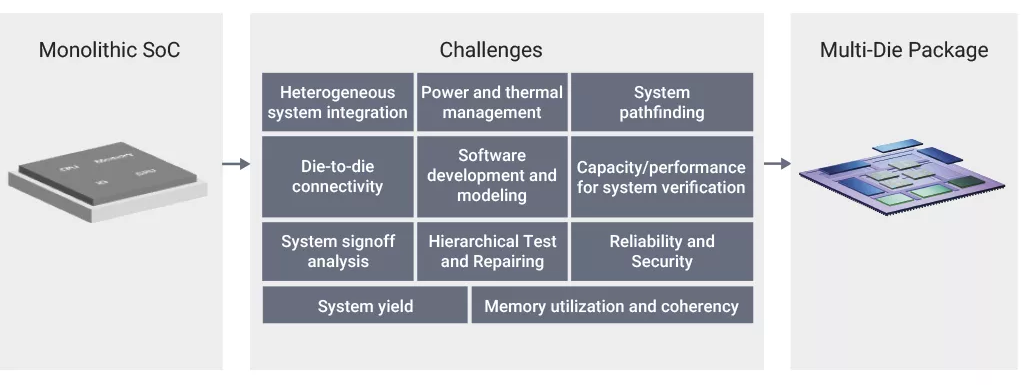

Multi-Die设计是一种在单个封装中集成多个异构或同构裸片的方法,虽然这种方法日益流行,有助于解决与芯片制造和良率相关的问题,但也带来了一系列亟待攻克的复杂性和变数。尤其是,开发者必须努力确保Multi-Die芯片在整个生命周期内的健康状况和可靠性。这不仅包括对各个裸片进行测试和分析,还包括对Die-to-Die连接性以及整个Multi-Die封装进行测试和分析。

利用新思科技Multi-Die解决方案加快创新速度

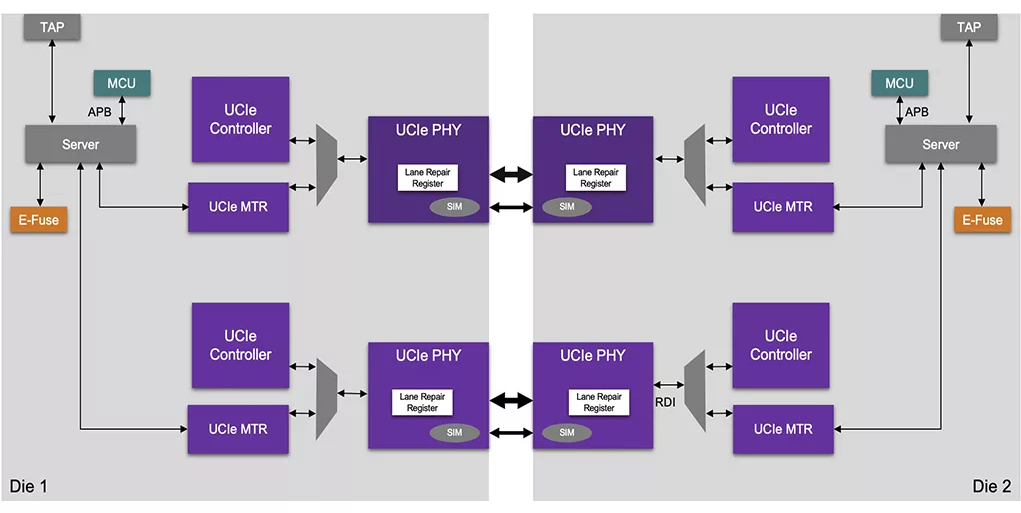

新思科技处于Multi-Die设计创新领域的前沿,我们最近与台积公司合作,演示了两个裸片之间通过高速UCIe(通用芯粒互连技术)规范进行通信。新思科技的监控、测试和修复(MTR) IP是此次演示的核心,展示了Multi-Die互连的制造和现场健康状况。

接下来,我们将探讨确保Multi-Die质量和可靠性所面临的独特挑战,深入了解为何全面的监控、测试和修复解决方案对芯片开发者至关重要,以及新思科技和台积公司正在采取哪些举措来提供助力。

互连监控、测试和修复的必要性

随着半导体变得更加复杂,即在单个封装中集成多个异构或同构裸片,裸片(也称为小芯片)之间有效通信和可靠互连的需求大幅增加。UCIe规范对Die-to-Die互连进行了标准化,促进了小芯片间的高速通信。然而,这些连接的高速特性要求对其进行严格的监控、测试和修复,以确保芯片在整个生命周期内实现无缝通信。监控信号完整性对于确保互连的整体健康状况至关重要。通过基于严格算法的测试,可以发现不同类型的开路、短路以及这些高数据速率通道附近可能出现的互连间串扰问题。同样重要的是,能够在工艺、电压和温度(PVT)范围内累积增强任何修复特征,以涵盖不同的用例。

为了实现UCIe Die-to-Die链路,开发者必须解决几个关键的Multi-Die健康挑战,包括:

窄间距:UCIe高级封装中的间距(即互连之间的距离)非常短(25-55um之间)。在芯片制造过程中,探测这些微凸块非常困难。这就需要一种嵌入式功能,能够进行自测而不是进行探测。

仅使用UCIe主带和边带:通常,除了主带和边带通道外,没有额外的可测性设计(DFT)端口可用于单个裸片级测试。

高速信号完整性:由于UCIe通信的高速特性,保持信号完整性变得极具挑战性。需要持续监测UCIe PHY参数,以便及时发现并纠正问题。

冗余与修复:为了提高质量、可靠性和良率,需要通过提供备用互连来实现冗余。出现故障时,备用互连可以替换有缺陷的互连,确保通信不间断。

环境变化性:互连在不同的环境条件(如温度和电压)下可能表现不同。需要对在多种条件下运行的互连进行测试和修复,以确保其鲁棒性。

Multi-Die健康状况监控和可靠性综合解决方案

我们的MTR IP解决方案由多个协同工作的组件组成,为Multi-Die设计提供全面的健康检查:

专用任务模式信号完整性监控:这由嵌入在UCIe高速互连通道内的信号完整性监控器(SIM)组成,用于持续监控信号完整性,实时反馈Die-to-Die通信通道的健康状况。

内置自测(BIST)算法:这些确定性算法旨在检测高级互连故障类型,包括因窄间距和高数据速率而可能出现的互连间串扰。

累积修复:高级UCIe提供冗余通道用于修复。每136个主通道配有12个额外的冗余通道,而在边带方面,4个主通道配有4个备用通道。这种冗余对于修复故障互连而不影响整体系统性能至关重要。借助这些冗余通道,MTR使用内置冗余分析(BIRA)算法进行硬修复,并将修复数据累积存储在E-Fuse中。

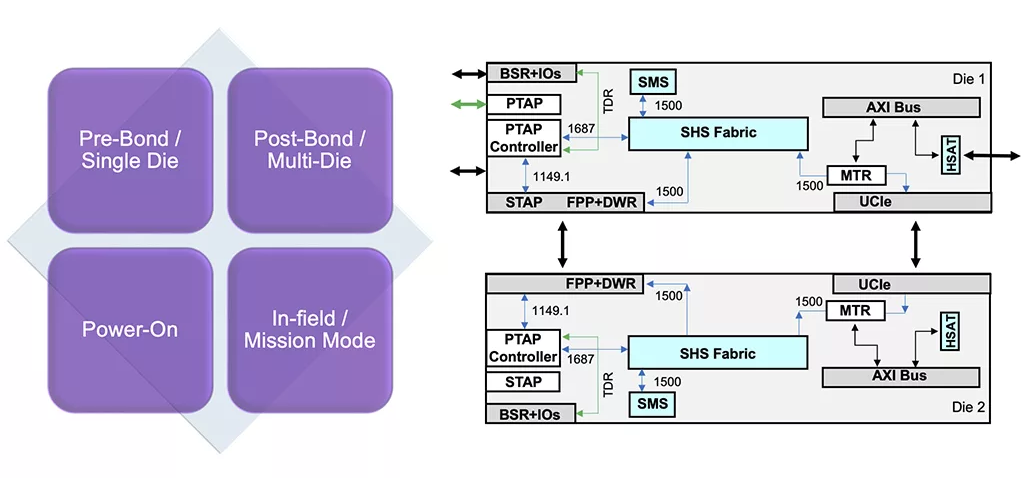

通过高速接口实现高速访问与测试(HSAT)以及自动测试向量生成(ATPG):HSAT功能有助于访问隐藏裸片,通过功能接口实现自适应高带宽测试。这不仅能够缩短测试时间,还能因引脚数和测试硬件的减少而降低成本,并支持在芯片的整个生命周期内进行测试。

我们的MTR IP解决方案可用于多种生命周期场景:在单个裸片层面,确保单个裸片的健康状况良好;在Multi-Die层面,这在制造堆叠芯片时尤为重要;在开机模式下,确保用户每次在实际使用中开启设备时,MTR都能发挥作用;以及在实时任务模式下,提供更深入的实时健康状况检查。前两种场景最适用于台积公司等代工厂,后两种场景则适用于代工厂的客户。

展示基于UCIe的Multi-Die进展

在小芯片峰会(Chiplet Summit)上,我们展示了采用台积公司工艺在CoWoS-S中介层上成功实现UCIe PHY IP一次性流片成功的最新成果。此外,我们还分享了一项演示结果,该演示展示了两个裸片通过高速UCIe Die-to-Die接口和标准GPIO接口进行通信的情况。

在第一种配置中,我们的MTR IP在两个新思科技UCIe IP之间提供互连可靠性、测试和修复功能。在第二种配置中,SLM MTR IP支持IEEE 1838测试访问基础结构,允许进行裸片内通道测试。

这两种配置都支持在每个裸片内部利用各种片上技术全面执行监控、测试、调试和修复功能,例如用于随机逻辑块的新思科技HSAT和SEQ IP、用于嵌入式存储器块的SMS IP,以及用于UCIe块的SHS和MTR IP。这些功能覆盖了键合前和键合后的制造阶段、实际应用中的开机阶段以及定期的任务健康监控。该设计展示了如何在Multi-Die封装的整个芯片生命周期内使用上述功能,而不会在堆叠裸片时造成覆盖率损失或向量膨胀。

我们对Multi-Die健康状况与可靠性的承诺

新思科技致力于帮助客户突破半导体技术的界限,并提供在整个芯片生命周期内具有超高制造良率和鲁棒性的Multi-Die设计。我们针对基于UCIe的Multi-Die设计提供的SLM MTR IP解决方案就是这一承诺的最好证明,它为监控、测试和修复Die-to-Die互连提供了一个鲁棒的框架。该解决方案可用于芯片生命周期的各个阶段,包括设计、试制到生产和现场阶段。

-

芯片

+关注

关注

459文章

51738浏览量

431063 -

封装

+关注

关注

128文章

8208浏览量

144060 -

新思科技

+关注

关注

5文章

834浏览量

50707

原文标题:新思科技+台积公司,助力Multi-Die设计全流程健康状况和可靠性

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

西门子Tessent Multi-die解决方案实现2.5D/3D IC可测性设计自动化

西门子推出Tessent Multi-die软件解决方案 满足多维设计的需求

2023是否会成为Multi-Die的腾飞之年?

光子芯片公司如何轻松搞定复杂Multi-Die设计?

芯片革命:Multi-Die系统引领电子设计进阶之路

设计更简单,运行更稳健,UCIe标准如何“拿捏”Multi-Die系统?

如何成功实现Multi-Die系统的方法学和技术

VCS:助力英伟达开启Multi-Die系统仿真二倍速

Multi-Die系统,掀起新一轮技术革命!

Multi-Die系统验证很难吗?Multi-Die系统验证的三大挑战

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

新思科技Multi-Die系统如何满足现代计算需求

利用Multi-Die设计的AI数据中心芯片对40G UCIe IP的需求

利用新思科技Multi-Die解决方案加快创新速度

利用新思科技Multi-Die解决方案加快创新速度

评论