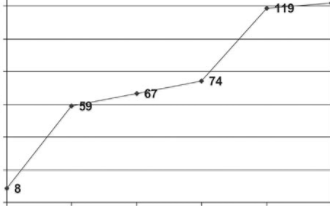

相信每一个电子工程师在项目开发的过程中都不可避免的要进行方案的调试,除了模拟调试我们还必须进行真机调试才能确保功能的正常,通常我们采用的调试方法分为两种:第一种是使用硬件逻辑分析仪,第二种是采用嵌入逻辑分析IP,通过JTAG连接开发IDE进行调试,但是随着FPGA设计越来越复杂,速度越来越快,这两种方案显得越来越捉襟见肘,逻辑分析仪会占用太多的FPGA I/O接口,嵌入式逻辑分析IP又会消耗宝贵的FPGA逻辑资源,因此Exostiv Labs公司推出了新型的调试工具EXOSTIV Probe。

图1:传统FPGA调试方案:硬件逻辑分析仪和嵌入式逻辑分析IP

EXOSTIV Probe从各方面都优于传统方案,它支持Xilinx All Programmable所有系列,采用高速SerDes接口实现数据采集和通信,EXOSTIV Probe能够采集多达32768个内部信号节点,此外EXOSTIV IP提供动态多路复用控制功能,能够动态采集更多的数据集而不需要重新进行编译。

图2:EXOSTIV Probe硬件调试仪

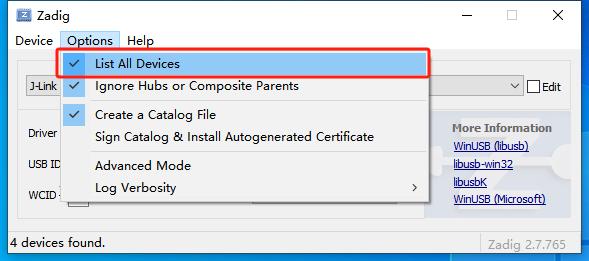

EXOSTIV Probe提供8GB的存储空间用于存储从FPGA中采集到的数据,高速USB 3.0接口用于实现EXOSTIV应用上位机与EXOSTIV之间的通信,集成了四个SFP/SFP+收发器接口,每个接口速度可达6.6Gbps。此外上位机EXOSTIV Dashboard由Core Inserter和Analyzer两大功能组件组成,Core Inserter可以动态配置EXOSTIV IP,Analyzer则实现采集数据的管理、显示分析并且导出,MYRIAD波形显示插件支持TB级波形数据的显示。

EXOSTIV Pobe结合Xilinx Virtex UltraScale VCU108开发板卡调我们看到现在很多新兴行业,比如云计算、5G通信、人工智能(AI)、机器学习、自动驾驶等应用场景都需要强大的计算能力来支持,因此FPGA的应用越来越多,这些设计不仅复杂,占用更多的逻辑资源,同时信号速度也呈现指数级别的增加,EXOSTIV Probe的出现提供了更强大的信号可视化能力,毫无疑问的方便了电子工程师们的调试工作,更快的将FPGA设计方案交付。

-

FPGA

+关注

关注

1664文章

22508浏览量

639479 -

逻辑分析仪

+关注

关注

3文章

220浏览量

24571

原文标题:高速FPGA设计方案调试利器:EXOSTIV Probe

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

简化Xilinx和Altera FPGA调试过程

实用FPGA的调试工具—ChipScope Pro

FPGA硬件电路的调试必备原则和技巧

FPGA设计的创新调试手段

采用内部或者嵌入式逻辑分析仪推动FPGA调试技术改变

传统FPGA调试方案与EXOSTIV Probe硬件调试仪

传统FPGA调试方案与EXOSTIV Probe硬件调试仪

评论