我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。作者ALIFPGA,多年FPGA开发经验,所有文章皆为多年学习和工作经验之总结。

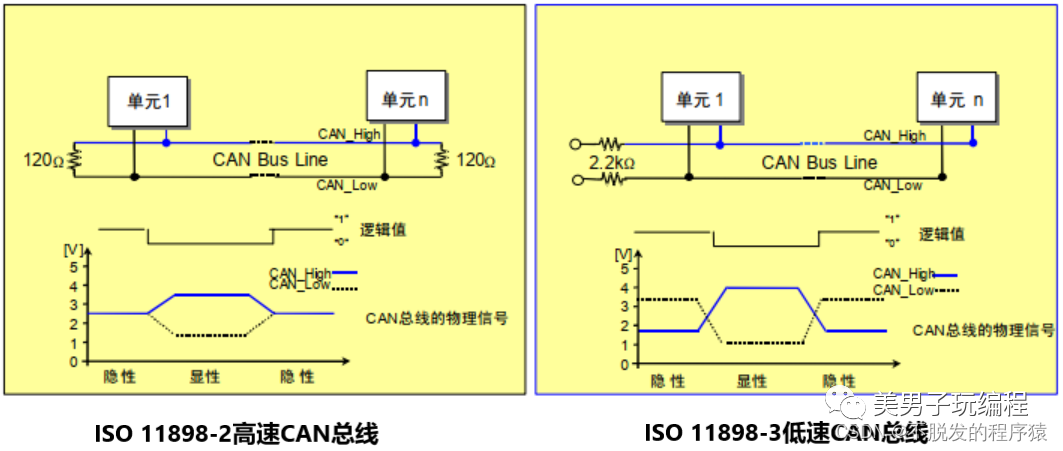

CAN总线是一种串行数据通信协议,其通信接口中集成了CAN协议的物理层和数据链路层功能,可完成对通信数据的成帧处理,包括位填充、数据块编码、循环冗余检验、优先级判别等项工作。

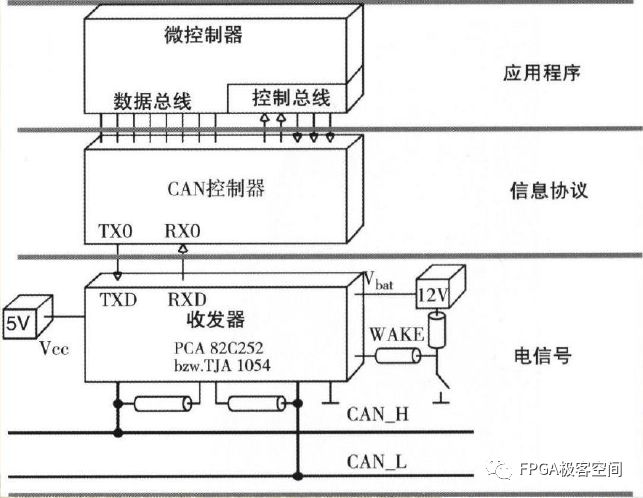

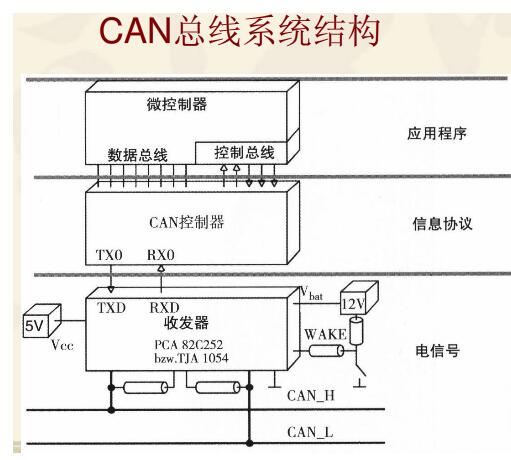

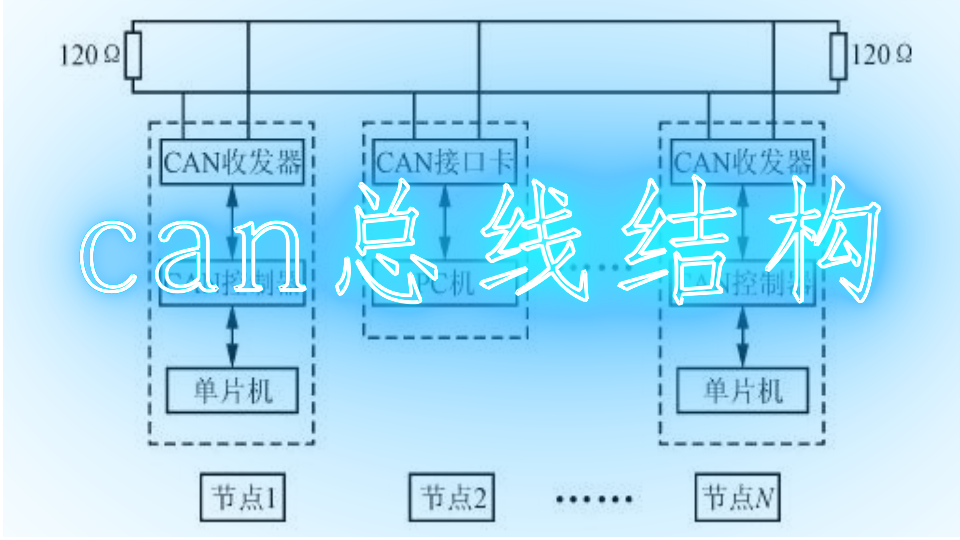

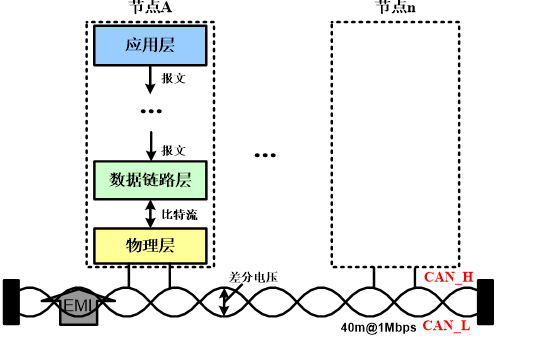

CAN总线结构

CAN总线规范采用了ISO-OSI(Open System Interconnection Reference Model,开放式通信系统互联参考模型)的三层网络结构,有三种不同的器件与之相对应。

对应物理层的是收发器;

对应数据链路层的是CAN控制器;

应用层上主要是用户特殊的应用,对应的器件是微控制器。

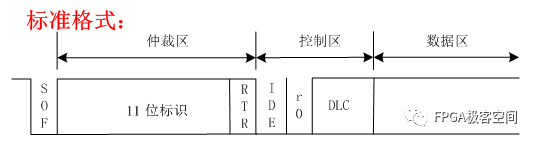

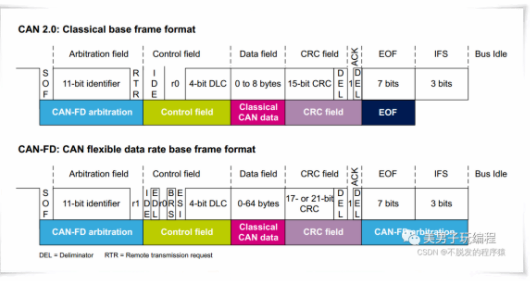

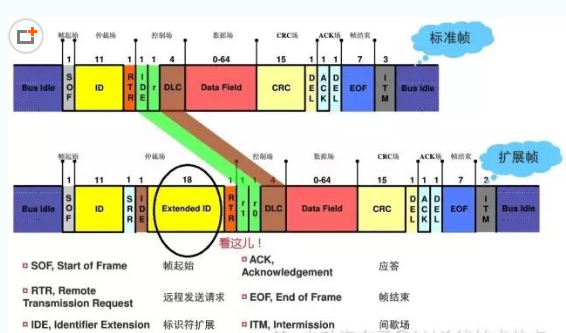

CAN总线标准帧

标准帧11位标识符。

帧类型数据帧、远程帧、错误帧和过载帧

数据帧:数据帧携带数据从发送器至接收器。总线上传输的大多是这个帧。

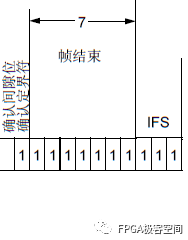

远程帧:由总线单元发出,请求发送具有同一识别符的数据帧。数据帧(或远程帧)通过帧间空间与其他各帧分开。

错误帧:任何单元一但检测到总线错误就发出错误帧。

过载帧:过载帧用以在先行的和后续的数据帧(或远程帧)之间提供一附加的延时。

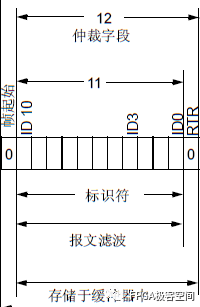

帧以起始帧(SOF)位开始, SOF 为显性状态,允许所有节点的硬同步。SOF之后是仲裁字段,由12个位组成,分别为11个标识位和一个远程发送请求(Remote TransmissionRequest, RTR)位。RTR 位用于区分报文是数据帧

(RTR 位为显性状态)还是远程帧(RTR 位为隐性状态)。

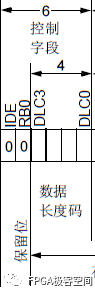

仲裁字段之后是控制字段,由6 个位组成。控制字段的第一位为标识扩展(Identifier Extension,IDE)位,该位应是显性状态来指定标准帧。标识扩展位的下一位为零保留位(RB0),CAN 协议将其定义为显性位。控制

字段的其余4 位为数据长度码(Data Length Code,DLC),用来指定报文中包含的数据字节数(0 到8 字节)。

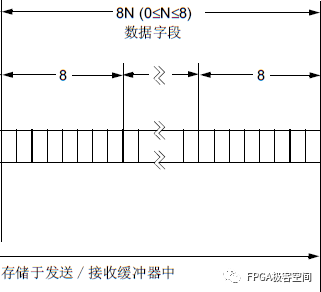

控制字段之后为数据字段,包含要发送的任何数据字节。数据字段长度由上述DLC 定义(0 到8 字节)。

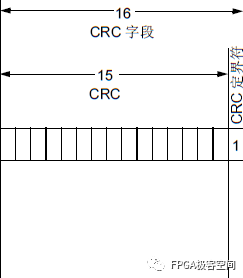

数据字段之后为循环冗余校验(CRC)字段,用来检测报文传输错误。CRC 字段包含一个15 位的CRC 序列,之后是隐性的CRC 定界位。

最后一个字段是确认字段(ACK),由2 个位组成。在确认时隙(ACK Slot)位执行期间,发送节点发出一个隐性位。任何收到无错误帧的节点会发回一个显性位(无论该节点是否配置为接受该报文与否)来确认帧收到无误。确认字段以隐性确认定界符结束,该定界符可能不允许被改写为显性位。

-

FPGA

+关注

关注

1664文章

22508浏览量

639450 -

CAN总线

+关注

关注

146文章

2050浏览量

135513

原文标题:CAN总线标准帧

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高速CAN总线和低速CAN总线的特性

can总线结构和原理

CAN总线过载帧及数据帧详解

虹科干货 | 带你全面认识“CAN总线错误”(一)——CAN总线错误与错误帧

CAN总线结构与CAN总线标准帧

CAN总线结构与CAN总线标准帧

评论