为了提高串行数据传输的可靠性,现在很多更高速率的数字接口采用的是对数据进行编码后再做并串转换的方式。编码的方式有很多,如8b/9b编码、8b/10b编码、64b/66b编码、128b/130b编码等,下面我们以最流行的ANSI 8b/10b编码为例进行一下介绍。

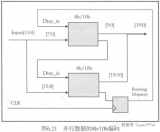

在ANSI 8b/10b编码方式中,8比特的数据先通过相应的编码规则转换成10比特的数据,然后再进行并串转换;接收端收到信号后先把串行数据进行串并转换得到10比特的数据,然后再通过10比特到8比特的解码得到原始传输的8比特数据。因此,如果发送端并行侧的数据速率是8bit*100Mb/s,通过8b/10b编码和并串转换后的串行侧的数据速率就是1bit*1Gb/s。8b/10b编码方法最早由IBM发明,后来成为ANSI标准的一部分(ANSI X3.230-1994, clause 11),并在通信和计算机总线上广泛应用。

数据经过8b/10b编码后有几个最大的好处:

有足够多的跳变沿,可以从数据里进行时钟恢复。正常传输的数据里可能会有比较长的连续的0或者连续的1,而进行完8b/10b编码后,其编码规则保证了编码后的数据流里不会出现超过5个的连续的0或1,信号里会出现足够多的跳变沿,因此可以采样嵌入式的时钟方式,即接收端可以从数据流里用PLL电路直接恢复时钟,不需要专门的时钟传输通道。

直流平衡,可以采用AC耦合方式。经过编码后数据里不会出现连续的0或者1了,但是还是有可能在某个时间段内0或者1的数量偏多一些。从上面的编码表中我们可以看到同一个Byte对应有正、负两组10bit的编码,一个编码里1的数量多一些,另一个编码里0的数量多一些。数据在对当前的Byte进行8b/10b编码传输时,会根据前面历史传输的数据中正负bit的数量来选择使用哪一组编码,从而可以保证总线上正负bit的数量在任何时刻基本都是平衡的,也就是直流点不会发生大的变化。直流点平衡以后,在信号传输的路径上我们就可以采用AC耦合方式(最常用的方法是在发送端或接收端串接隔直电容),这样信号对于收发端的地电平变化和共模噪声的抵抗能力进一步增强,可以传输更远的距离。采用AC耦合方式的另一个好处是收发端在做互连时不用太考虑直流偏置点的互相影响,互连变得非常简单,对于热插拔的支持能力也更好。

有利于信号校验。很多高速信号在做传输时为了保证传输的可靠性要对接收到的信号进行检查以确认收到的信号是否正确。在8b/10bit编码表里,原始的8bit数据总共有256个组合,即使考虑到每个Byte有正负两个10bit编码也只需要用到512个10bit的组合。而10bit的数据总共可以有1024个组合,因此有大约一半的10bit组合是无效的数据,接收端一旦收到这样的无效组合就可以判决数据无效。另外,前面我们介绍过数据在传输过程中是要保证直流平衡的,一旦接收端收到的数据中发现违反直流平衡的规则,也可以判决数据无效。因此采用8b/10b编码以后数据本身就可以提供一定的信号校验功能。不过需要注意的是,这种校验不是足够可靠,因为理论上还是可能存在有几个bit在传输中发生了错误但是结果仍然符合8b/10b编码和规则和直流平衡原则。因此,很多使用8b/10b编码的总线都还会在上层协议上再做相应的CRC校验(循环冗余校验)。

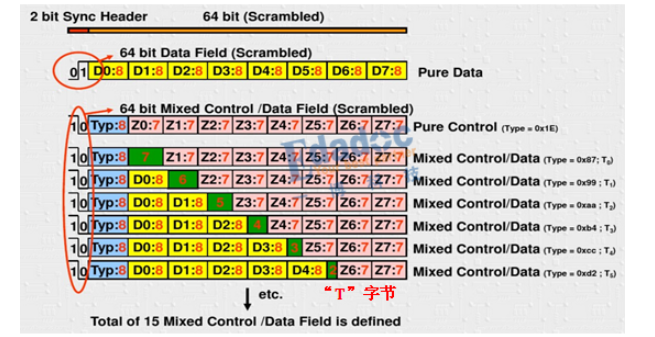

可以插入控制字符。在10bit数据可以表示的1024个组合中,除了512个组合用于对应原始的8bit数据以及一些不太好的组合(比如0b1100000000这样信号里有太长的连续0或者1而且明显0、1的数量不平衡)以外,还有一些很特殊的组合。这些特殊的组合可以用来在数据传输过程中做为控制字符插入。这些控制字符不对应特定的8bit数据,但是在有些总线应用里可以代表一些特殊的含义。比如K28.5码型,其特殊的码型组合可以帮助接收端更容易判别接收到的连续的10bit数据流的符号边界,所以在一些总线的初始化阶段或数据包的包头都会进行发送。还有一些特殊的符号用于进行链路训练、标记不同的数据包类型、进行收发端的时钟速率匹配等。

综上所述,要把并行的信号通过串行总线传输,一般需要对数据进行并串转换。为了进一步减少传输线的数量和提高传输距离,很多高速数据总线采用嵌入式时钟和8b/10b的数据编码方式。8b/10b编码由于直流平衡、支持AC耦合、可嵌入时钟信息、抗共模干扰能力强、编解码结构相对简单等优点,在很多高速的数字总线如FiberChannel、PCI-E、SATA、USB3.0、DisplayPort、XAUI、RapidIO等接口上得到广泛应用。

-

编码

+关注

关注

6文章

962浏览量

55055 -

串行总线

+关注

关注

1文章

183浏览量

30772

原文标题:串行总线的8b/10b编码

文章出处:【微信号:gh_bee81f890fc1,微信公众号:面包板社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

8b10b编码verilog实现

Aurora 8b/10b IP核问题

收发器向导中启用8b/10b编码器的方法是什么?

如何使用Aurora 8B / 10B建立仅传输?

怎么禁用Aurora IP Core 8B / 10B中的时钟补偿功能?

基于FPGA的8B/10B编解码设计

基于PRBS的8B/10B编码器误码率为0设计

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议分析

串行总线的8b/10b编码

串行总线的8b/10b编码

评论