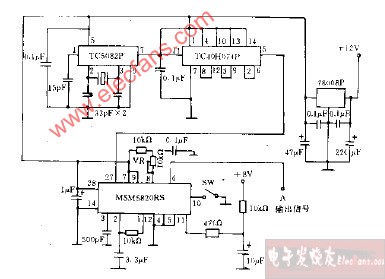

下图所示的是用Q2230激励锁相倍频系统实现的一个实际的频率合成器。系统时钟采用40 MHz,这样能输出DC~15 MHz、分辨率为0.01 Hz、电压峰一峰值为10 V的正弦波。谱纯度优于一70 dB,能输出DC~60 MHz的TTL信号,具有AM、FM、FSK、DPSK调制功能。

1. 40 MHz高稳定基准时钟

为了合成器输出信号的高质量,40 MHz时钟是用一个高稳定度5 MHz(优于l0-9/s)的恒温晶体振荡器,通过8倍频PLL系统获得的。其中PLL的VCO采用40 MHz晶体振荡器,以保证系统时钟有足够高的频谱纯度和频率稳定度。

2.微处理器控制系统

以8031为核心构成的微处理器控制系统包含键盘显示单元、串行通信口和CPU单元,实现调制控制电路(FM、FSK、DPSK)、幅度控制DAC、直流偏置、电平比较、输出切换诸电路以及面板功能和显示控制功能。

3.TTL比较器

TTL比较器A完成DC~15 MHz TTL电平输出。TTL比较器B获得的TTL电平反馈到CPU单元与电平比较DAC,得到正弦输出幅度的标准功能。

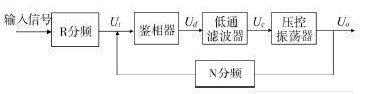

4. 15~60 MHz PLL系统

15~60 MHz是一个4倍频锁相系统,通过切换控制,在TTL输出口可获得DC~60 MHz的TTL信号。

-

频率合成器

+关注

关注

5文章

222浏览量

32437 -

Q2230

+关注

关注

0文章

2浏览量

2302

发布评论请先 登录

相关推荐

详解频率合成器高性能架构的实现

基于DDS的频率合成器设计介绍

如何利用FPGA设计PLL频率合成器?

DDS PLL短波频率合成器设计

ADI发布新款PLL合成器,用于实现高性价比FMCW雷达系统

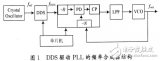

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

基于FPGA与PLL频率合成技术设计的整数/半整数频率合成器

Q2230+PLL实现的频率合成器

Q2230+PLL实现的频率合成器

评论