在现代电子测量、雷达、通信系统、电子对抗等技术领域中,具有频率范围宽,分辨率高,转换快速的多种模式的信号源是重要和必不可少的。20世纪70~80年代大都采用锁相频率合成技术,实现频率范围为DC(MHz)~几十GHz,分辨率达到MHz的信号源。虽然转换速度不高(几十μs到ms量级),但已广泛应用到现代电子系统中;与此同时,各种规格的锁相频率合成技术的信号源产品也投入到国际市场。

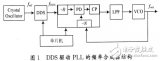

随着电子技术和集成电路的飞速发展,进入20世纪90年代后,出现了频率分辨率高(MHz量级),频率转换快(μs到ns量级)的DDS大规模芯片,输出信号的频率上限基本止在HF或VHF频段内,比PLL合成技术以及直接模拟合成技术所得到的信号频率低。当要求得到既有高的频率分辨率,又有较快的转换速度和较低噪声的超高频(UHF),甚至微波信号时,DDS+PLL技术就显示出了强大的生命力。

一、Q2230的基本结构及实现的频率合成器

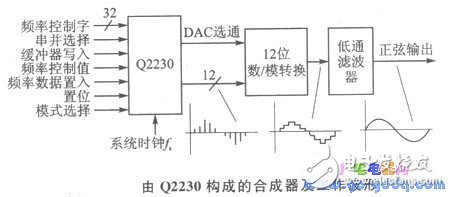

Q2230是QUALCOMM公司生产的一种单片单通道85 MHz的DDS器件。它有串并行控制接口,采用85 MHz的时钟,可以合成出DC~34 MHz,具有20 MHz分辨率的信号频率范围。它的基本组成框图如图1所示。

它由频率控制缓冲器、频率控制寄存器、相位累加器、相位累加寄存器、正弦检索表5个部分组成,设有串并行输入控制的频率控制寄存器、32位的高速相位寄存器及输出12位的正弦量。

频率控制缓冲器 将输入代表频率的数码暂存起来。

频率控制寄存器 在写入脉冲的作用下,将缓冲器中的代表频率的二进制码写入该寄存器。

相位累加器 根据寄存器的代表频率的字,对系统时钟的相位进行抽样。

图2示出了相位步长△ψ与输出频率的关系。

正弦检索表将相应累加器输出的离散数字变换为相应的正弦波形离散幅度数字,再经外接的D/A转换器和低通滤波器就可获得正弦信号。

图3示出了用Q2230组成的频率合成器及工作波形。

1.频率控制值的计算

根据DDS调谐方程

当fs为40 MHz,输出频率为12.5 MHz时,可以按上式计算出频率控制值的相位步长字,以便控制频率变化。

因此通过改变写入到频率控制寄存器的频率字△ψ的大小,可达到精确改变输出频率的目的。

2.频率分辨率的计算设频率分辨率fr为

当fs=40 MHz时

3.最低频率和最高频率的计算

芯片中相位累加器的步长M-32,当相位累加器的相位取样步长M-1时,参考时钟相位的取样点数达到最大值为△ψ=1,此时DDS输出的频率fo为最低,即fomin=fs/232。40 MHz时,fomin=0. 01 Hz。当相位字长Aψ=232时,输出频率fomax=AφXfs/232。根据取样定理,输出信号基波最高频率应低于所用参考时钟频率的一半,fomax=20 MHz,实际中只能用到fs的40%,即16 MHz。

-

DDS

+关注

关注

22文章

688浏览量

156873 -

Q2230

+关注

关注

0文章

2浏览量

2369

发布评论请先 登录

关于DDS+PLL雷达发射源芯片选型问题请教

DDS PLL短波频率合成器设计

采用DDS+PLL技术实现的L波段频率合成器

DDS+PLL高性能频率合成器的设计方案

基于DDS+PLL在电台设计中的应用

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

DDS+PLL频率合成技术与应用

DDS+PLL频率合成技术与应用

评论