MY-I.MX6系列核心板,只需要一个5V电源(持续供电电流不低于2A,峰值2.5A-3A)输入即可。详见下图。

MY-I.MX6seriesofcoreboardonlyneeds5Vpowersource(constantcurrentisnotsmallthan2A,peakvalue2.5A-3A)asaninput。detailsasbelow。

如果是直接的5V输入,5V的电源一定要做过压保护,过压保护电路参考如下。

ifitisadirect5Vinput,5Vpowersourceneedaovervoltageprotection,theprotectioncircuitcanbedesignedwithfollowingreference。

如果是高电压输入通过DCDC转换成5V,核心板会输出一个3P3V的电源,此电源的电流不超过500mA。如果底板上面3.3V的电流非常小,可以直接采用此3P3V作为底板的供电电源,如果用3P3V作为底板供电电源,请在3P3V电源上串上500mA的保险丝。

ifitishighvoltageinputtobeconvertedto5VthroughDCDCprinciple,thecoreboardwilloutput3P3Vpowersourcewithamaximumcurrent500mAofwhichcanbeusedaspowersupplyforbaseboardifcurrentwith3.3Vonthebaseboardistoosmall,inthiscase,pleaseputinserialafuseforthis3P3Vpowersource。

由于底板上面的3.3V电压通常会超过500mA,一般用户会单独通过DCDC或者LDO产生3.3V。

sincecurrentwith3.3Vonthebaseboardisusuallyover500mA,normallyuserswillgenerateaanother3.3VthroughDCDCorLDO。

注意:底板的3.3V的电源,一定要通过核心板的3P3V来做使能控制,而不能够直接由底板上面的其他电源产生。如果底板上面还有其他电源,也必须有3P3V来做使能控制。此点是由于I.MX6芯片决定的。

note:enablecontrolmustbedonefor3.3Vonbaseboardby3P3Voncoreboardinsteadofbeingconductedbyotherpowersourcesonthebaseboard.ifthereareotherpowersourcesonbaseboard,theirenablecontrolsmustbeconductedby3P3Vaswell,thisisuptothenatureofI.MX6chip。

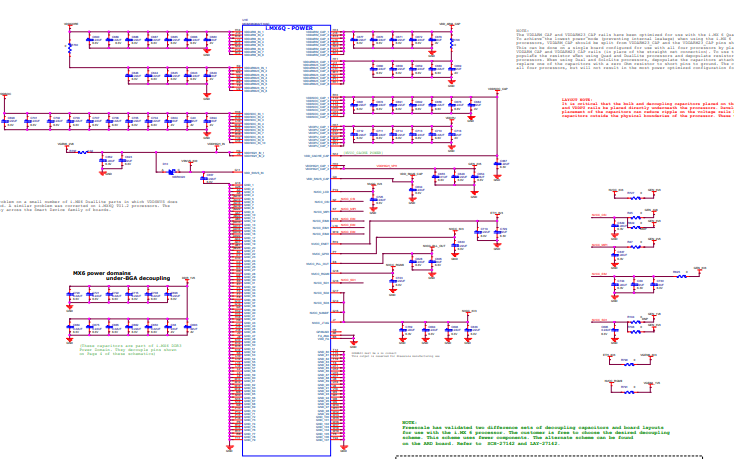

参考电路如下:

referencecircuitasbelow:

核心板5V电源输入处要放置大的储能电容,确保CPU在瞬间增加负载的时候不至于断电。如果有过孔,确保过孔的电流至少能够通过3A的峰值电流,可以多打一些过孔增加电流。

capacitorwithbigcapacityshouldbeplacednear5Vinputoncoreboard,toensurecontituouspowersupplyevenwhensuddenextraloadisaddedforCPU。ifthereisviahole,needtomakesureviaholecangothrough3Apeakcurrent,moreviaholescanbebuilttoincreasecurrent。

串口设计(serialportdesign)原理(principle)

串口设计上面,经常会碰到的问题是RXD跟TXD的方向接反。参考原理图中的网标表示如下

forserialportdesign,commonquestionsarisingareinversionbetweenRXDandTXD。networkstandardintheschematicasbelow

TXD——CPU输出

TXD——CPUoutput

RXD——CPU输入

RXD——CPUinput

PCB

注意:在设计底板的时候,我司提供了底板的原理图和PCB图,串口我司采用的是母头的接口。务必确保用户在设计的时候也使用的是母头,如果要更换成公头。RS232信号要更换。公头母头的详细信息请上网查询

note:wecanprovideschematicandPCBdiagramfordesignofbaseboard,ourserialportisfemaleheadasconnector.pleaseassureyourdesigntobeconsistentwithouroffer,ifchangeserialporttobemaleheadconnector,thenRS232siganlconnectorheadneedtobechangedaccordingly.Forthedetailsofmaleandfemaleheadconnector,pleasegetoninternetforconsuls.

SD卡设计(SDcarddesign)原理(principle)

用户在设计SD卡的时候,针对IO的上下拉,请严格参考原理图,过多的上下拉可能会导致SD卡不能够正常的工作。参考图见下面

forusers‘designofSDcard,pleasefollowstrictlyschematictoarrangeIOdropdown,excessivedropdownwillenableSDcardnottoworknormally。referencediagramasbelow

注意:如果用户不需要SD卡,要换成TF卡,由于TF卡是没有写保护这个功能的。写保护信号(SD3_RST/SD3_WP)要下拉,而不能够直接悬空。如果TF卡选用的是热插拔卡座,一定要清楚TF卡的检测管脚是哪个。一般情况是插卡之后,检测管脚接地,此时插入检测管脚(KEY_COL/SD3_CD_B)要上拉。如果TF卡选择的是翻盖式非可插拔卡座。写保护信号上拉,同时插入检测信号要接地(相当于始终插入了卡)

note:ifusersdon’tneedSDcard,butneedTFcard,sinceTFcarddoesn‘thavefunctionofwrite-protect.Write-protectsignal(SD3_RST/SD3_WP)needtopulldown,whichcan’tbehangeddirecltyintheair.IfTFcardboothisdesignedwithhotswap,mustmakeclearwhichpinofTFcardisfordectetion。normallywheninsertthecard,detectionpinwillbegrounded,theinserteddetectionpinKEY_COL/SD3_CD_B)needtopullup.IfTFcardboothisdesignedwithfliptype,write-protectneedtopullup,atthesametimetheinserteddetectionsignalneedtobegrounded(justasacardiskeptinthebooth)

如果要增加ESD保护。确保接在SD_CLK信号上的ESD的电容值很小。

ifneedadditionalESDprotect,pleaseensureasmallcapacityvalueonSD_CLKsignal。

PCB

SD0,SD1,SD2,SD3,CMD,CLK信号要做等长处理。ESD原件要跟SD卡座非常接近。

SD0,SD1,SD2,SD3,CMD,CLKsignalneedanequaltreatment。ESDoriginalsneedtobeveryclosetoSDcardbooth。

SATA设计(SATAdesign)原理(principle)

SATA的原理相对简单,确保方向正确。由于一般SATA盘的电流比较大,5V输入电流要不低于3A为好。

SATAprincipleissimplebycontrast,onlyneedtoensureacorrectdirection.sincecurrentonSATAisnormallyalittlebig,5Vcurrentinputedisbetternottobeaslowas3A。

PCB

SATA信号上面串联的4个电容要紧挨SATA座。

thefourcapacitorswhichareserialedtoSATAsignalshouldbeclosetoSATAbooth。

100欧姆的差分阻抗匹配

100ohmdifferenceresistancematchingup

每组差分对之间的长度误差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

要求完整参考地平面

requireafullreferencetogroundlevel

HDMI原理(principle)

HDMI座子不能够接错定义

HDMIstandcan‘tbelinkedwithwrongdefinition

PCB

100欧姆差分阻抗匹配。

100ohmdifferenceresistancematchingup。

每组差分对之间的长度误差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

要求完整参考地平面

requireafullreferencetogroundlevel

保护器件CM2020一定不要省略。

protectcomponentCM2020can’tbeignored。

LVDS原理(principle)

LVDS信号如果传输距离比较远,接的屏幕比较大,LVDS信号上面可以串联耦合磁珠,能够保证传输的质量更好。

iftransmittingdistanceforLVDSsignalislong,andscreenlinkedwithisbig接的屏幕比较大,amagneticcouplingcanbeputinserialonLVDSsignalforabettertransmitingquality。

PCB

100欧姆的差分阻抗匹配。

100ohmdifferenceresistancematchingup。

每组差分对之间的长度误差控制在±5mil

lengthtoleranceforeachgroupofdifferencespairsiscontrolledwithin±5mil

如果用双路LVDS信号做1080p的显示。LVDS0跟LVDS1的信号要做等长处理。

iftwowayLVDSsinglaisusedfor1080pdispla,。LVDS0andLVDS1signalneedanequaltreatment。

要求完整参考地平面

requireafullreferencetogroundlevel

RGB接口LCD(RGBportLCD)原理(principle)

RGB接口的LCD满足24bit,18bit的接口模式

LCDasRGBportneedtobematchedupwithinterfacemodelwith24bit,18bit

CPU信号(注1)

(CPUsignal(note1))24bit(注2)

(24bit(note2))18bit(注3)

(18bit(note3))18bit(注4)

(18bit(note4))

D0B0B0

D1B1B1

D2B2B0B2

D3B3B1B3

D4B4B2B4

D5B5B3B5

D6B6B4G0

D7B7B5G1

D8G0G2

D9G1G3

D10G2G0G4

D11G3G1G5

D12G4G2R0

D13G5G3R1

D14G6G4R2

D15G7G5R3

D16R0R4

D17R1R5

D18R2R0

D19R3R1

D20R4R2

D21R5R3

D22R6R4

D23R7R5

注1(note1)。

D0表示CPU的液晶接口最低位,

D0indicateaminimallevelforCPUliquidcrystalport,

D23表示CPU的液晶接口最高位

D23indicateamaximallevelforCPUliquidcrystalport

注2(note2)

B0-24位液晶蓝色位最低位,

B0-24bitbluebitofliquidcrystalatminimallevel,

B7-24位液晶蓝色位最高位

B7-24bitbluebitofliquidcrystalatmaximallevel,

G0-24位液晶绿色位最低位,

G0-24bitgreenbitofliquidcrystalatminimallevel,

G7-24位液晶绿色位最高位

G7-24bitgreenbitofliquidcrystalatmaximallevel

R0-24位液晶红色位最低位,

R0-24bitredbitofliquidcrystalatminimallevel,

R7-24位液晶红色位最高位

R7-24bitredbitofliquidcrystalatmaximallevel

注3(note3)。

采用此接法,LCD软件还是选用24bit模式

inuseofthiskindoflink,LCDsoftwarestillchoose24bitmodel

B0-18位液晶蓝色位最低位,

B0-18bitbluebitofliquidcrystalatminimallevel,

B5-18位液晶蓝色位最高位

B5-18bitbluebitofliquidcrystalatmaximallevel

G0-18位液晶绿色位最低位,

G0-18bitgreenbitofliquidcrystalatminimallevel,

G5-18位液晶绿色位最高位

G5-18bitgreenbitofliquidcrystalatmaximallevel

R0-18位液晶红色位最低位,

R0-18bitredbitofliquidcrystalatminimallevel,

R5-18位液晶红色位最高位

R5-18bitredbitofliquidcrystalatmaximallevel

注4(note4)。

采用此接法,LCD软件要改成选用18bit模式

ifinuseofthislinkmethod,LCDsoftwareneedtochoose18bitmodel

B0-18位液晶蓝色位最低位,

B0-18bitbluebitofliquidcrystalatminimallevel,

B5-18位液晶蓝色位最高位

B5-18bitbluebitofliquidcrystalatmaximallevel

G0-18位液晶绿色位最低位,

G0-18bitgreenbitofliquidcrystalatminimallevel,

G5-18位液晶绿色位最高位

G5-18bitgreenbitofliquidcrystalatmaximallevel

R0-18位液晶红色位最低位,

R0-18bitredbitofliquidcrystalatminimallevel,

R5-18位液晶红色位最高位

R5-18bitredbitofliquidcrystalatmaximallevel

如果静电要求非常严格,LCD信号上面要做ESD防护。

ifthereisastrictrequestwithstatic,needESDprotectforLCDsignal。

PCB

所有的数据线,CLK信号要做等长处理

foralldatalines,needanequaltreatmentforCLKsignal

要求完整参考地平面

requestafullreferencetogroundlevel

CMOS原理(principle)

PCB

MCLK和PIXCLK信号频率非常高,Layout时要做地隔离处理

sincefrequencyofMCLKandPIXCLKsignalisveryhigh,needisolationtreatmentwhenLayout

数据,clk信号要做等长处理。

data,needanequaltreatmentforclksignal。

要求完整参考地平面

requestafullreferencetogroundlevel

USB原理(principle)

USBHOST通过LAN9514扩展了4和USBHOST,同时扩展了1路10M/100M的以太网接口。

USBHOSTexpandedwith4andUSBHOSTviaLAN9514,andexpandedwithoneway10M/100Methernetinterface。

USB线上串耦合电感。

acouplinginductanceisputinserialonUSBline。

核心板的USB_H1_VBUS信号要通过磁珠接5V电源。

核心板的USB_H1_VBUSsignalofcoureboardneedtobeconnectedwith5Vpowersupplythroughmagneticbead。

对外做HOST供电时,要采用USB过流保护器件。

ifpowersupplyHostoutoftheboard,pleaseincludeover-currentprotectcomponentforUSD。

目前的MINIUSB口硬件设计上只能够做device口,如果要做HOST功能,请参考FSL官方的OTG设计即可。

sofaronlydeviceportcanbedoneinlayoutofhardwareforMINIUSBport,ifneedfunctionofHOST,pleaserefertoOTGlayoutfromFSLofficial。

PCB

90欧姆的差分阻抗匹配

90ohmdifferenceresistancematchingup

要求完整参考地平面

requestafullreferencetogroundlevel

对外供电的电流足够大。

currenttosupplyoutsideneedtobebigenough。

CAN原理(principle)

由于CAN的TX,RX信号是3.3V电平,注意电平转换。

sinceCAN的TX,RXsignalis3.3Velectricallevel,attentiontoconversionofelectricallevel。

PCB

CANH,CANL查分信号。

CANH,CANLchecksignal。

PCIE原理(principle)

TX,RX信号要串联0.1uF电容(外接模块上面如果RX信号已经串联了电容,不需要再次串联)

TX,RXsignalneedtoconnectinserialwith0.1uFcapacitor(ifanexternalmoduleisalreadywithacapacitorinserial,thennoneedtoconnectacapacitoragain)

CLK信号上串联0.1uF电容,同时在电容后端并联一个49.9欧姆的对地电阻。

CLKsignalconnectinserialwith0.1uFcapacitor,atthesametimeputa49.8resistortogroundinparallelwithanotherendofthecapacitor。

PCB

85欧姆的差分阻抗匹配

85ohmdifferenceresistancematchingup

要求完整参考地平面

requestafullreferencetogroundlevel

-

iMX6

+关注

关注

1文章

33浏览量

13669

发布评论请先 登录

相关推荐

iTOP-iMX6PLUS开发板-v_2.3底板扩展串口

NXP iMX8和iMX6 ARM处理器网络性能对比分析

iMX6板子gpio引脚的读写配置

iMX6开发板设备树文件分析

iMX6常见 Android系统问题

基于imx6处理器的核心板及底板的6层PCB设计原理图与全3D封装图纸

IMX6 MfgTool烧录指导手册

iMX6系列-iMX6Q 开发板 Python 移植

IMX6底板设计指南

IMX6底板设计指南

评论