AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的应用外,AXI FIFO还可以用于AXI系统总线和点对点高速应用。

AXI接口FIFO不支持Builtin FIFO和 Shift Register FIFO配置。

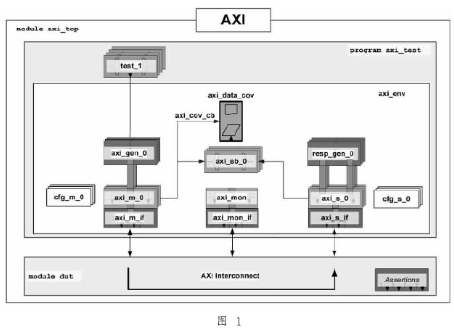

当需要连接到其他AXI功能时,可以在Native接口FIFO支持的相同应用中使用AXI FIFO。AXI FIFO可以通过IP集成器集成到系统中。

1 AXI FIFO的功能

AXI FIFO的功能概述主要体现在其对AXI Memory Mapped接口中读写通道的便捷集成能力上。

1.1 读写通道的分离

对于AXI Memory Mapped接口,AXI规范定义了写通道和读通道。

写通道包括写地址通道、写数据通道和写响应通道。

读通道包括读地址通道和读数据通道。

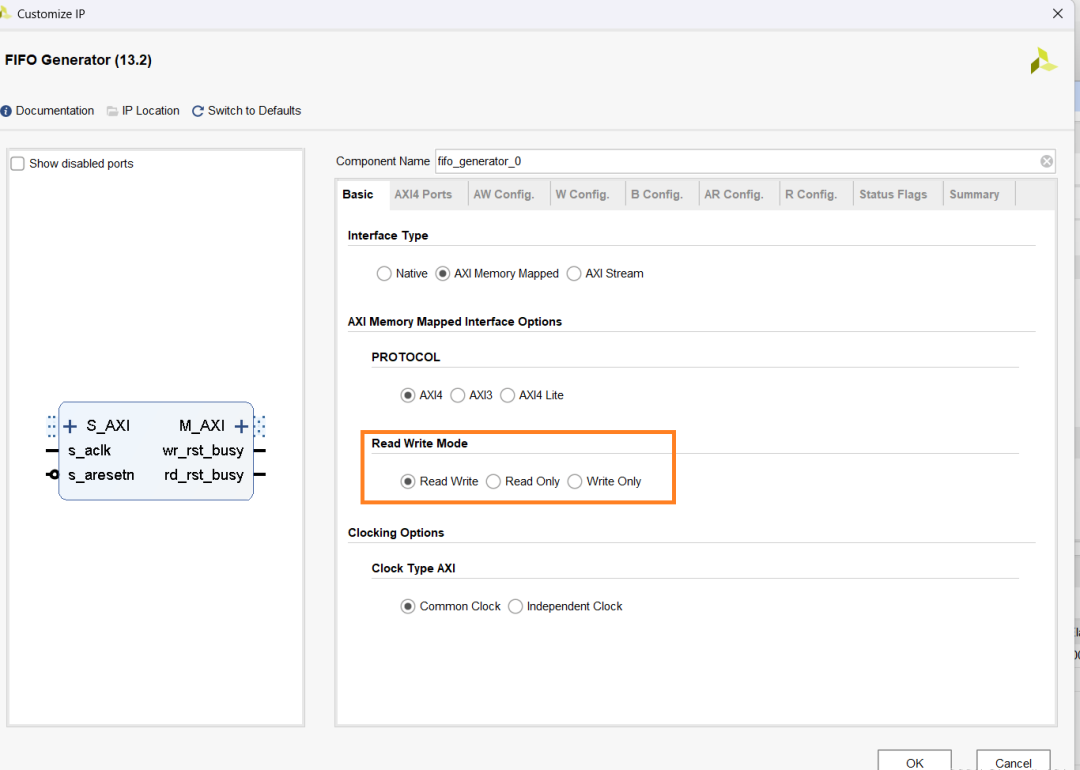

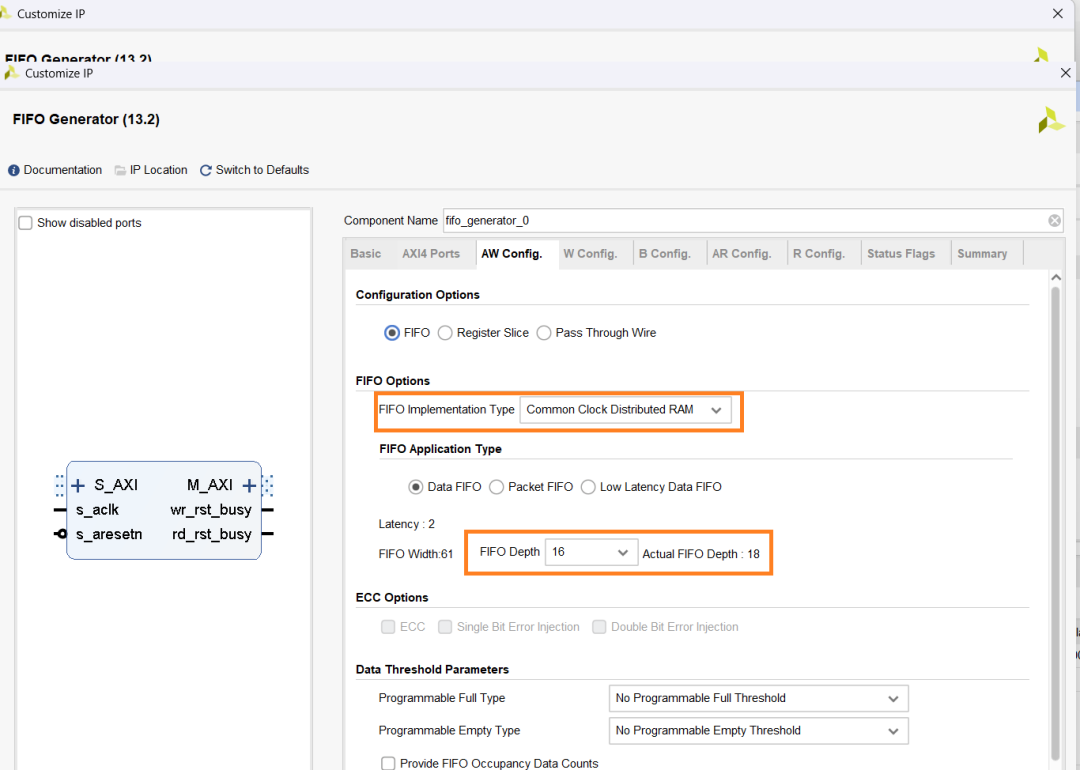

FIFO Generate IP核提供了为AXI Memory Mapped生成单独的写通道或读通道,或者同时生成写通道和读通道的能力。如下图所示。

对于写通道,集成了三个FIFO:一个用于写地址通道,一个用于写数据通道,以及一个用于写响应通道。

对于读通道,集成了两个FIFO:一个用于读地址通道,一个用于读数据通道。

当同时选择写通道和读通道时,FIFO Generate IP核将集成五个独立的FIFO。

1.2 每个通道的独立配置

对于每个通道,FIFO Generate IP核都可以独立配置以生成基于Block RAM或Distributed RAM FIFO。每个FIFO的深度也可以独立配置,以满足特定应用的数据缓存需求。如下图所示。

AXI FIFO的使用有助于简化高速数据传输和处理的系统设计,因为它们能够与AXI总线标准无缝集成,提供高吞吐量和低延迟的数据传输能力。这使得AXI FIFO成为高性能计算、图像处理、视频传输等领域的理想选择。

2 AXI FIFO的时序

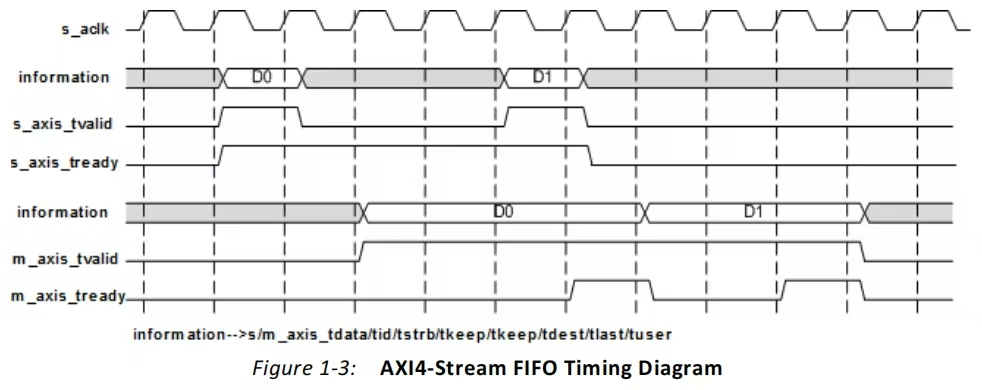

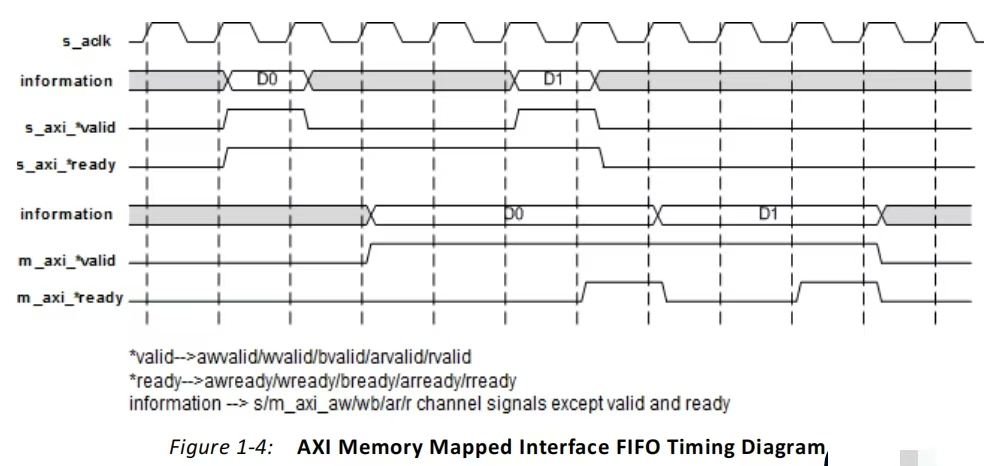

AXI接口协议使用双向的有效(Valid)和就绪(Ready)握手机制。信息源使用有效信号来表示通道上何时有有效的数据或控制信息可用。信息目标使用就绪信号来表示何时可以接受数据。图1-3展示了AXI4-Stream FIFO的写和读操作的示例时序图,而图1-4则展示了AXI Memory Mapped 接口FIFO的写和读操作的示例时序图。

在图1-3和图1-4中,信息源生成有效信号(valid)以指示数据何时可用。目标生成就绪信号(ready)以指示它可以接受数据,并且只有当有效信号和就绪信号都为高时,才会发生数据传输。

对于AXI4-Stream FIFO,写操作和读操作通常涉及连续的数据流传输。在图1-3中,看到写操作和读操作的时序图,显示了有效信号和就绪信号如何协同工作以完成数据传输。

而对于AXI Memory Mapped接口FIFO,写操作和读操作通常与特定的内存地址相关联。在图1-4中,看到写地址通道、写数据通道、写响应通道以及读地址通道和读数据通道的时序图。这些通道协同工作,通过有效和就绪信号的握手机制,确保数据在源和目标之间的正确传输。

由于AXI FIFO是从Native接口FIFO派生而来的,因此它们之间的很多行为是相似的。就绪信号是基于FIFO中可用空间来生成的,当FIFO中有空间时,就绪信号保持高电平以允许写入FIFO。只有当FIFO中没有剩余空间进行额外的写入操作时,就绪信号才会被拉低。有效信号则是基于FIFO中数据的可用性来生成的,当FIFO中有数据可供读取时,有效信号保持高电平以允许从FIFO中读取数据。只有当FIFO中没有可供读取的数据时,有效信号才会被拉低。这些信息信号被映射到Native 接口FIFO的din和dout总线上。AXI FIFO的宽度是通过连接AXI接口的所有信息信号来确定的。这些信息信号包括除有效和就绪握手信号之外的所有AXI信号。

在AXI协议中,这种握手机制确保了数据在源和目标之间的可靠传输。当源设备准备好发送数据时,它会将有效信号置高,表示数据已经准备好。然后,目标设备会检查就绪信号。只有当就绪信号也为高时,目标设备才会从源设备接收数据。这种机制确保了数据在传输过程中不会被丢失或发生错误。

AXI FIFO仅在First Word Fall Through模式下运行。该功能提供了在不执行读取操作的情况下查看FIFO中下一个可用字的能力。当FIFO中有数据时,第一个字会自动通过FIFO并出现在输出数据总线上。

注意:对于AXI接口,由于复位输入总是异步的,因此在内核内部会自动启用安全电路。

3 AXI FIFO的直通线(Pass Through Wire)

AXI Memory Mapped接口的IP核提供了直通线选项,使得所有输入信号能够直接传递到输出,而无需经过任何处理或缓存。这在某些情况下可能很有用,比如当您希望将信号直接转发到另一个接口或组件时。

3.1 数据包FIFO(Packet FIFO)

数据包FIFO配置确保了在接收到数据包(突发传输)的末尾(LAST节拍)之前,不会开始数据包的传输。这样做可以确保一旦主设备侧开始传输,数据就能不间断地可用,从而避免了AXI数据通道的源端停滞。这对于数据起源于主设备的应用场景特别有价值。

例如,当实时信号通道以低于下游AXI交换机和/或从设备目的地的数据速率运行时,如高带宽内存,这种配置就非常有用。

数据包FIFO原理既适用于AXI4/AXI3 Memory Mapped突发事务(写入和读取),也适用于AXI4-Stream数据包传输。这个特性有时被称为“store-and-forward”,它描述了内存映射写入和流传输的行为。对于内存映射读取,事务会延迟到FIFO中有足够的空位来确保整个读取数据包能够不间断地缓冲,这是根据AR(地址读取)通道事务的预测进行的。读取事务实际上并不依赖RLAST信号。

数据包FIFO特性支持公共时钟AXI4/AXI3和公共/独立时钟AXI4-Stream配置。它不支持AXI4-Lite配置。

3.2 AXI4-Stream Packet FIFO

AXI4-Stream Packet FIFO和AXI4/AXI3 Packet FIFO是两种不同类型的FIFO,它们分别使用AXI4-Stream接口和AXI Memory Mapped接口来实现数据包FIFO的功能。

AXI4-Stream Packet FIFO使用AXI4-Stream接口。当在AXI4-Stream Slave侧接收到一个完整的数据包(由tlast标记)或AXI4-Stream FIFO已满时,FIFO Generate IP核会在AXI4-Stream Master侧指示tvalid。由于FIFO变满而在Master侧指示tvalid是一个异常情况,在这种情况下,Packet FIFO会作为一个正常的FWFT(First Word Fall Through)FIFO工作,将Slave侧接收到的数据转发到Master侧,直到在Slave侧接收到tlast。

3.3 AXI4/AXI3 Packet FIFO

AXI4/AXI3 Packet FIFO 使用AXI Memory Mapped接口,它支持AXI协议中的写(W)和读(R)通道以及相关的地址(AW/AR)通道。Packet FIFO允许在数据传输过程中存储完整的数据包,直到数据包被完全接收或发送。

写通道上的Packet FIFO

当在AXI W通道Slave侧接收到一个由wlast标记的完整数据包时,FIFO Generate IP核会在AXI AW通道Master侧指示awvalid。这意味着写地址(AW)的传输只有在W通道Slave侧接收到请求传输所需的所有数据后才会被发送到AXI Write Address Channel。

写通道Packet FIFO与写地址通道(AW通道)耦合,这确保了在发送写请求之前,有足够的空间来存储与该请求相关的所有数据。

W通道的最小深度被设置为512,这允许写通道Packet FIFO存储两个最大长度的数据包。

读通道上的Packet FIFO

当在AXI R通道Master侧接收到一个由rlast标记的完整数据包时,FIFO Generate IP核会在AXI R通道Slave侧指示rvalid。这意味着读数据的传输(通过R通道)已经完成,并且整个数据包已经被成功接收。

读通道Packet FIFO与读地址通道(AR通道)耦合,这确保了在发送读请求之前,Packet FIFO中有足够的空间来存储与该请求相关的数据。如果Packet FIFO中没有足够的空间,则不会向AXI Read Address Channel发送AR传输。

R通道的最小深度也被设置为512,允许读通道Packet FIFO存储两个最大长度的数据包。

这种机制允许数据包在传输过程中被缓存,确保数据传输的连续性和完整性,同时避免由于数据不匹配或丢失而导致的错误。这对于需要处理大量数据或需要确保数据完整性的应用场景(如高速数据传输或实时信号处理)非常有用。

原文链接:https://tencentcloud.csdn.net/678a2f13edd0904849a69a14.html

-

接口

+关注

关注

33文章

8783浏览量

152462 -

fifo

+关注

关注

3文章

394浏览量

44120 -

总线

+关注

关注

10文章

2915浏览量

88736 -

AXI

+关注

关注

1文章

131浏览量

16850

原文标题:AXI接口FIFO简介

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

可以在EDK中使用Axi4Stream接口/总线吗?

AXI流FIFO挂起

高级可扩展接口(AXI)简介

AXI FIFO和AXI virtual FIFO这两个IP的使用方法

AXI STREAM FIFO如何设置双时钟

高级可扩展接口(AXI)简介

你必须了解的AXI总线详解

AXI接口FIFO简介

AXI接口FIFO简介

评论