HZ-CORE-RK3588J_K7是合众恒跃推出的一款ARM+FPGA异构融合的工业级核心板,集成了瑞芯微RK3588J处理器和Xilinx Kintex-7 FPGA,旨在满足工业控制、人工智能等领域对高性能和高可靠数据处理的需求。这款核心板将ARM处理器的强大通用计算能力与FPGA的高度并行可编程能力相结合,实现了低延迟、高带宽的高速数据处理。

在本文中,我们将深入分析HZ-CORE-RK3588J_K7所采用的FPGA技术架构及其在高性能数据处理中的应用。

01

高速数据处理能力

FPGA最大的优势在于高度并行计算能力。与CPU的顺序计算不同,FPGA内部拥有大量逻辑单元和DSP单元,能同时执行多项计算任务,如FFT、数字滤波、矩阵运算等算法,显著提升数据处理效率。此外,HZ-CORE-RK3588J_K7集成的Kintex-7 GTX高速收发器,能够实现FPGA与外设之间直接的高速数据交换,例如PCIe接口、多路10G以太网以及高速ADC接口,减少数据拷贝和中间缓冲环节,有效降低延迟并提高数据吞吐率。

值得一提的是,在高速串行链路中,为了确保信号完整性和可靠传输,GTX收发器还提供了一系列可调节参数和功能,例如预加重、均衡、时钟数据恢复(CDR)等。工程师可以根据高速信号的传输距离和介质,优化GTX收发器的设置以降低误码率。在高速通信应用中,充分发挥FPGA GTX收发器的性能并进行合理的协议定制,可以实现低延迟、高可靠的数据链路,这是软件实现难以企及的。总体而言,FPGA的高度并行计算加上GTX高速通信,使其在需要海量数据实时处理的场景中表现卓越。

02

PCIe 3.0数据加速机制

在HZ-CORE-RK3588J_K7架构中,FPGA与ARM处理器之间通过PCI Express高速总线相连。PCIe 3.0提供每通道8 GT/s的速率,可实现GB/s级别的数据吞吐。FPGA利用PCIe 3.0接口作为与处理器交换数据的桥梁,构建起低延迟的高速数据通道。Kintex-7 FPGA内部集成了PCIe硬核模块,支持实现PCIe Gen3 x4甚至x8的端点设计。通过PCIe接口,FPGA可以被映射为处理器系统中的一款高速外设,支持DMA(直接内存访问)等机制高效地与系统内存交换数据。

为了充分发挥PCIe 3.0的数据加速作用,工程师在设计时需要关注以下几点优化措施:

增大数据吞吐粒度

尽量使用较大的PCIe传输payload和批量DMA传输,以减少总线握手开销。例如,将数据打包成几百KB甚至更大的块再通过DMA发送,比频繁发送小数据包效率更高。

异步并行传输

使用FPGA内部多DMA通道或多队列机制,实现读写并行或多流并行传输。这样可以充分利用PCIe多条通道的带宽,防止单一事务阻塞影响整体吞吐。

流水线设计

在FPGA中设计好数据缓冲和流水线,使得数据在采集->处理->传输各阶段能够重叠执行。例如采用Ping-Pong双缓冲,FPGA在DMA传输当前缓冲区数据的同时,下一块数据采集或计算不间断进行,从而实现数据流的连续高速输出。

通过以上策略,FPGA可以将PCIe 3.0链路的带宽利用率最大化,实现与ARM内存之间近似实时的大容量数据交换。在数据采集(如高速ADC数据传输)、视频处理(如4K/8K超高清视频帧传输)等场景下,这种基于PCIe的FPGA加速机制能够显著提高系统的数据吞吐量和响应速度。

03

FPGA DDR3L高速缓存使用

HZ-CORE-RK3588J_K7核心板在FPGA旁配备DDR3L高速内存,作为FPGA的大容量缓存。相比Block RAM,DDR3L容量更大(数百MB至数GB),位宽更高、频率更快,数据存取速率更高。FPGA通过内置的控制器(如Xilinx MIG IP)管理DDR3L,通常速率可达1600 MT/s以上,32位接口理论带宽约6.4 GB/s。

FPGA可将DDR3L用作帧缓冲、FIFO队列或临时数据池。例如多路高清视频处理中可缓存视频帧进行并行编解码;高速数据采集中可作环形缓冲区,平衡数据流处理的不均衡性,解决外设与处理单元之间的速率差异。

为了充分发挥DDR3L在FPGA中的作用,架构设计上通常会考虑多通道数据处理和多端口存储访问:

多通道数据处理

针对多路并发数据,FPGA可在DDR3L中为每路数据设独立缓冲区,各通道读写逻辑独立、互不干扰。通过时间分片或多端口并行方式实现数据访问,有效保证并发数据流的高效存取。DDR3L的大带宽和容量可避免峰值流量下的数据丢失与延迟。

多端口存储架构

高性能FPGA设计中,多个模块常需同时访问DDR存储,如数据采集模块写入、处理模块读取计算。为避免访问冲突,可采用存储调度机制或双端口RAM架构。Kintex-7通过AXI总线矩阵和仲裁器,实现多主设备共享DDR3控制器。逻辑设计上,可利用双缓冲(Ping-Pong Buffer):当一个缓冲区写满时切换至另一缓冲区,读写并行交替进行,提高DDR利用率。HZ-CORE-RK3588J_K7板载DDR3L高速存储和灵活时钟管理,确保数据精准同步。在雷达信号处理、图像识别等高实时性场景下,FPGA借助DDR3L缓存实现实时处理与批处理的高效平衡。通过优化缓存架构和访问策略,DDR3L成为系统高速数据处理的核心缓冲区,保障数据高效流动。

04

FPGA与ARM的协同计算

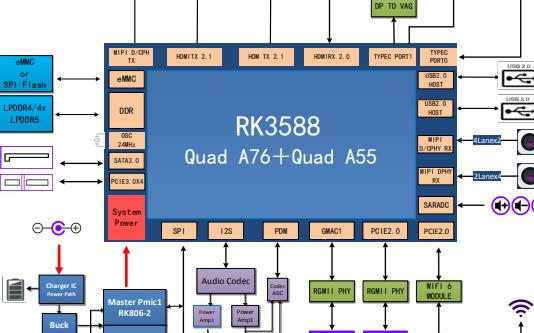

ARM端采用八核RK3588J(4核Cortex-A76+4核Cortex-A55,主频2.0GHz),内置6.0 TOPS算力NPU,适合AI推理、多媒体编解码等任务;FPGA端提供灵活可编程逻辑和强大并行计算能力,擅长定制算法加速与实时控制。两者通过高速接口共享数据和同步协作,ARM负责通用任务处理和调度,FPGA作为硬件加速器处理高实时性、高吞吐任务,形成高效的异构计算平台。具体协同方式包括:

AI推理

虽然RK3588J内置了强大的NPU,但FPGA在AI任务中仍有独特价值。FPGA可实现NPU不擅长的运算(如非标准精度处理、特殊模型加速),并可用于数据预处理(图像去噪、校正)或后处理,减轻ARM负载、优化整体性能。在特定场景中,FPGA还能实现完整的定制AI推理逻辑。ARM通过驱动程序向FPGA下发模型或部分计算任务,完成加速后再回传结果,从而同时利用NPU的高效与FPGA的灵活,实现更快、更灵活的AI推理。

视频编解码与多媒体处理

RK3588J处理器具备4K/8K视频编解码能力,可处理常见视频格式。但在特殊任务中,FPGA可提供辅助,例如在工业视觉场景下,对多路视频进行拼接、缩放和颜色转换后再交由ARM或GPU编码。FPGA还能实现定制滤波或图像增强,降低处理延迟、提高吞吐性能。FPGA与ARM通过共享缓冲区和中断机制协作,完成图像处理后通知ARM进行编码。此外,FPGA也可支持新兴或专有的视频编解码标准,扩展系统的多媒体能力。

工业自动化与实时控制

在工业控制系统中,FPGA凭借确定时序和高并行IO能力,实现高实时控制算法和高速接口协议,例如高速PID运算和伺服控制。ARM则负责路径规划、参数调节和人机交互等高层软件任务。当发生紧急情况时,FPGA能迅速执行保护措施并通知ARM处理。在工业通信领域,FPGA可硬件实现EtherCAT、PROFINET等实时协议,保证微秒级通信精度,ARM则运行协议栈与高层逻辑。

整体上,系统采用ARM主控、FPGA加速的协同模式:ARM处理复杂决策、通信和交互任务,FPGA执行实时性强、计算密集的任务,两者通过PCIe或片上总线协同工作,实现软硬件优势互补,达到“1+1>2”的效果。

05

实际应用案例

得益于以上所述的架构优势,HZ-CORE-RK3588J_K7在众多高性能数据处理场景中都有用武之地。下面结合几个实际案例,阐述FPGA在提升性能方面的作用,并给出相应的设计建议。

案例1:多通道工业数据采集与实时分析

实际应用中,工业物联网系统需要实时采集和分析多路高速传感器数据(如高频振动信号)。采用FPGA直接连接ADC前端,可完成多通道数据采集和数字滤波、FFT频谱分析等预处理,再通过PCIe接口将处理结果高速传输给ARM。ARM则负责故障诊断、数据上报并通过以太网上传至云端。

FPGA保证每个传感器通道数据实时、稳定采集,避免CPU负载过高造成数据丢失;ARM专注高层分析与通信任务。这种架构相比纯CPU方案,延迟更低、扩展性更佳,增加传感器通道仅需扩展FPGA逻辑单元,无需大量修改ARM软件。整体而言,FPGA协处理模式有效实现了工业数据采集系统的实时、高可靠监测和分析。

案例2:软件无线电(SDR)高速信号处理

软件无线电(SDR)需要对射频信号进行数字下变频、滤波和调制解调等高速处理。据此,FPGA通过与高速ADC/DAC配合,实现射频与基带间的实时转换与信号处理。在LTE/5G小基站设计中,FPGA完成PHY层高速FFT/IFFT、信道编码、数字上下变频,ARM则负责MAC层及以上协议处理和网络通信。

此外,通过FMC接口可扩展射频子卡,可直接连接FPGA的GTX收发器和高速IO,支持MIMO多通道并行处理。FPGA解调后的数据交由ARM组帧和网络处理,ARM发送的数据再由FPGA编码调制并发射。实际应用表明,这种ARM+FPGA协同架构实现了传统DSP难以达到的高吞吐与低延迟,充分体现了FPGA在SDR领域的性能优势与协作价值。

案例3:多摄像头图像处理与智能分析

在智能视觉系统中,经常需要同时处理多路高清摄像头视频,并运行AI算法进行目标检测或识别。FPGA可通过板载扩展接口并行采集多路MIPI摄像头图像数据,进行实时的缩放、同步、预处理等操作,再经PCIe传输至ARM处理器。ARM结合NPU完成AI推理,实现目标识别和分类。FPGA有效保证多摄像头数据的实时同步与低延迟预处理,显著降低整体分析延迟,提高系统吞吐量,满足工业与安防场景对实时性的严格要求。

综上所述,HZ-CORE-RK3588J_K7核心板通过其Kintex-7 FPGA的灵活可编程架构,在高性能数据处理领域展现出了强大的加速能力。

从工业传感、无线通信到视觉AI,各类应用都可以从ARM+FPGA的协同计算中受益。在设计这些系统时,我们建议工程师充分利用FPGA的并行硬件特性和高速通信接口,将关键的性能瓶颈部分卸载到FPGA中执行。同时注重ARM与FPGA之间的高效协作,通过硬件架构和软件架构的协调优化,工程师能够构建出性能卓越且灵活可靠的高性能数据处理系统,充分发挥HZ-CORE-RK3588J_K7这样的ARM+FPGA异构平台的价值。

-

FPGA

+关注

关注

1638文章

21853浏览量

609298 -

ARM

+关注

关注

134文章

9234浏览量

371668 -

核心板

+关注

关注

5文章

1061浏览量

30266

发布评论请先 登录

相关推荐

瑞芯微RK3588开发板RK3588 EVB和RK3588S EVB解读

重磅!基于瑞芯微RK3588旗舰芯片打造的MinipcRK3588面世

armsom推出工规级RK3588J-Core (armsom P1 Core) 8K 智能NVR核心板

RK3588是什么元件 RK3588的功耗如何

ITX 3588J源代码RK356X/RK3588 RKNN SDK

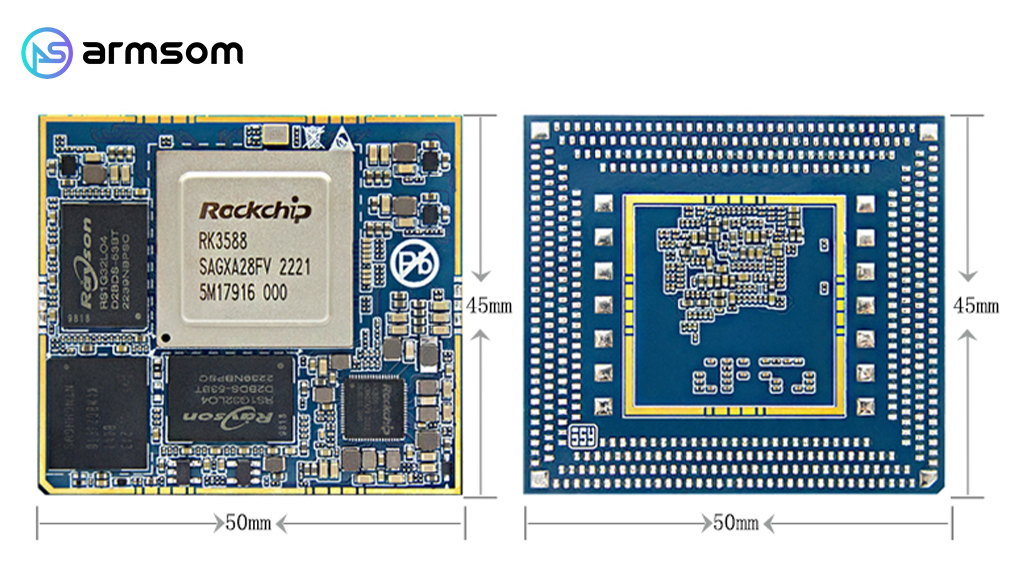

【LGA封装RK3588核心板】基于RK3588,小而强大的ArmSom-W3 CORE BOARD

rk3588和rk3588s的区别

rk3588和j4125参数对比

RK3588与3588s的区别

rk3588是armv8吗?rk3588硬件资料

新品发布 ▏性能猛兽登场!瑞芯微RK3588J_K7 ARM+FPGA双核异构核心板重磅发布!

破界而生,智领未来——瑞芯微RK3588J_K7的“悟空之力”

PET_RK3588_CORE核心板

HZ-CORE-RK3588J_K7 FPGA技术架构及应用分析

HZ-CORE-RK3588J_K7 FPGA技术架构及应用分析

评论