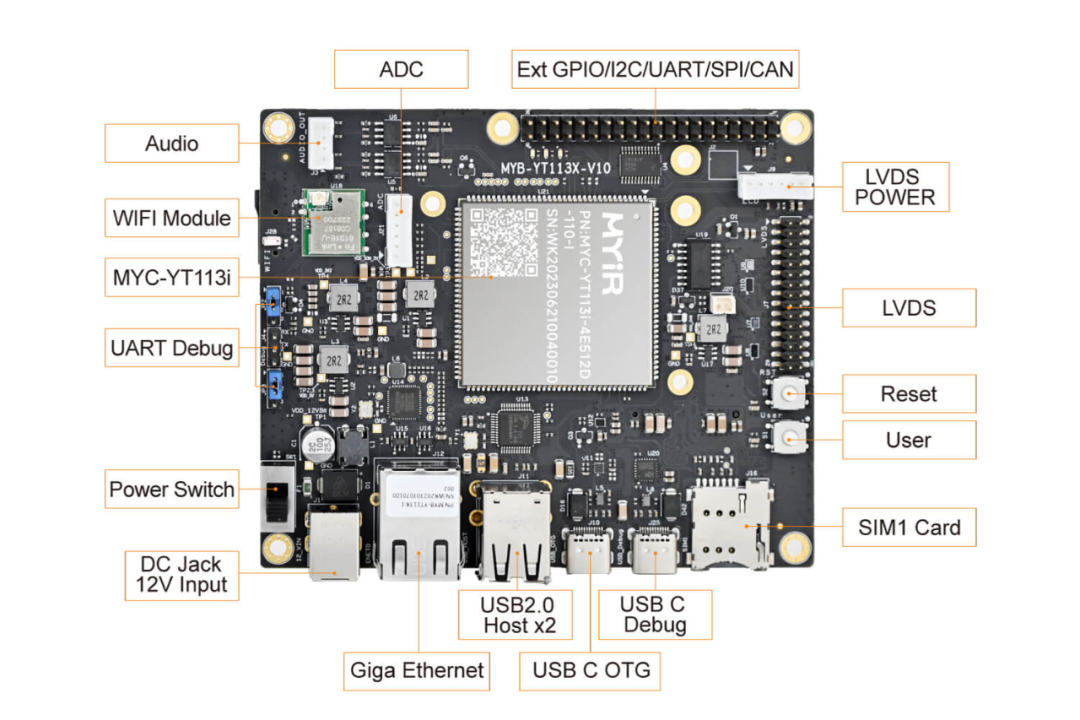

近年来,随着半导体产业的快速发展和技术的不断迭代,物联网设备种类繁多(如智能家居、工业传感器),对算力、功耗、实时性要求差异大,单一架构无法满足所有需求。因此米尔推出MYD-YT113i开发板(基于全志T113-i)来应对这一市场需求。

米尔基于全志T113-i核心板及开发板

part 01

T113-i芯片及OpenAMP简介

T113-i芯片简介

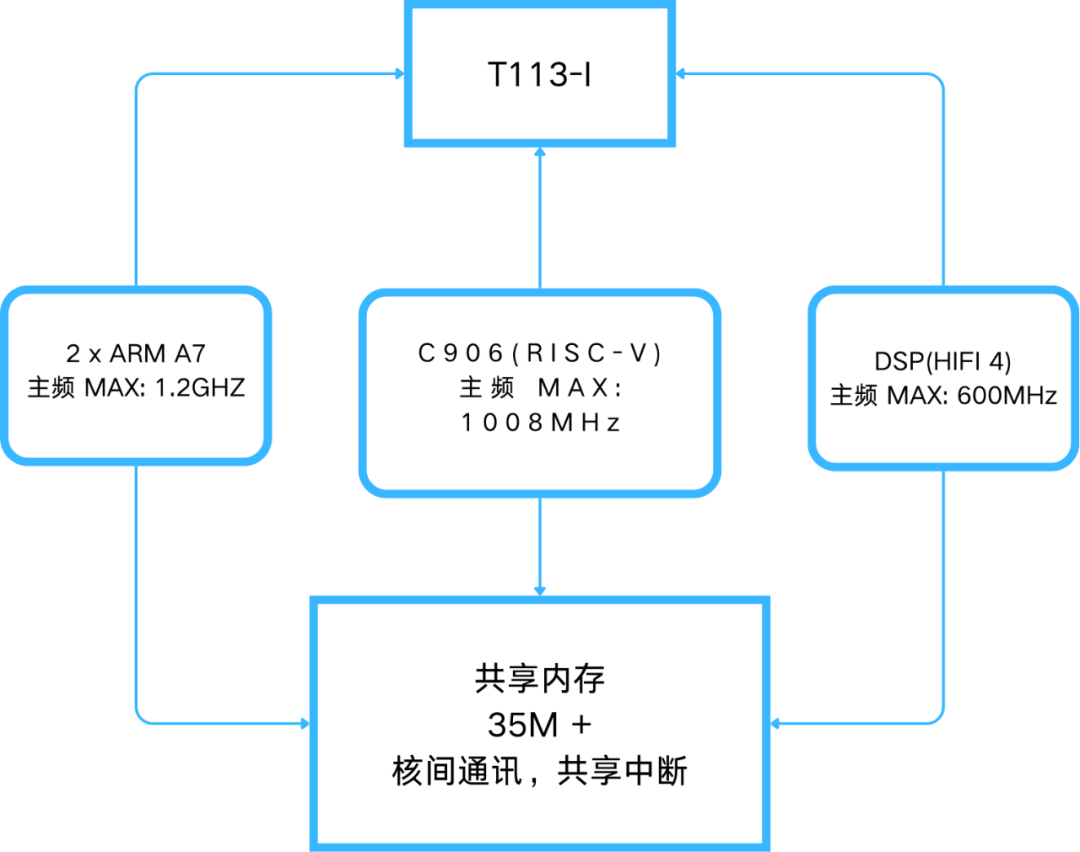

T113-i由两颗ARM A7 、一颗C906(RISC-V)和一颗DSP(HIFI 4)组成。

C906(RISC-V核)特性:

支持少量数据核间通讯(RPMsg)和大量核间数据(RPBuf)

- DSP(HIFI 4)特性:

- 最高主频600MHz

- 32KB L1 I-cache+32 KB L1 D-cache 64KBI-ram+64KB D-ram

- 操作系统支持裸跑和FreeRTOS实时操作系统

支持少量数据核间通讯(RPMsg)和大量核间数据(RPBuf)

OpenAMP系统原理

T113-i=2×ARM A7 + 1×C906(RISC-V) + 1×DSP(HIFI 4)组成,其中两个A7核为主核心,C906(RISC-V核)和DSP为双副核心。而其中的RISC-V属于超高能效副核心,标配内存管理单元,可运行RTOS或裸机程序,T113的主核运行Linux进行人机界面的交互和应用流程,而RISC-V则是后台可进行大数据数据采集,或者相关编码器的控制等,降低主核被中断的次数,大大提供了主核的运行效率。每个处理器核心相互隔离,拥有属于自己的内存,既可各自独立运行不同的任务,又可多个核心之间进行核间通信,这些不同架构的核心以及他们上面所运行的软件组合在一起,就成了 AMP 系统(Asymmetric Multiprocessing System 异构多处理系统)即非对称多处理架构。

part 02

AMP系统通信机制详解

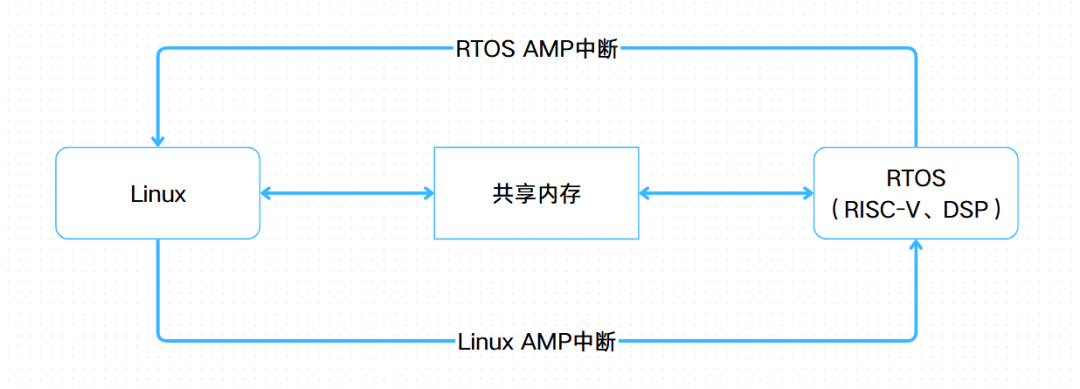

AMP通信原理

由于两个核心存在的目的是协同的处理,因此在异构多处理系统中往往会形成Master-Remote结构。主核心启动后启动从核心。当两个核心上的系统都启动完成后,他们之间就通过IPC(Inter Processor Communication)方式进行通信,而 RPMsg就是IPC中的一种。

在AMP系统中,两个核心通过共享内存的方式进行通信。两个核心通过AMP中断来传递讯息。内存的管理由主核负责

。

使用 RPMsg进行核间通信

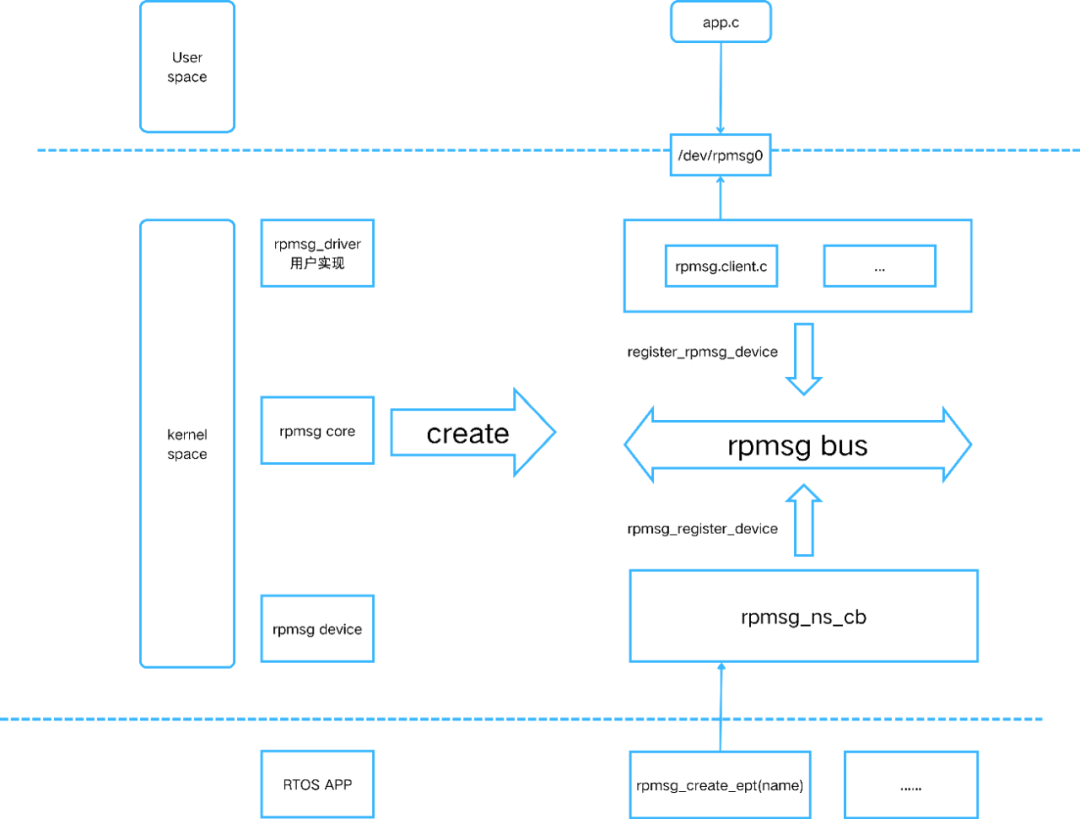

RPMsg整体通讯框架

上面介绍了通讯原理,这里讲解如何通讯,AMP使用RPMsg框架进行通讯,该框架用于AMP场景下处理器之间进行相互通信。OpenAMP内部实现了可用于RTOS或裸机系统中的RPMsg框架,与Linux内核的RPMsg框架兼容。

其通信链路建立流程如下:

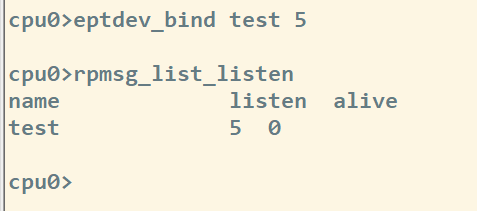

- RTOS 端调用 rpmsg_create_ept 创建指定 name 的端点。

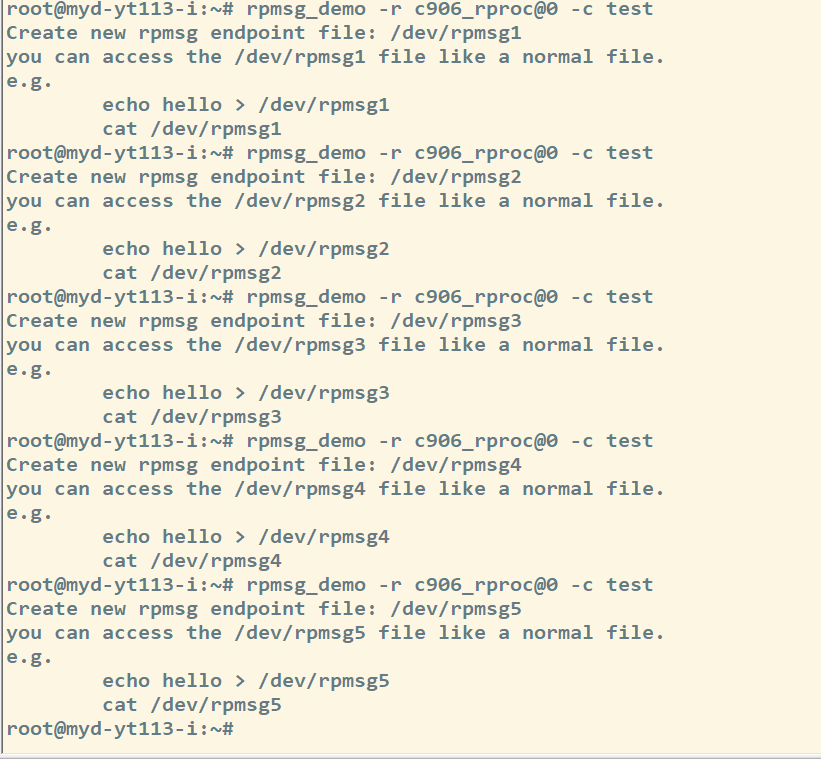

- Linux 端 rpmsg core 层收到端点创建消息,调用 rpmsg_register_device 将其作为一个设备注册到 rpmsg bus。

- Linux 端 rpmsg bus 匹配到相应的驱动,触发其 probe 函数。

- Linux 端驱动 probe 函数完成一些资源的分配以及文件节点的生成。

- Linux 端驱动的 probe 函数调用完后,rpmsg bus 会回复一个 ACK。

RTOS 端收到 ACK 后设置端点的状态,此时使用 is_rpmsg_ept_ready 函数会返回 true。

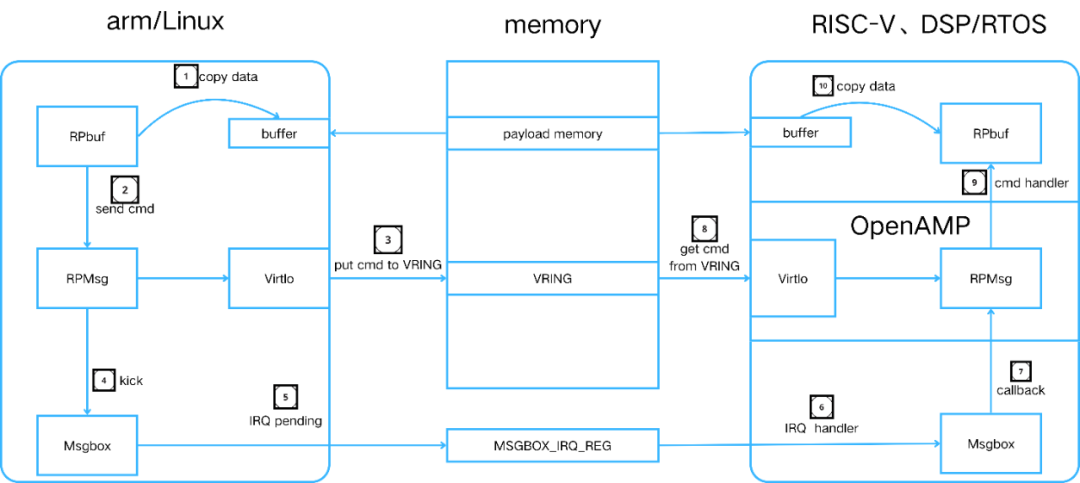

RPMsg数据传输流程如下:

下面展示一次RPMsg数据传输的通信过程,下面详细说明:

- arm端把数据拷贝到buffer中,在初始化时已经将buffer和payload memory地址绑定,因此数据拷贝后相当于存放到了payloadmemory中。

在消息传输命令后加上数据在payload memory中的起始地址和长度,组成数据包,调用RPMsg接口发送。

RPBuf:基于共享内存和RPMsg消息通知,实现传输大数据传输的框架。RPMsg:基于VirtIO管理的共享内存,实现数据传输的框架。

VirtIO:原本是一套用在虚拟化环境中传输数据的框架,这里用作共享内存(VRING)的管理。

OpenAMP:OpenAMP框架为RTOS、裸机和Linux用户空间提供了RPMsg、VirtIO、re-moteproc(未列出)的实现,并且与Linux内核兼容。Msgbox:是全志平台提供的一套消息中断机制,已通过linux内核中原生的mailbox框架作适配。

MSGBOX_IRO_REG:Msgbox的中断相关寄存器。

buffer:表示申请到的共享内存。用户通过操作buffer对象,可直接访问对应的共享内存。

payload memory:用来存放实际传输数据的共享内存,因此称为payload(有效负载)。

VRING:由Virtl0管理的一个环形共享内存。

part 03

案例与性能测试

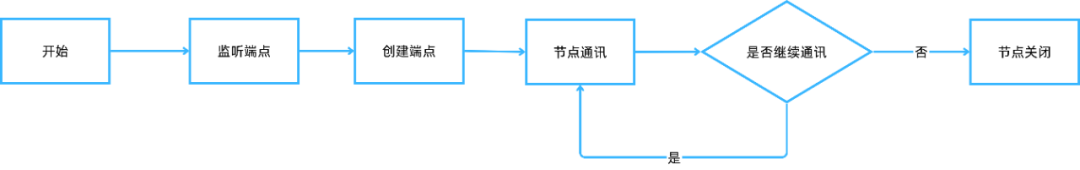

A核与RISC-V核通讯流程

A核与RISC-V核通讯流程如下:

1. 首先监听端点

2. 创建端点

3. 节点通讯

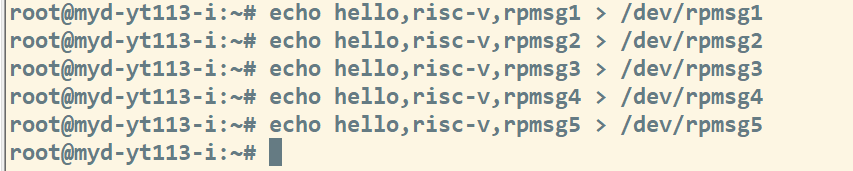

linux向riscv发送

4. riscv接收数据

A核与RISC-V核数据传输性能测试

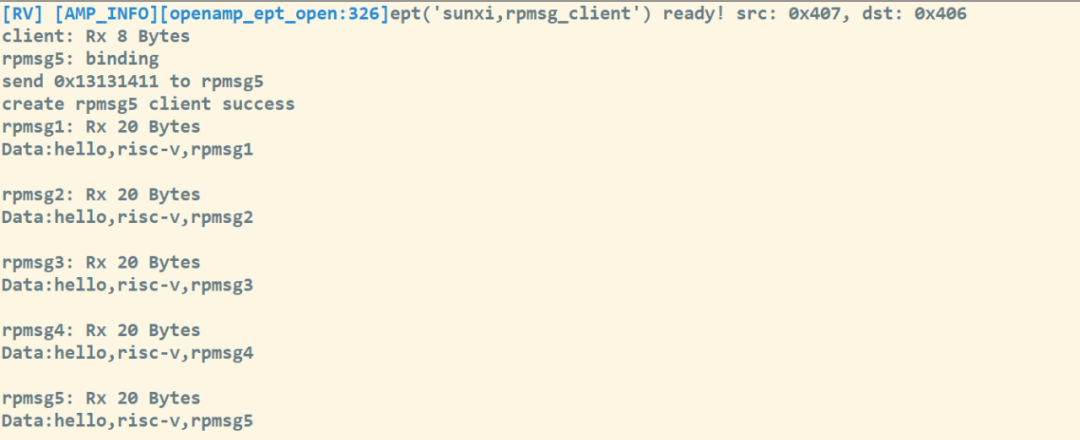

A核与RISC-V核数据传输性能测试,使用rpmsg_test命令对rpmsg进行性能测试,测试发送方向和接收方向各自的耗时以及速率。

1. 主核测试结果:

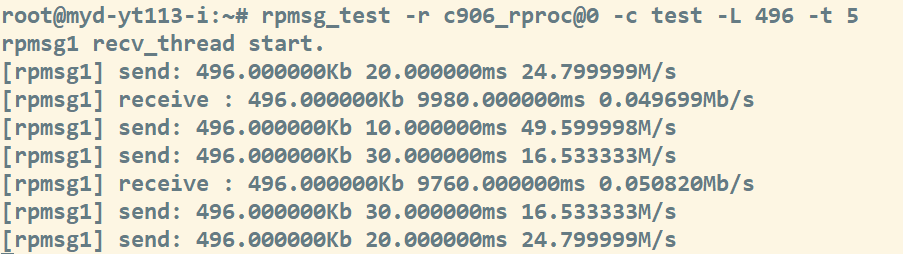

2. 从核测试结果:

3. 通过输出的结果可以得到:

[rpmsg1] send: 496.000000Kb 20.000000ms 24.799999M/s

[rpmsg1] receive : 496.000000Kb 9980.000000ms 0.049699Mb/s

发送496KB数据耗时20ms发送速率为24.79Mb/s

接收496KB数据耗时9980ms发送速率为0.049699Mb/s

- DSP GPADC采集测试

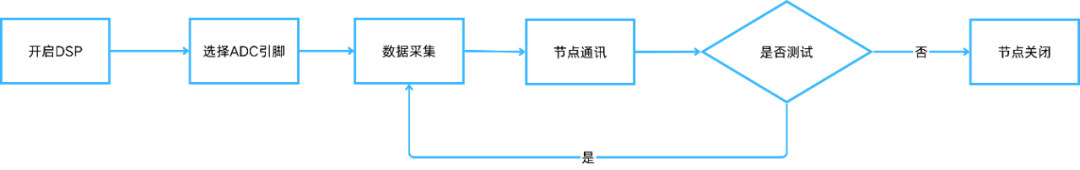

采集流程如下:

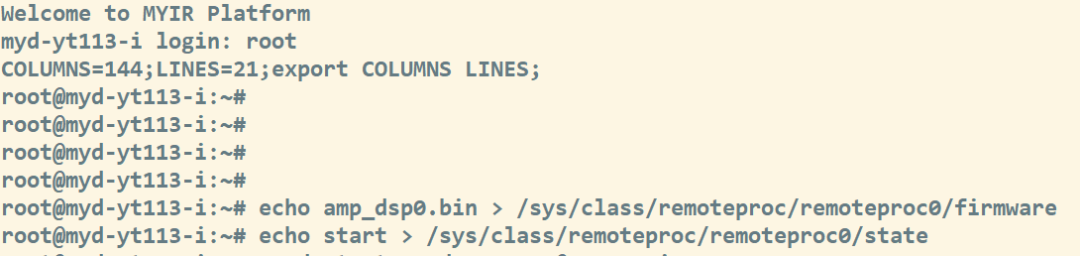

1. 开启DSP

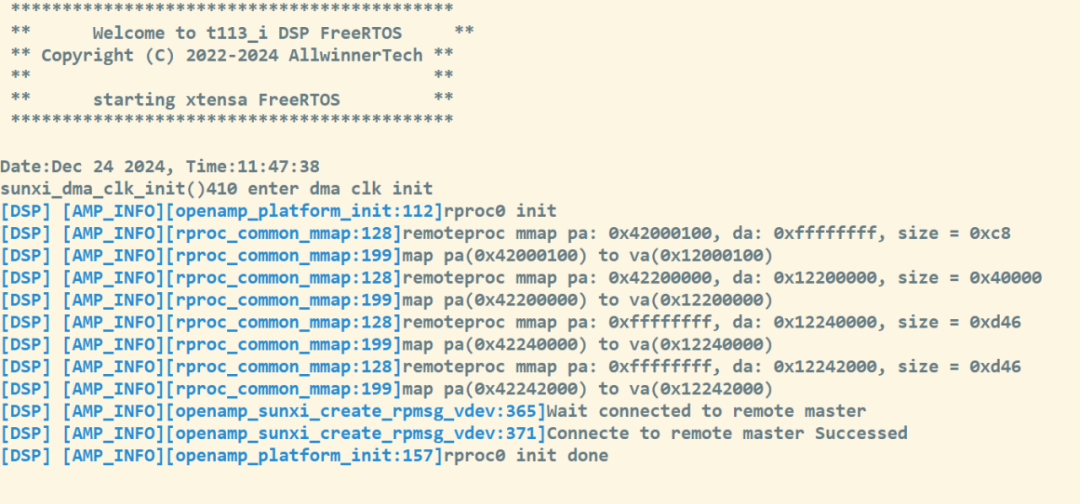

2. DSP核打印

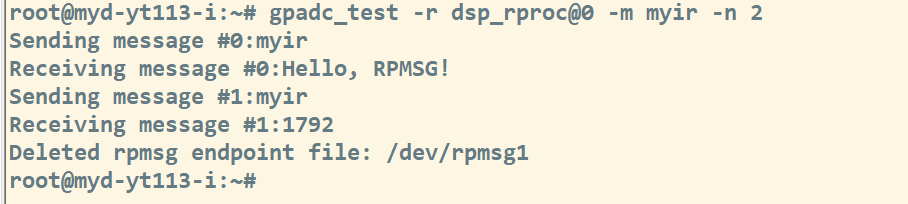

3. 开启DSP后,把GPADC0引脚接入1.8V电源,此时用户可以执行A核应用程序与DSP进行通讯,使DSP进行GPADC采集并返回数据

可以看到GPADC0收的电压数据为1792,转换为电压值为:1792/1000=1.792V。

米尔T113-i核心板配置型号

产品型号 | 主芯片 | 内存 | 存储器 | 工作温度 |

| MYC-YT113i-4E256D-110-I | T113-i | 256MB DDR3 | 4GB eMMC | -40℃~+85℃ |

| MYC-YT113i-4E512D-110-I | T113-i | 512MB DDR3 | 4GB eMMC | -40℃~+85℃ |

| MYC-YT113i-8E512D-110-I | T113-i | 512MB DDR3 | 8GB eMMC | -40℃~+85℃ |

| MYC-YT113i-8E1D-110-I | T113-i | 1GB DDR3 | 8GB eMMC | -40℃~+85℃ |

表MYC-YT113-i核心板选型表

米尔T113-i开发板配置型号

产品型号 | 对应核心板型号 | 工作温度 |

| MYD-YT113i-4E256D-110-I | MYC-YT113i-4E256D-110-I | -40℃~+85℃ 工业级 |

| MYD-YT113i-4E512D-110-I | MYC-YT113i-4E512D-110-I | -40℃~+85℃工业级 |

| MYD-YT113i-8E512D-110-I | MYC-YT113i-8E512D-110-I | -40℃~+85℃工业级 |

| MYD-YT113i-8E1D-110-I | MYC-YT113i-8E1D-110-I | -40℃~+85℃工业级 |

表MYD-YT113-i开发板选型表

-

dsp

+关注

关注

555文章

8088浏览量

352974 -

ARM

+关注

关注

134文章

9237浏览量

371944 -

开发板

+关注

关注

25文章

5260浏览量

99746 -

RSIC-V

+关注

关注

4文章

15浏览量

6616 -

米尔电子

+关注

关注

0文章

123浏览量

617

发布评论请先 登录

相关推荐

开源项目!DIY了一台无人机,用全志T113芯片

DIY了一台无人机,用全志T113芯片

全志T113双核异构处理器的使用基于Tina Linux5.0——RTOS简介

全志T113双核异构处理器的使用基于Tina Linux5.0——RTOS编译开发说明

全志T113双核异构处理器的使用基于Tina Linux5.0——异构双核通信的具体实现

国产开发板—米尔全志T113-i如何实现ARM+RISC-V+DSP协同计算?

Arm+RISC-V双核异构前景如何?

【米尔-全志T113-S3开发板- 极致双核A7国产处理器-试用体验】米尔-全志T113-S3开发板初次接触体验感不错

全志T113核心板|T113芯片,双核A7米尔核心板零售价低至79元!

全志D1和t113对比

基于T113开发板优化启动速度方法

7折购!米尔基于全志T113系列开发板

一篇文章玩转T113的ARM+RSIC V+DSP三核异构!

一篇文章玩转T113的ARM+RSIC V+DSP三核异构!

评论