1、滤波时选用电感,电容值的方法是什么?

电感值的选用除了考虑所想滤掉的噪声频率外,还要考虑瞬时电流的反应能力。如果LC的输出端会有机会需要瞬间输出大电流,则电感值太大会阻碍此大电流流经此电感的速度,增加纹波噪声(ripple noise)。 电容值则和所能容忍的纹波噪声规范值的大小有关。纹波噪声值要求越小,电容值会较大。而电容的ESR/ESL也会有影响。

另外,如果这LC是放在开关式电源(switching regulation power)的输出端时,还要注意此LC所产生的极点零点(pole/zero)对负反馈控制(negative feedback control)回路稳定度的影响。

2、模拟电源处的滤波经常是用LC电路。但是为什么有时LC比RC滤波效果差?

LC与RC滤波效果的比较必须考虑所要滤掉的频带与电感值的选择是否恰当。因为电感的感抗(reactance)大小与电感值和频率有关。如果电源的噪声频率较低,而电感值又不够大,这时滤波效果可能不如RC。但是,使用RC滤波要付出的代价是电阻本身会耗能,效率较差,且要注意所选电阻能承受的功率。

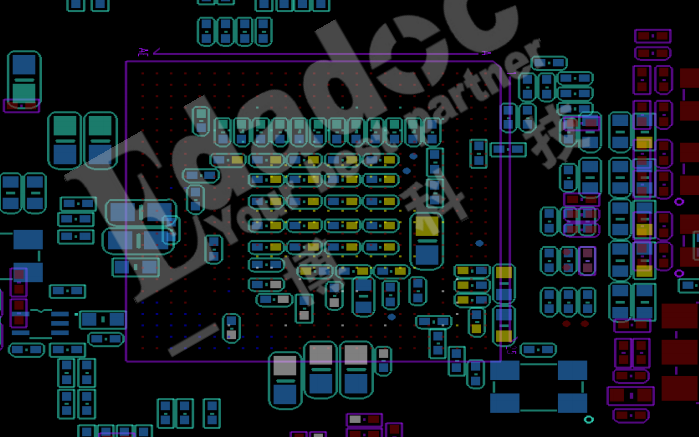

3、在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请介绍在高速(>100MHz)高密度PCB设计中的技巧?

在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

1)控制走线特性阻抗的连续与匹配。

2)走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。

3)选择适当的端接方式。

4)避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5)利用盲埋孔(blind/buried via)来增加走线面积。但是PCB板的制作成本会增加。

在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

4、如何尽可能的达到EMC要求,又不致造成太大的成本压力?

PCB板上会因EMC而增加的成本通常是因增加地层数目以增强屏蔽效应及增加了ferrite bead、choke等抑制高频谐波器件的缘故。除此之外,通常还是需搭配其它机构上的屏蔽结构才能使整个系统通过EMC的要求。以下仅就PCB板的设计技巧提供几个降低电路产生的电磁辐射效应。

1)尽可能选用信号斜率(slew rate)较慢的器件,以降低信号所产生的高频成分。

2)注意高频器件摆放的位置,不要太靠近对外的连接器。

3)注意高速信号的阻抗匹配,走线层及其回流电流路径(return current path), 以减少高频的反射与辐射。

4)在各器件的电源管脚放置足够与适当的去耦合电容以缓和电源层和地层上的噪声。特别注意电容的频率响应与温度的特性是否符合设计所需。

5)对外的连接器附近的地可与地层做适当分割,并将连接器的地就近接到chassis ground。

6)可适当运用ground guard/shunt traces在一些特别高速的信号旁。但要注意guard/shunt traces对走线特性阻抗的影响。

7)电源层比地层内缩20H,H为电源层与地层之间的距离。

5、另一种作法是在确保数/模分开布局,且数/模信号走线相互不交叉的情况下,整个PCB板地不做分割,数/模地都连到这个地平面上。道理何在?

数模信号走线不能交叉的要求是因为速度稍快的数字信号其返回电流路径(return current path)会尽量沿着走线的下方附近的地流回数字信号的源头,若数模信号走线交叉,则返回电流所产生的噪声便会出现在模拟电路区域内。

6、当一块PCB板中有多个数/模功能块时,常规做法是要将数/模地分开,原因何在?

将数/模地分开的原因是因为数字电路在高低电位切换时会在电源和地产生噪声,噪声的大小跟信号的速度及电流大小有关。如果地平面上不分割且由数字区域电路所产生的噪声较大而模拟区域的电路又非常接近,则即使数模信号不交叉, 模拟的信号依然会被地噪声干扰。也就是说数模地不分割的方式只能在模拟电路区域距产生大噪声的数字电路区域较远时使用。

7、在高速PCB设计原理图设计时,如何考虑阻抗匹配问题?

在设计高速PCB电路时,阻抗匹配是设计的要素之一。而阻抗值跟走线方式有绝对的关系, 例如是走在表面层(microstrip)或内层(stripline/double stripline),与参考层(电源层或地层)的距离,走线宽度,PCB材质等均会影响走线的特性阻抗值。也就是说要在布线后才能确定阻抗值。一般仿真软件会因线路模型或所使用的数学算法的限制而无法考虑到一些阻抗不连续的布线情况,这时候在原理图上只能预留一些terminators(端接),如串联电阻等,来缓和走线阻抗不连续的效应。真正根本解决问题的方法还是布线时尽量注意避免阻抗不连续的发生。

8、在高速PCB设计时,设计者应该从那些方面去考虑EMC、EMI的规则呢?

一般EMI/EMC设计时需要同时考虑辐射(radiated)与传导(conducted)两个方面. 前者归属于频率较高的部分(>30MHz)后者则是较低频的部分(<30MHz). 所以不能只注意高频而忽略低频的部分。一个好的EMI/EMC设计必须一开始布局时就要考虑到器件的位置, PCB迭层的安排, 重要联机的走法, 器件的选择等, 如果这些没有事前有较佳的安排, 事后解决则会事倍功半, 增加成本. 例如时钟产生器的位置尽量不要靠近对外的连接器, 高速信号尽量走内层并注意特性阻抗匹配与参考层的连续以减少反射, 器件所推的信号之斜率(slew rate)尽量小以减低高频成分, 选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降低电源层噪声。另外, 注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗loop impedance尽量小)以减少辐射. 还可以用分割地层的方式以控制高频噪声的范围. 最后, 适当的选择PCB与外壳的接地点(chassis ground)。

9、哪里能提供比较准确的IBIS模型库?

IBIS模型的准确性直接影响到仿真的结果。基本上IBIS可看成是实际芯片I/O buffer等效电路的电气特性资料,一般可由SPICE模型转换而得 (亦可采用测量, 但限制较多),而SPICE的资料与芯片制造有绝对的关系,所以同样一个器件不同芯片厂商提供,其SPICE的资料是不同的,进而转换后的IBIS模型内之资料也会随之而异。也就是说,如果用了A厂商的器件,只有他们有能力提供他们器件准确模型资料,因为没有其它人会比他们更清楚他们的器件是由何种工艺做出来的。如果厂商所提供的IBIS不准确, 只能不断要求该厂商改进才是根本解决之道。

10、如何选择EDA工具?

目前的pcb设计软件中,热分析都不是强项,所以并不建议选用,其它的功能1.3.4可以选择PADS或Cadence性能价格比都不错。PLD的设计的初学者可以采用PLD芯片厂家提供的集成环境,在做到百万门以上的设计时可以选用单点工具。

-

pcb

+关注

关注

4319文章

23105浏览量

398090 -

电路板

+关注

关注

140文章

4963浏览量

97942 -

PCB设计

+关注

关注

394文章

4689浏览量

85686

原文标题:PCB设计十问十答

文章出处:【微信号:gh_bee81f890fc1,微信公众号:面包板社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EMC十问十答,带你了解电磁兼容的“前世今生”

PCB设计十问十答

MP3十问十答(再简单也会有疑问)

PCB设计有哪些误区PCB设计的十大误区上部分内有下部分链接

PCB设计的十问十答

PCB设计6问6答资料下载

高层PCB设计的十大黄金法则

虹科分享 | 关于TrueNAS十问十答

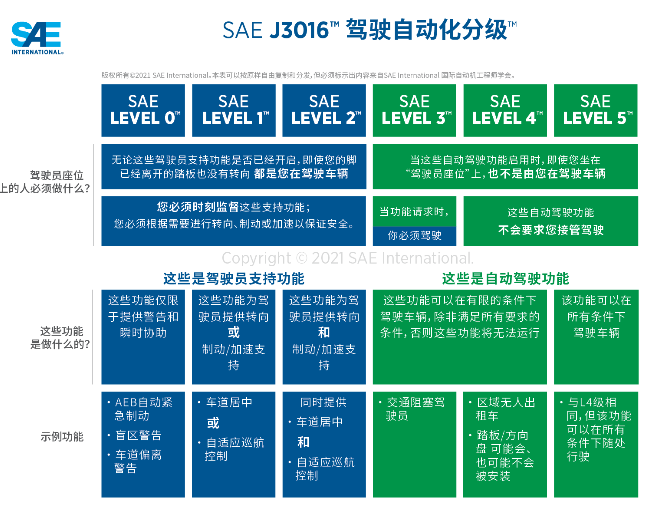

自动驾驶“十问十答”

PCB设计十问十答

PCB设计十问十答

评论