为了避免由于静电感应而损坏电路,焊接CMOS集成电路所使用的电烙铁必需良好接地,焊接时间不得超过5秒。最好使用20~25W内热式电烙铁和502环氧助焊剂,必要时可使用插座。

在接通电源的情况下,不应装拆CMOS集成电路。凡是与CMOS集成电路接触的工序,使用的工作台及地板严禁铺垫高绝缘的板材(如橡胶板、玻璃板、有机玻璃、胶木板等),应在工作台上铺放严格接地的细钢丝网或铜丝网,并经常检查接地可靠性。

CMOS集成电路的测试

测试时所有CMOS集成电路的仪器、仪表均应良好接地。如果是低阻信号源,应保证输入信号不超过CMOS集成电路的电源电压范围(CXXX系列为7~15V,C4000系列为3~18V),既VSS≤Vi≤VDD。如果输入信号一定要超过CMOS集成电路的电源电压范围,则应在输入端加一个限流电阻,使输入电流不超过5mA,以避免CMOS集成电路内部的保护二极管烧毁。

若信号源和CMOS集成电路用两组电源,开机时,应先接同CMOS集成电路电源,后接通信号源电源。关机时,应先关信号源电源,后关CMOS集成电路电源。

CMOS集成电路的保护措施

因为CMOS集成电路输入阻抗极高,随机的静电积累很可能使电路引出端任意两端的电压超过MOS管栅击穿电压,从而引起电路损坏。所以,CMOS集成电路不用时应把电路的外引线全部短路,或放在导电的屏蔽容器内,以防被静电击穿。

CMOS集成电路的互换。在使用中有些CMOS集成电路是可以直接换用。如国产CC4000可与国外产品CD4000、MC14000系列直接代换。

对于那些管脚排列和封装形式完全一致,但电参数有所不同的CMOS集成电路,换用时要十分注意。如国产CC4000和CXXX中有些品种,它们的工作电压有所差异,CC4000为3~18V、CXXX为7~15V。换用时要考虑到电源供电及负载能力问题。另外,对于那些封装形式及管脚排列不同的CMOS集成电路,一般不能直接代换。如果需要换用,则应做一些相应的变换使两者功能相同的引出端一一对应。

焊CMOS集成块。先找一块比集成块稍大的铝箔和一块平整的泡沫塑料。铝箔平放在塑料泡沫上,将CMOS集成块垂直插入泡沫塑料后随即拔起,使铝箔附在集成块上以使引脚全部短路。然后将集成块插入线路板的规定位置,像焊其它集成块那样焊接,焊好后撕去铝箔即可。

cmos电路焊接注意事项

CMOS集成电路由于输入电阻很高,因此极易接受静电电荷。为了防止产生静电击穿,生产CMOS时,在输入端都要加上标准保护电路,但这并不能保证绝对安全,因此使用CMOS集成电路时,必须采取以下预防措施。

①存放CMOS集成电路时要屏蔽,一般放在金属容器中,也可以用金属箔将引脚短路。

②CMOS集成电路可以在很宽的电源电压范围内提供正常的逻辑功能,但电源的上限电压(即使是瞬态电压)不得超过电路允许极限值、…电源的下限电压(即使是瞬态电压)不得低于系统工作所必需的电源电压最低值Vmin,更不得低于VSS。

③焊接CMOS集成电路时,一般用20W内热式电烙铁,而且烙铁要有良好的接地线。也可以利用电烙铁断电后的余热快速焊接。禁止在电路通电的情况下焊接。

④为了防止输入端保护二极管因正向偏置而引起损坏,输入电压必须处在VDD 和VSS之间,即VSS<u1<VDD。

⑤调试CMOS电路时,如果信号电源和电路板用两组电源,则刚开机时应先接通电路板电源,后开信号源电源。关机时则应先关信号源电源,后断电路板电源。即在CMOS本身还没有接通电源的情况下,不允许有输入信号输入。

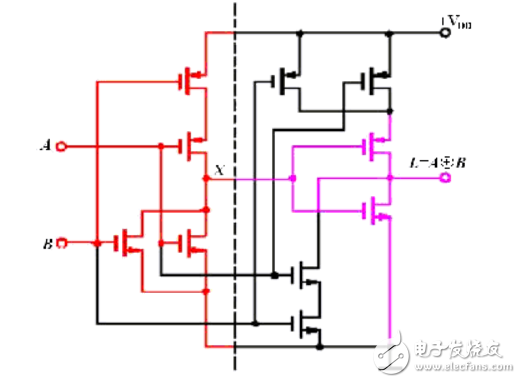

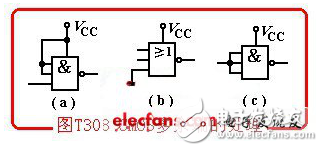

⑥ 多余输入端绝对不能悬空。否则不但容易受外界噪声干扰,而且输入电位不定,破坏了正常的逻辑关系,也消耗不少的功率。因此,应根据电路的逻辑功能需要分别情况加以处理。例如:与门和与非门的多余输入端应接到VDD或高电平;或门和或非门的多余输入端应接到VSS或低电平;如果电路的工作速度不高,不需要特别考虑功耗时,也可以将多余的输入端和使用端并联。如图T308所示。

以上所说的多余输入端,包括没有被使用但已接通电源的CMOS电路所有输入端。例如,一片集成电路上有4个与门,电路中只用其中一个,其它三个门的所有输入端必须按多余输入端处理。

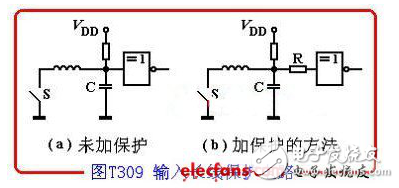

⑦输入端连接长线时,由于分布电容和分布电感的影响,容易构成LC振荡,可能使输入保护二极管损坏,因此必须在输入端串接一个10~20kΩ的保护电阻R,如图T309所示。

⑧CMOS电路装在印刷电路板上时,印刷电路板上总有输入端,当电路从机器中拔出时,输入端必然出现悬空,所以应在各输入端上接入限流保护电阻,如图T309所示。如果要在印刷电路板上安装CMOS集成电路,则必须在与它有关的其它元件安装之后再装CMOS电路,避免CMOS器件输入端悬空。

⑨插拔电路板电源插头时,应该注意先切断电源,防止在插拔过程中烧坏CMOS的输入端保护二极管。

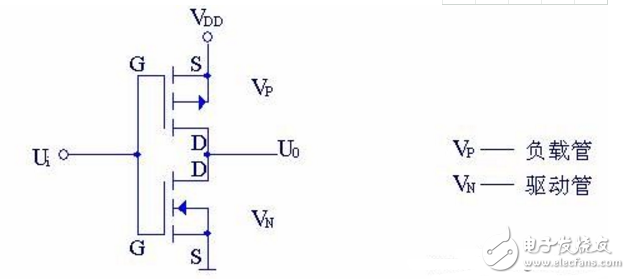

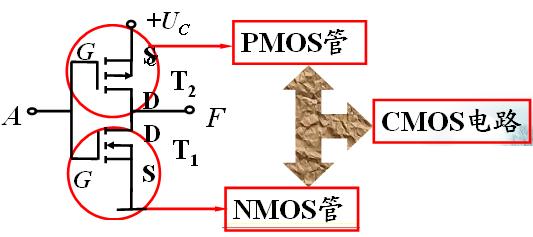

CMOS数字集成电路的特点

1.静态功耗低:电源电压VDD=5V的中规模电路的静态功耗小于100μW,从而有利于提高集成度和封装密度,降低成本,减小电源功耗。

2.电源电压范围宽:4000系列CMOS电路的电源电压范围为3~18V,从而使选择电源的余地大,电源设计要求低。

3.输入阻抗高:正常工作的CMOS集成电路,其输入端保护二极管处于反偏状态,直流输入阻抗可大于100MΩ,在工作频率较高时,应考虑输入电容的影响。

4. 扇出能力强:在低频工作时,一个输出端可驱动50个以上的CMOS器件的输入端,这主要因为CMOS器件的输入电阻高的缘故。

5.抗干扰能力强:CMOS集成电路的电压噪声容限可达电源电压的45%,而且高电平和低电平的噪声容限值基本相等。

6.逻辑摆幅大:空载时,输出高电平VOH>VDD-0.05V,输出低电平VOL<VSS+0.05V。

7. CMOS集成电路还有较好的温度稳定性和较强的抗辐射能力。

不足之处是,一般CMOS器件的工作速度比TTL集成电路低,功耗随工作频率的升高而显著增大。

CMOS数字集成电路使用注意事项:

1.电源连接和选择:VDD端接电源正极,VSS端接电源负极(地)。绝对不许接错,否则器件因电流过大而损坏。对于电源电压范围为3V~18V系列器件。如CC4000系列,实验中VDD通常接+5V电源,VDD电压选在电源变化范围的中间值,例如电源电压在8~12V之间变化,则选择VDD=10V较恰当。

注意:CMOS器件在不同的VDD值下工作时,其输出阻抗、工作速度和功耗等参数都有所变化,设计中须考虑。

2.输入端处理:多余输入端不能悬空。应按逻辑要求接VDD或接VSS,以免受干扰造成逻辑混乱,甚至还会损坏器件。对于工作速度要求不高,,而要求增加带负载能力时,可把输入端并联使用。

对于安装在印刷电路板上的CMOS器件,为了避免输入端悬空,在电路板的输入端应接入限流电阻RP和保护电阻R,当VDD=+5V时,RP取5.1KΩ,R一般取100KΩ~1MΩ。

3.输出端处理:输出端不允许直接接VDD或VSS,否则将导致器件损坏,除三态(TS)器件外,不允许两个不同芯片输出端并联使用,但有时为了增加驱动能力,同一芯片上的输出端可以并联。

4.对输入信号VI的要求:VI的高电平VIH<VDD,VIL的低电平VIL小于电路系统允许的低电压;当器件VDD端末接通电源时,不允许信号输入,否则将使输入端保护电路中的二极管损坏。

5.CMOS器件的输入端和VSS之间接有保护二极管,除了电平变换器等一些接口电路外,输入端和正电源VDD之间也接有保护二极管,因此,在正常运转和焊接CMOS器件时,一般不会因感应电荷而损坏器件。但是,在使用CMOS数字集成电路时,输入信号的低电平不能低于(VSS-0.5V),除某些接口电路外,输入信号的高电平不得高于(VDD+0.5V),否则可能引起保护二极管导通,甚至损坏进而可能使输入级损坏。

-

集成电路

+关注

关注

5387文章

11516浏览量

361548 -

CMOS

+关注

关注

58文章

5708浏览量

235383

发布评论请先 登录

相关推荐

CMOS集成逻辑门电路的使用注意事项

cmos电路焊接注意事项

cmos电路焊接注意事项

评论