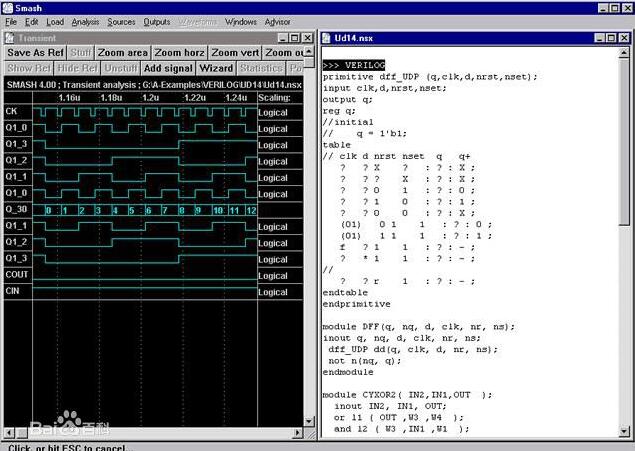

verilog语言是什么

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL是目前应用最为广泛的硬件描述语言.Verilog HDL可以用来进行各种层次的逻辑设计,也可以进行数字系统的逻辑综合,仿真验证和时序分析等。Verilog HDL适合算法级,寄存器级,逻辑级,门级和版图级等各个层次的设计和描述。

Verilog HDL进行设计最大的优点是其工艺无关性.这使得工程师在功能设计,逻辑验证阶段可以不必过多考虑门级及工艺实现的具体细节,只需根据系统设计的要求施加不同的约束条件,即可设计出实际电路。

Verilog HDL是一种硬件描述语言(hardware description language),为了制作数字电路而用来描述ASICs和FPGA的设计之用。Verilog 的设计者想要以 C 编程语言为基础设计一种语言,可以使工程师比较容易学习。

verilog语言基本语句有哪些

1、赋值语句:

(1)非阻塞赋值方式, 如 b《=a ;

特点:块结束后才完成操作,b的值不是立刻改变的。

(2)阻塞赋值方式, 如 b = a ;

特点:赋值语句执行完后,块才结束,b的值是立刻改变的。

2、块语句

(1)顺序块

顾明思议,就是顺序执行,这与C语言的顺序结构特性一样。

格式如下:

语句1到n是顺序执行的,也可给块命名,只需在begin后面加上“:块名”即可。当加给块命名后,才可以在块内定义局部变量,和块被其他语句调用,如disable语句。

(2)并行块

同样,从表面意思可知道,块内语句是并行进行的,也就是同时进行的。

当执行完所有语句或一个disable语句执行时,程序跳出并行块。

并行块的结构和顺序块的结构一样,只需将关键字换成fork…join

注意:begin 、 end 、 fork 、 join 后面都没有封号“;”。

3、条件语句

(1) if 语句

这里 if 语句与C语言没有什么不同,只需注意,在C语言里,用大括号的地方,在Verilog里都用begin…end 。

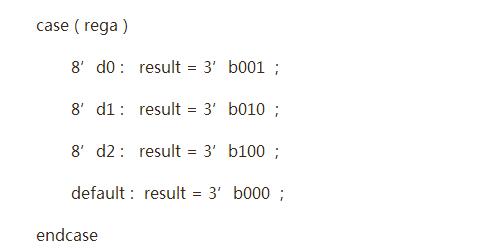

(2)case 语句

这个与C语言不同了,在Verilog里,没有switch,只有case ,示例如下:

这里也不需要break , 每当执行完一个case 分项后的语句,则跳出该case语句,终止case语句的执行。

另外,Verilog还提供了casex和casez两个语句,他们三者之间有一定的区别。

在用case 语句时,要求case括号中的值必须与分项中的值完全相等才执行,即满足“===”全等于的关系。

在用casex语句时,将高阻值z和不定值x 都视为不关心的值,即不比较其所在位的值,只需其他位满足全等于的关系即可。

在用casez语句时,不考虑高阻值的z比较过程,只考虑x 、0、1三个值。

注意:if语句和case语句都只能用于always语句内部,如果要在always语句之外应用条件语句,可用三目运算符 ? :如下:

assign data = ( sel ) ? a : b ;

4、循环语句

(1)for 语句 和 while 语句,这与C语言语法一样。不解释

(2)forever语句

forever循环常用于产生周期性的波形,用来作为仿真测试信号。它与always语句不同之处在于它不能独立写在程序中,而必须写在initial块中。

(3)repeat语句

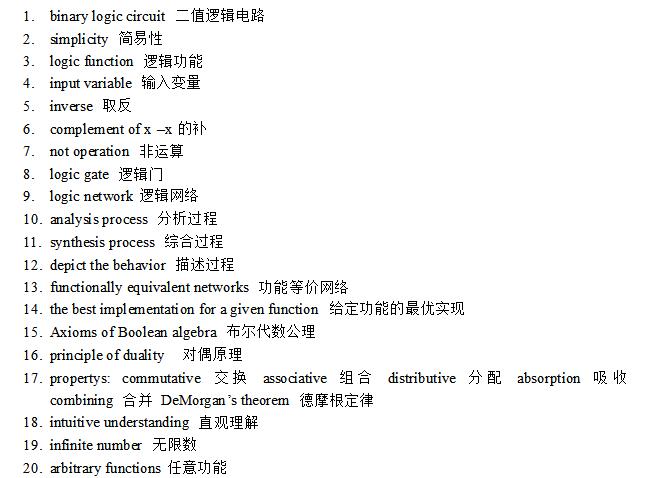

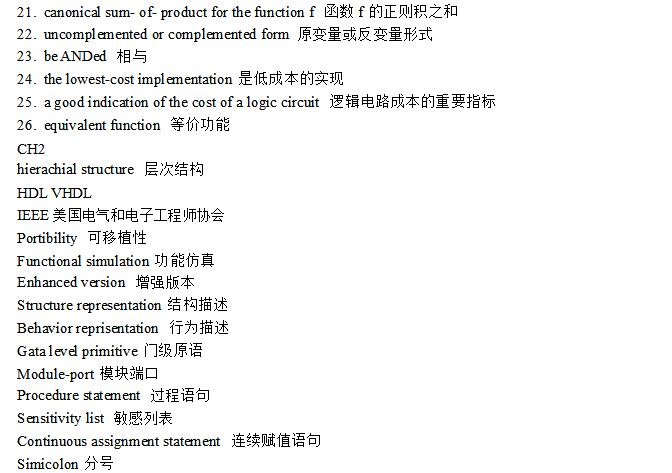

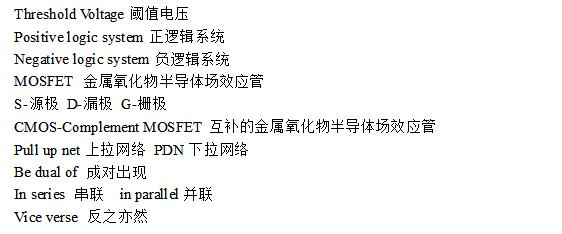

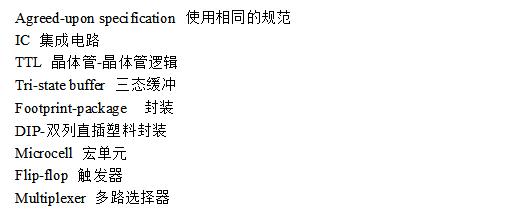

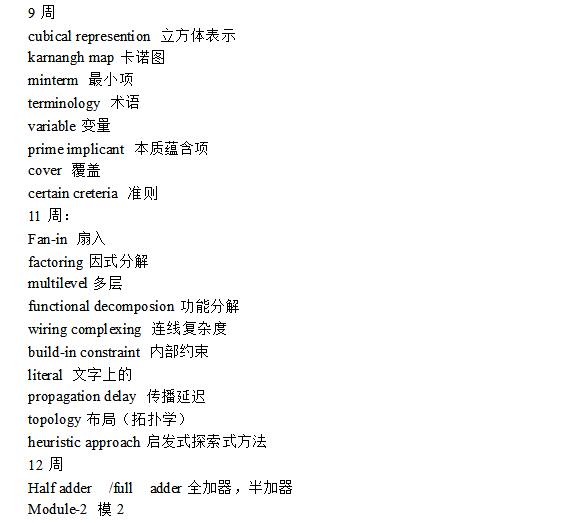

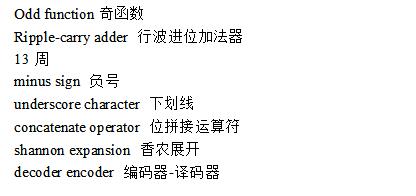

verilog语言词汇大全

Verilog的主要应用

1、ASIC和FPGA工程师编写可综合的RTL代码

2、 高抽象级系统仿真进行系统结构开发

3、测试工程师用于编写各种层次的测试程序

4、用于ASIC和FPGA单元或更高层次的模块的模型开发

如何学习verilog语言

如果搞FPGA开发verilog必然要精通。如果没有数字电路基础的话建议首先学一些基本的数字电路知识。

然后看书,《Verilog HDL数字设计与综合》,一定注意只要看能够综合的代码,那些不能综合的东西可以一带而过。

实践!实践!实践!光看书绝对学不会。如果你有开发板当然好,如果没有至少也要写程序仿真。当时我学的时候买了个几千块的开发板。这个东西不练绝对学不会。

总之,先看书,把基本的数电搞懂。然后最好学一点练一点。一个很有用的方法,就是对着书或者自己想一些代码,然后看看编出的电路是什么样子的。

FPGA和C语言等软件语言相比,非常难以调试。一定要保证学的扎实些。

verilog是硬件描述语言,归根结底你设计的是电路,而不是软件,不能那C语言等软件语言硬套。

学习verilog语言的注意事项

1、不使用初始化语句;

2、不使用延时语句;

3、不使用循环次数不确定的语句,如:forever,while等;

4、尽量采用同步方式设计电路;

5、尽量采用行为语句完成设计;

6、always过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号;

7、所有的内部寄存器都应该可以被复位;

8、用户自定义原件(UDP元件)是不能被综合的。

-

Verilog

+关注

关注

28文章

1351浏览量

110067 -

Verilog语言

+关注

关注

0文章

113浏览量

8224

发布评论请先 登录

相关推荐

verilog语言基本语句_verilog语言词汇大全

verilog语言基本语句_verilog语言词汇大全

评论