在Coarse Placement和Legalization之间,其实还有很重要的一个步骤, 就是对Scan Chain(扫描链)的处理。英文名Scan Reorder,直译为扫描链重组。

那讲Scan Reorder之前,有必要对Scan Chain的基本知识做一定普及。Scan chain其实是可测试性设计(DFT)中的内容。DFT,Design for test,其实是探测错误序列的一种设计方法学,由于芯片内部是一个黑盒子,在外部难以控制。测试人员通过DFT技术,可以从外部控制和观测电路内部触发器的信号值。DFT通常需要单独的一个部门来完成,很复杂,有专门的书籍可以参考。基本概念可以参考:

【时序分析基本概念介绍——花一样的“模式”】

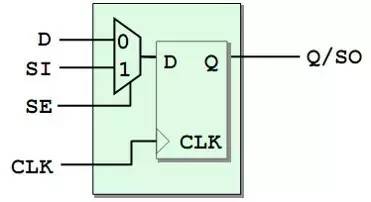

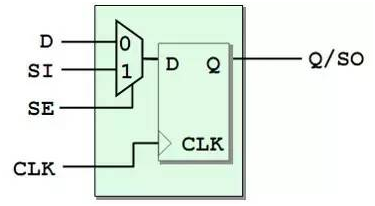

而在后端PR中,我们更关注的是DFT中的Scan Chain,有了它,我们的芯片就更加具有测试性。Scan Chain将芯片中的所应用的普通寄存器替换成带有扫描功能的扫描寄存器,首尾相连成串,从而可以实现附加的测试功能。那扫描寄存器特殊在什么地方呢?我们从它的结构图来看一下:

从上图中可以看出,它比普通存储器多了SI,SE,SO这3个端口。

1. 其中SI,SO也就是scan_in与scan_out端,定义了一条scan chain的input和output端。通常情况下,每一个input会驱动一条scan chain,一个ouput也是用来观察一条scan chain的。

2. SE是scan enable信号,它控制着scan cell的工作模式。从图中可以看出,SE,SI,D端通过一个Mux实现工作模式的切换。当SE输入为0时,scan cell工作在普通模式下,相当于是普通的flop;当SE输入为1时,scan cell就进入scan模式,相当于一个移位寄存器。

scan cell通常定义在lib库中直接导入,可以通过get_cells_of_scan_chain来做一些检查。

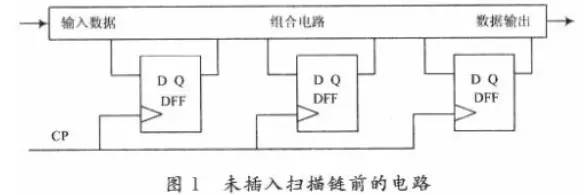

用图片说明可能会更加形象,对整个逻辑电路来说,未插入scan chain时,电路图如下:

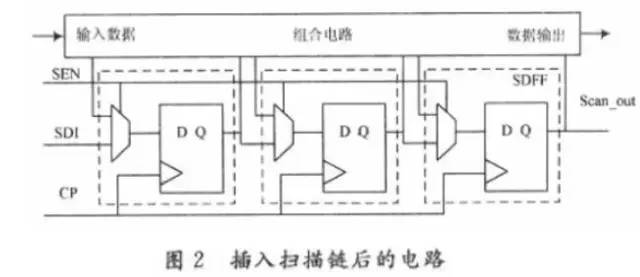

插入scan chain以后,软件会自动地用scan flip flop(SFF)替换掉普通的flip flop,并且连接SFF到scan chain上,这样就实现了移位扫描的功能,如下图所示:

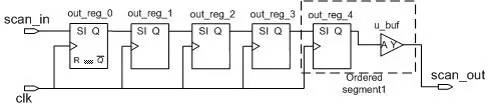

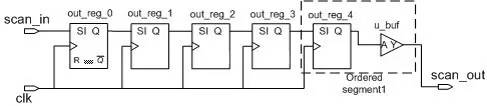

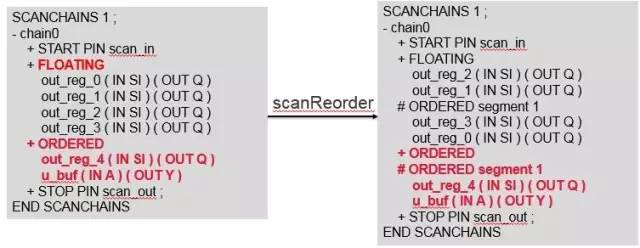

而后端对于扫描链的定义,通常使用DEF文件来定义,我们一般称它为scan def,配合下图,我们写出scan DEF语句来说明:

SCANCHAINS 1 ; scan chain数量

- chain0 scan chain名字+ START PIN scan_in scan chain起点+ FLOATING 代表着单独的寄存器单元,上图中out_reg_0,_1,_2,_3都是floating单元out_reg_0 ( IN SI ) ( OUT Q ) out_reg_1 ( IN SI ) ( OUT Q )

out_reg_2 ( IN SI ) ( OUT Q )out_reg_3 ( IN SI ) ( OUT Q )

+ ORDERED 需要放在一起的单元,上图中out_reg_4与u_buf就是ORDERED单元,用方框圈出out_reg_4 ( IN SI ) ( OUT Q )u_buf ( IN A ) ( OUT Y )+ STOP PIN scan_out ; scan chain终点END SCANCHAINS

概念都了解完以后,那我们后端到底需要对scan chain做些什么呢?

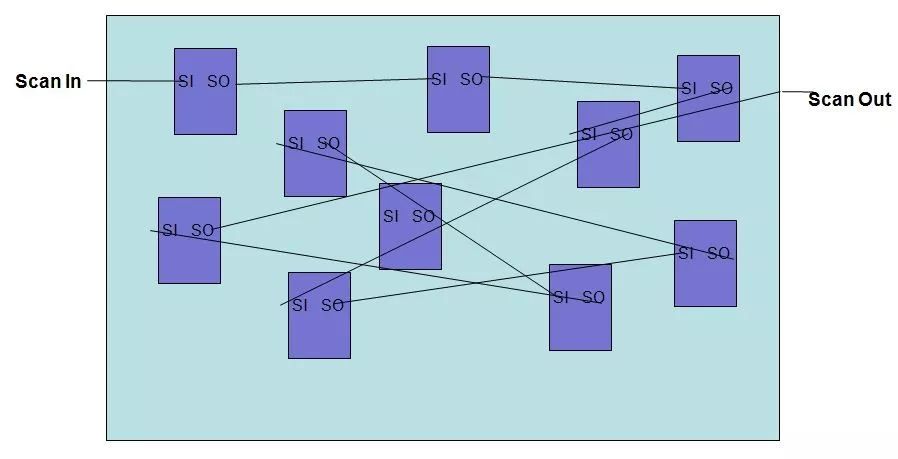

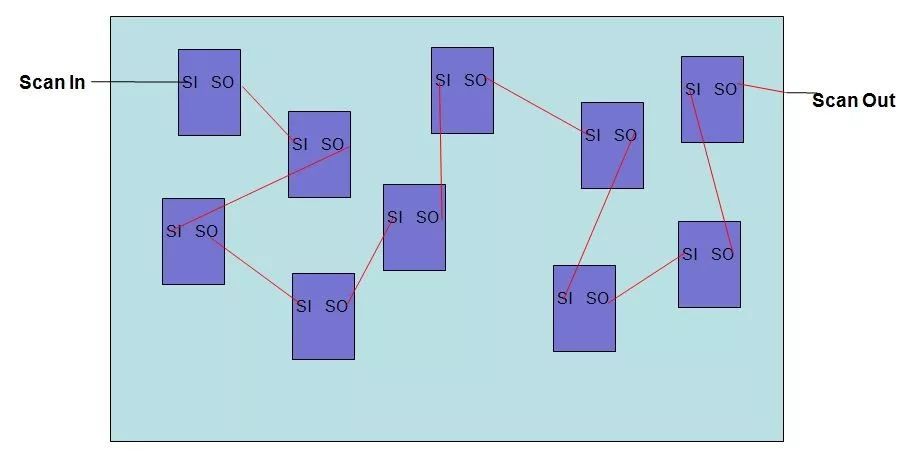

其实,在做完coarse placement后,Scan Cell大部分是按照连接的顺序随机的乱放的。这样其实会极大地占用绕线资源。因此,在后续步骤开始之前,我们希望对扫描链的连线进行处理,在不影响逻辑功能的前提下,重新进行连接,从而减少走线长度。那这个重组的过程,我们就称之为扫描链重组(Scan Reorder)。整个过程,可以用下面两张图来形象地说明:

Scan Reorder之前:可以看到,每个scan cell的连接得乱七八糟,专业术语叫做detour

Scan Reorder之后:仔细看,走线少了很多,也规整了不少吧!那这就是我们希望得到的结果~~(当然前提是不能影响逻辑功能)

如果用前文DEF的例子解释:

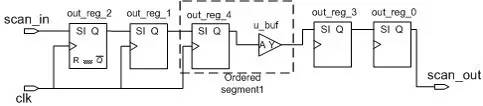

经过Scan Reorder之后,变成如下的电路连接:

可以看到,被方框圈住的out_reg_4和u_buf就类似一个整体一样,位置重新进行了排列。

那对应的Scan DEF信息变化就是:

左边的DEF格式前文已经说明,那右边reorder之后的大家能看懂嘛?

右边就多了一个#符号,这里可以理解为标志位,与着下面的#ORDERED segment 1相关联,就是为了说明它在FLOATING信息里的排列位置。

最后,我们可以使用report_scan_chains来报出scan chain的组成,使用check_scan_chain来检查其合理性

Checking Scan Chain scan_segment_88

STOP: u__noram/u_etm/u_fifo/ts_0_lockLD_865264

....

thru: u_noram/uersistent_cell_0_buf_intsi54506_i/Z

STATUS: VALIDATED, Sequential Length = 524, Instance Count = 524, Partition = partition_1

-

DFT

+关注

关注

2文章

232浏览量

22973 -

时序

+关注

关注

5文章

392浏览量

37538

原文标题:剪断了,理就不会乱——Scan Reorder

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序分析基本概念介绍——花一样的“模式”

时序分析基本概念介绍——花一样的“模式”

评论