本设计实例探讨了分辨率更高、位数更少的三进制DAC。尽管精确的三进制DAC实现可能要比普通的二进制DAC更困难 (特别在分辨率提高时困难更大),但五个三态位 (35=243) 本质上就可与常规八个两态位 (28=256) 性能相近。与所有简单的DAC设计一样,三态 DAC电源噪声也会传递到输出端。

当EDN忠实读者和设计实例栏目的投稿人Jim Brannan提出要写一篇关于三进制DAC设计的文章时,我感到非常高兴。像Charlieplexing(一种采用较少管脚驱动多路复用显示的技术)一样,他的想法是利用三态输出以便从一个管脚上获取更多信息,而不仅仅是“0”和“1”。例如,对于一个三态的四位DAC,理论上能够产生81(34)种输出值,而不是通常(两态)的16(24)种。而三态的五位DAC(35=243)本质上与常规的两态八位(28=256)性能相近,尽管精确的三进制DAC实现可能要比普通的二进制DAC更困难,特别是分辨率的提高带来更大的困难。

一如既往,我先Google是否有类似的创意想法。果然,找到了两页描述类似设计的文献。Jim也看了,他觉得没啥可补充的。所以,设计创意的文章也就搁浅了。但我觉得这个创意无论如何都值得说一下。另外,Jim的方法确有独到之处。

在开始之前,或许该花点时间想一下你自己会如何构思一个三态DAC。在下面的想法占领你的大脑前,也许你会另辟蹊径,想出一种新方法。

*************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************************

好吧,这是我自己的实现思路:

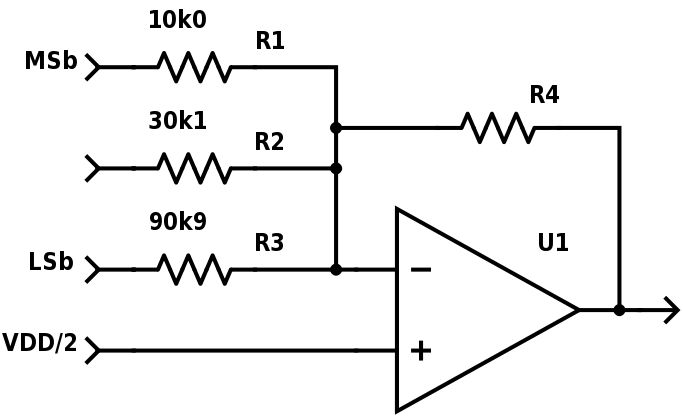

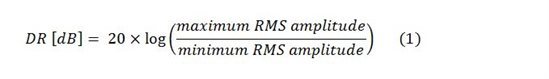

图1:采用带中间电源参考的加法放大器实现三进制 DAC。

实际上,我最初的想法是将放大器的(+)输入设置为-VDD,但后来我意识到浮动输出会被拉向负电源,可能会钳位在-0.7V,且通常无法工作。VDD/2参考表示0、1、2状态,对应于0、Z、1输出值(“Z”表示高阻抗和/或输入模式)。

另一个硬件问题是,当输入处于中间电压轨时,某些微控制器可能会吸收过多的供电电流,因此要确认这不会出问题。要禁用数字输入模式,或使用可设置为模拟输入的引脚。

驱动三进制DAC需要一个查找表,或从二进制到三进制的转换程序。在大多数情况下,除非在一个写周期内设置好引脚模式和值,否则DAC输出将在其设置发生改变时产生毛刺现象。

被Jim放弃的设计想法使用无源“R-2R”类型的DAC,他写了用于搜索许多阻值组合的软件。意识到无法创建一款完美的线性DAC,他的方案是使用查找表,DAC的表现有些不平衡也就只好接受了。

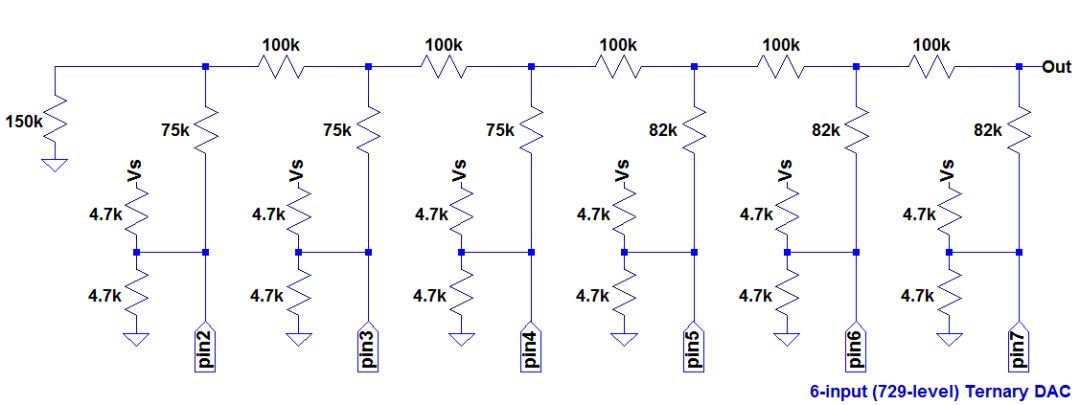

在Josh Bowman的博客中,他描述了自己对三进制DAC的构想。它采用一种类R-2R结构,用较低值的电阻将电源分压以产生中间电平的“Z”值。

图2: Josh Bowman的无源三进制DAC。

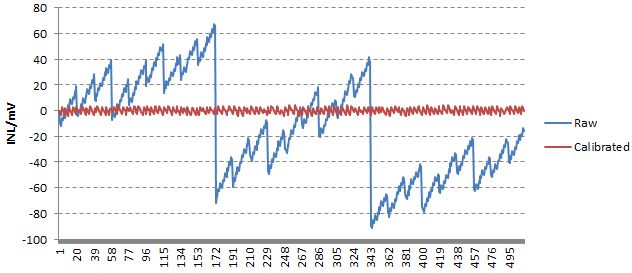

正如你在下面看到的,设计中有冗余的值,可用来进行校准。

图3:原始和校准过的积分非线性(INL)性能。

在Arduino论坛上也有几个关于三进制DAC设计的讨论,感兴趣可以去看看。

如果你对三进制DAC设计实现有自己的想法,请在写下你的经验。我们很乐意倾听你的分享。请记住,与所有这些简单的DAC设计一样,三态DAC电源噪声也会传递到输出端。

《电子技术设计》2018年4月刊版权所有,转载请注明来源及链接。

-

电源

+关注

关注

185文章

17886浏览量

252317 -

dac

+关注

关注

43文章

2315浏览量

191788

原文标题:三进制DAC:分辨率更高,位数更少

文章出处:【微信号:edn-china,微信公众号:EDN电子技术设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EVAL_PASCO2_SENSOR为什么无法从较低的分辨率高速获得更高的分辨率?

ADC的噪声、ENOB及有效分辨率

请问24位的分辨率是否是所有ADC的极限?

RF成像分辨率怎么提高

如何实现更高的分辨率或更窄的RBW测量?

如何使用gstreamer获得更高的分辨率?

峰峰值分辨率与有效分辨率的区别

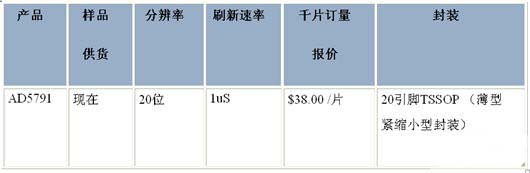

ADI推出分辨率+精度1ppm DAC

峰峰值分辨率与有效分辨率

分辨率的峰值分辨率和有效分辨率概念

ADC 的分辨率位数和有效分辨率哪个更重要

探讨分辨率更高、位数更少的三进制DAC

探讨分辨率更高、位数更少的三进制DAC

评论