下面我们来简单地聊一聊定点小数的常规格式、相对于浮点小数的优势与劣势,以及如何使用Lattice ECP3/ECP5的sysDSP乘法器来实现基本的定点小数运算(加法和乘法)。并会在后续的文章中介绍定点小数的除法、平方根、平方根倒数和CORDIC算法的基本理论和HDL的实现等。

1.定点小数的常规格式

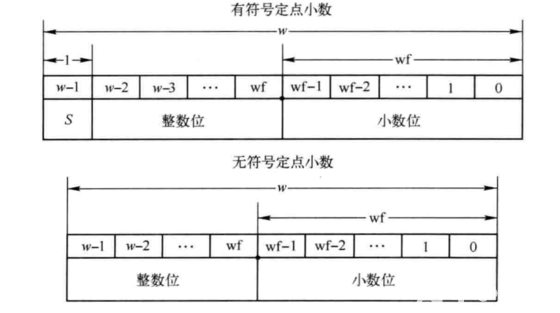

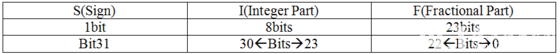

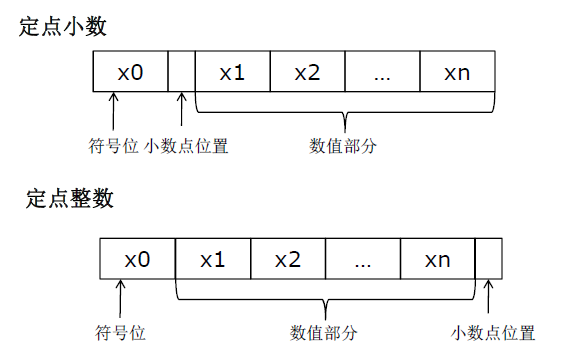

常规的定点小数格式如下图:

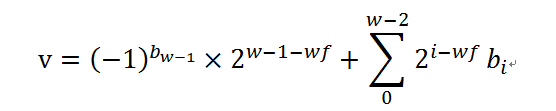

其中,有符号定点小数的值可以表示为:

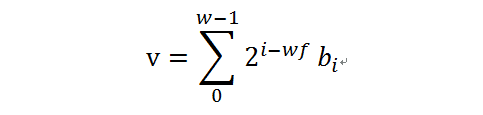

无符号定点小数的值可以表示为:

定点数的位宽w和小数部分的位宽wf可以看做是定点数的两个要素。其中,w决定了定点数的动态范围,wf决定了定点数的精度。需要注意的是,在进行定点数运算的时候,需要注意数值溢出的问题(包括向上溢出和向下溢出)。所谓向上溢出是指运算结果超出了定点数整数部分所能表示的范围,向下溢出表示运算结果超出了定点数小数部分所能表示的范围。显然,一旦溢出将会造成计算精度的丢失,甚至是计算结果的错误。因此,合理地选择w和wf至关重要,w和wf的值过大会浪费资源,过小又会造成精度丢失。

2.定点数与浮点数的比较

与浮点数相比,定点数具有如下的一些优势:

(1)更少的资源

通常在FPGA中进行浮点运算时,会消耗更多的LUT、寄存器和乘法器。定点数由于不需要存储小数点的位置,所以定点数的运算消耗的资源基本上和同样位宽的整数运算相当,远远低于浮点运算的开销。

(2)更高的性能

浮点运算在消耗更多资源的同时,也会给MAP和PAR带来压力,从而导致整个设计的Fmax降低。在同样规模的运算量下,采用定点数的设计则可以获得更高的Fmax。

与此同时,相对于浮点数,定点数也有很多的缺陷和不足:

(1)能够表示数值的动态范围较小

(2)数值溢出的问题

浮点数由于采用了统一的格式(IEEE-754),且动态范围很大,因此基本不存在数值溢出的问题。但是定点数则需要程序设计中合理地选取w和wf的值,并且没有统一的格式规范也为复杂程序的协同设计带来麻烦。

从应用的需求来看,很多场合下,采用定点数即可满足系统的性能需求,但是也有一些场合对精度的要求很高,如雷达成像,医学成像,高精度数据采集与分析等则需要采用浮点数进行运算。

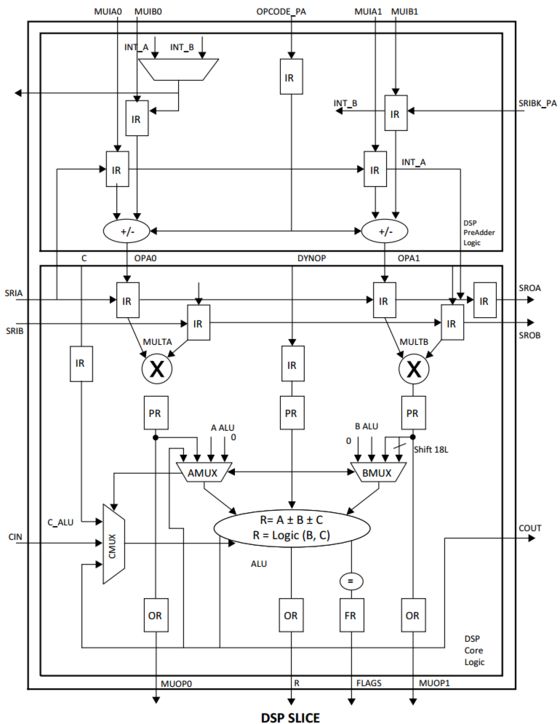

3.ECP3/ECP5 中的sysDSP乘法器

Lattice的ECP3/ECP5系列FPGA内部集成了多个sysDSP架构的乘法器模块,基于sysDSP,用户可以便捷地设计出低功耗高性能的数字信号处理应用。相比于用LUT实现的乘法器,基于sysDSP的乘法器具有显著的性能优势。此外,Lattice还提供了多种基于sysDSP的IP,如FFT、FIR和CIC等。

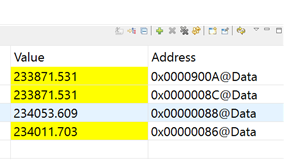

ECP5中sysDSP的Slice结构图如下图所示:

4.定点小数的加法与乘法

定点小数的加法与乘法运算基本上和普通整数的加法与乘法一致,但是需要注意运算结果的w和wf的与原值的w和wf之间的对应关系。

下面来举一个简单的例子:两个32位的有符号定点小数相乘,其中w=32,wf=23。即

此时,

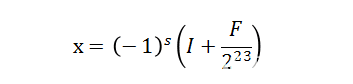

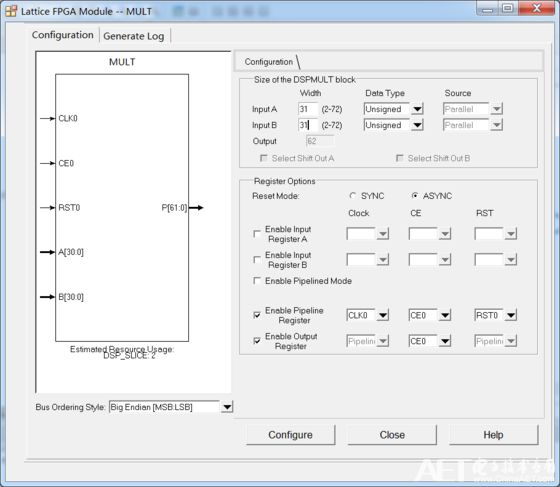

我们可以直接使用Clarity来生成整除乘法器的Module,如下图所示。其中符号位可以提取出来进行异或操作,剩余的31位进行乘法运算。

如果需将运算结果也转换为和输入相同的格式,则可以进行如下的操作:

上面的例子,是将有符号数转换为无符号数,再进行运算的(即采用原码直接运算的)。实际上,我们还可以直接将MULT的Module中的Data Type配置为Signed,此时操作数将以补码的形式进行运算。

-

FPGA

+关注

关注

1635文章

21837浏览量

608343 -

乘法器

+关注

关注

9文章

207浏览量

37386

原文标题:【精选博文】FPGA定点小数计算(一)

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浮点处理器相对于定点处理器有何不同

第7章 DSP定点数和浮点数

基于牛顿迭代法的FPGA定点小数计算

IEEE 754标准浮点格式可分为哪几种

定点小数的编码方法

IEEE754浮点数格式

LM4F定点格式于浮点格式的对比和浮点运算的应用详细中文资料

FPGA定点小数的常规格式、相对于浮点小数的优势与劣势和计算的概述

FPGA定点小数的常规格式、相对于浮点小数的优势与劣势

FPGA定点小数的常规格式、相对于浮点小数的优势与劣势

评论