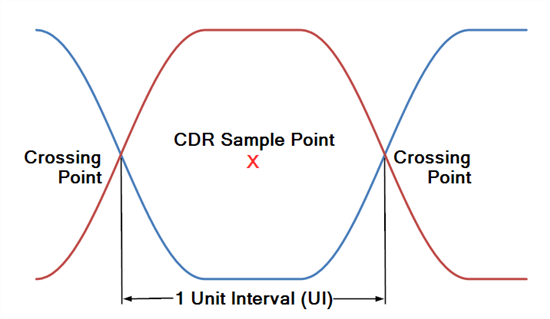

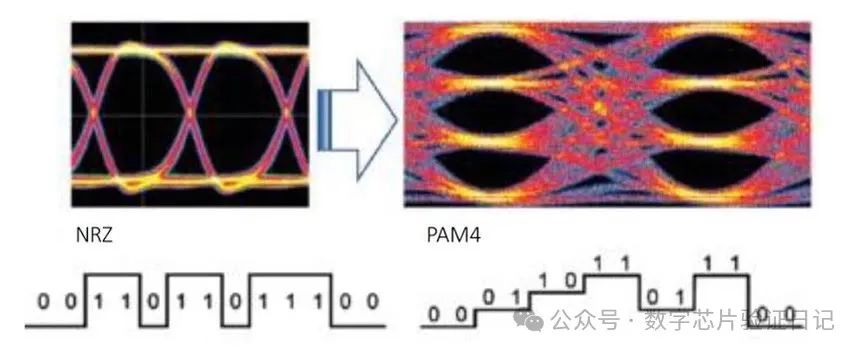

要理解抖动,我们首先要了解眼状图。眼状图是数字信号在时域中的表现形式,其中电压振幅按时间变化绘制。一长串数据可分割成多个片段,称之为单位间隔 (UI),这些 UI 在示波器上一个个叠加,有助于示波器一次显示极大数量的数据。单位间隔定义为 UI = 1/比特速率。如图 1 中眼状图所示。一个眼状图由 1 个 UI 组成(工程师有时会绘制两个并排眼状图),它是数字信号质量的视觉体现。

图 1

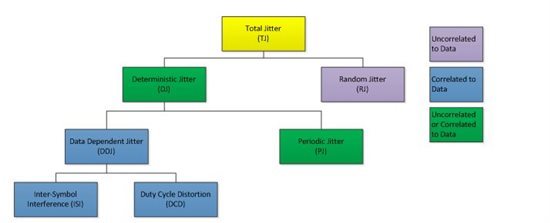

既然我们了解了眼状图,就可提出这样一个问题“什么是抖动?”抖动可定义为不希望看到的、信号理想转换位置的高频率偏移。抖动可分为总体抖动 (TJ)、随机抖动 (RJ) 和确定性抖动 (DJ)。顾名思义,总体抖动 (TJ) 包含所有抖动组成部分的影响。下图 2 中的流程图是 TJ 及其所有组件的分解图:

图 2

如欲了解有关 TJ 的更多详情,敬请查看应用手册《如何测量总体抖动》。

RJ 是不可预测的,而且通过随机过程不断积累,其中包括但不仅限于热噪声、散粒噪声与电源噪声。RJ 不受限制,因此其测量值会随时间推移持续增大。

DJ 是可预测的抖动,因为它与所传输的数据类型以及传输媒介有关。DJ 具有非高斯概率密度分布函数,而且是有界限的,因此其测量值会随时间推移增加到某一点,但不会无限增大。DJ 包含几个组成部分,其中包括数据相关抖动 (DDJ)、占空比失真 (DCD)、码间串扰 (ISI) 与周期性抖动 (PJ)。

码间串扰 (ISI) 是所选传输媒介内带宽不足的产物。PCB 迹线或线缆可作为低通滤波器 (LPF) 衰减数据信号中的高频率内容。这会引起电压失调和不均衡数据模式,如果处理不当最终会导致位错误。占空比失真 (DCD) 是升降时间不等的结果,其可导致具有不同持续时间的 1 和 0,引起阀值交点偏移。数据相关抖动 (DDJ) 是与数据模式有关的抖动,由带宽限制 (ISI) 和阀值交点偏移 (DCD) 的总和效应引起。对于 DDJ 而言,之前传输的数据位会给当前数据位状态产生负面影响。周期性抖动 (PJ) 是按周期形式重复的抖动,不包含数据相关性抖动组成部分。PJ 可以是任何具有周期性特性的边缘偏移。有一种 PJ 叫做正弦曲线抖动 (SJ),因为它可分解成谐波相关正弦曲线的傅里叶级数。PJ 一般由外部确定性噪声源引起,该噪声源通过开关电源、串扰或不稳定时钟恢复 PLL 耦合在我们的系统中。当然,可通过每个抖动成分了解更多信息,我建议大家对其进行深入挖掘,真正理解抖动及其组分。

ISI 抖动是传输媒介带宽的函数,因此可通过设计进行补偿。如果背板或线缆传输路径出现大量 ISI 抖动,可使用 SN65LVCP1414 线性均衡器和 SN65LVCP114 线性四通道多路复用器均衡器等器件来对通道的 LPF 效应进行逆向处理。这些器件可为您的系统补偿高达 17dB 的损耗,从而可通过减少整体抖动来扩展通道范围。

-

眼图测量

+关注

关注

0文章

4浏览量

8838 -

信号抖动

+关注

关注

1文章

4浏览量

9168

发布评论请先 登录

相关推荐

txs0102使用中遇到的高电平是什么引起的?怎么解决?

高电平输入和低电平输入是什么意思

rca输出是低电平还是高电平

双色led灯的引脚为高电平还是低电平

如何解决交流接触器出现异常抖动问题

芯片引脚悬空是高电平还是低电平

高电平和低电平输入有什么区别

高速信号传输中的抖动和眼图挑战

从眼状图入手,了解高电平抖动问题

从眼状图入手,了解高电平抖动问题

评论