超级结MOSFET开关速度和导通损耗问题:

超级结技术是专为配备600V以上击穿电压的高压功率半导体器件而开发的,该技术已用于改善导通电阻与击穿电压之间的制衡。采用超级结技术有助于降低导通电阻并提高MOSFET的开关速度。但随着MOSFET开关速度的加快,封装中的源级连接电感产生反电势,开始对开关速度产生不利的影响,导通损耗随之变大。

通过TO-247-4L封装来解决这些问题:

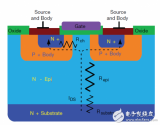

采用TO-247-4L封装的超级结MOSFET可以解决这一问题。4引脚TO-247-4L封装具有栅极驱动回路的开尔文源极连接,可以降低内部源级连接电感的影响。因此,超级结MOSFET与4引脚TO-247-4L封装组合是高速应用的理想之选。

利用仿真技术分析TO-247-4L封装的机制

东芝利用SPICE仿真技术分析了4引脚TO-247-4L封装的机制。经验证,3引脚TO-247封装中产生的反电动势VLS并未在4引脚TO-247-4L封装中产生。4引脚TO-247-4L封装的栅极开关速度比3引脚TO-247封装的栅极开关速度快。因此,4引脚TO-247-4L封装有助于提高MOSFET开关速度和降低导通损耗,关断后还有助于抑制栅极振荡。

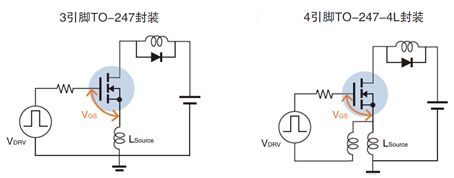

我们采用了相同的MOSFET器件模型对4引脚TO-247-4L封装和3引脚TO-247封装进行仿真。将源极引线分成两部分,然后将这两部分分别连接至栅极和漏极,从而对4引脚TO-247-4L封装进行建模,下面是3引脚TO-247封装和4引脚TO-247-4L封装的仿真模型。

TO-247-4L封装有助于提高MOSFET开关速度

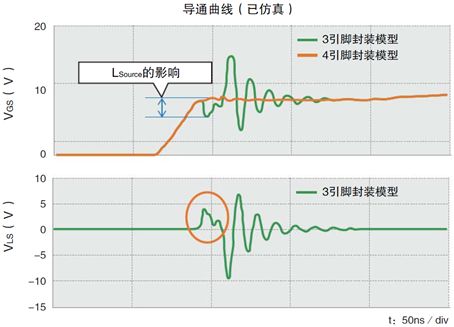

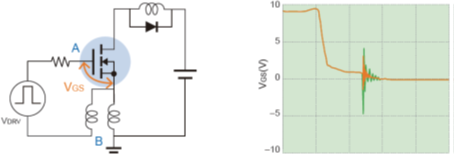

利用仿真技术验证了由于源极LSource生成反电动势VLS,通过MOSFET的电压并不等于全部的驱动电压VDRV。MOSFET导通时3引脚封装的反电动势VLS、栅极-源极VGS波形如下图所示。图中用圆圈突出显示的部分是LSource的实际电压。该电压降低了通过栅极和源极的电压。因此,如3引脚封装的VGS波形所示,导通后栅极电压下降,降低了导通速度。而在4引脚封装中,通过MOSFET的VGS电压几乎等于VDRV。因此,与3引脚封装相比,4引脚封装更有助于提高MOSFET开关速度。

TO-247-4L封装可以降低导通损耗

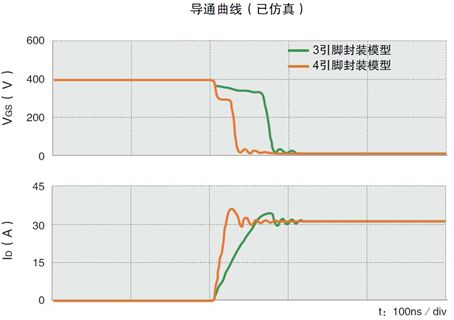

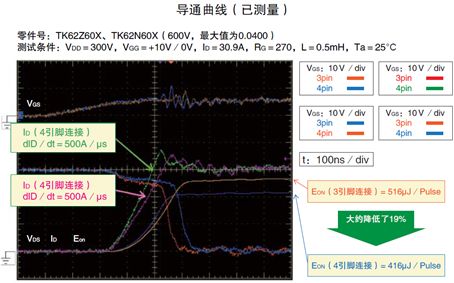

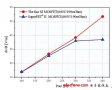

我们通过仿真和实际测量数据还验证了使用TO-247-4L封装有助于降低导通损耗。下图显示了通过仿真和实际测量得出的漏极-源极电压(VDS)和漏极电流(ID)。根据使用3引脚和4引脚模型得出的仿真结果推断,4引脚封装的开关速度更快。此外,我们还借助实际测量结果对具有同样额定电流的3引脚封装TK62N60X和4引脚封装TK62Z60X进行了对比。结果证实,4引脚封装比3引脚封装的开关速度更快。导通损耗因提高开关速度降低了19%。

关断TO-247-4L封装有助于抑制栅极振荡

关断TO-247-4L封装有助于抑制栅极振荡TO-247-4L封装除了可以降低导通损耗之外,关断后还有助于抑制栅极振荡。下图显示仿真结果,其展示MOSFET关断时的VGS波形,VGS指4引脚TO-247-4L封装电路中A和B间的电压,4引脚封装比3引脚封装的栅极振荡幅度更小。

东芝利用仿真技术分析了4引脚TO-247-4L封装的机制并验证,3引脚TO-247封装中产生的反电动势并未在4引脚TO-247-4L封装中产生,4引脚TO-247-4L封装的开关速度快,可以使导通损耗降低19%。仿真结果还显示,采用4引脚TO-247-4L封装可以抑制栅极振荡。

-

MOSFET

+关注

关注

146文章

7095浏览量

212748 -

封装

+关注

关注

126文章

7789浏览量

142734 -

栅极驱动

+关注

关注

8文章

184浏览量

23112

原文标题:采用TO-247-4L封装可以提高MOSFET开关速度和降低导通损耗

文章出处:【微信号:toshiba_semicon,微信公众号:东芝半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何优化PCB设计以最大限度提高超级结MOSFET的性能

功率MOSFET的开关损耗:开通损耗

功率MOSFET的开关损耗:关断损耗

三分钟读懂超级结MOSFET

超级结MOSFET的优势

超级结MOSFET

高耐压超级结MOSFET的种类与特征

EN系列可保持低导通电阻与开关速度,改善噪声性能

罗姆新品|低噪声,低导通电阻,600V 超级结MOSFET PrestoMOS “R60xxJNx系列”

罗姆新品|低噪声,低导通电阻,600V 超级结MOSFET PrestoMOS “R60xxJNx系列”

导通损耗和关断损耗的相关资料推荐

理解MOSFET开关损耗和主导参数

讨论在PFC中应用的新型超级结MOSFET器件的特点

MOSFET开关损耗分析

理解超级结技术

超级结MOSFET开关速度和导通损耗问题

超级结MOSFET开关速度和导通损耗问题

评论