FPGA对绝大多数的人来说相对有些陌生。经常有朋友问我,你们成天搞的这个FPGA到底是什么东西。

我想很难用一两句通俗易懂的语言解释什么是FPGA,因为当今的FPGA已经是一个非常复杂的系统了。打个比喻来说,对于热爱乐高的人来说FPGA设计就像搭积木,对于爱涂鸦的我来说FPGA就像是一张精密的画布。借助赛灵思这样的FPGA厂商提供给设计师的易用的“画笔”,有创意的设计师就能根据需求创作自己心仪的作品。

那么这张画布有什么好处呢?且听我 一 一 道来:

易用性:对“画家”来说,FPGA令人生畏的地方,就是只有“硬件工程师使用”的硬件可编程模式。硬件描述语言虽然硬件发展了30多年,但是由于HDL是一种用形式化的语言描述极其复杂的数字系统的,抽象级别较低,因而大大提高了编程难度,限制了FPGA的推广和普及。其次随着系统级FPGA和片上系统(SoC)的出现和迅速发展,FPGA开发已不再单单只是一个模块的“编程”工作。系统设计,软硬件协同设计变得越来越重要,这也大大提高了“准入”门槛。

然而,“山穷水复疑无路,柳暗花明又一村” 觊觎 FPGA 的优势又苦于无法不会使用的软件和系统工程师们, 现在可以再次把FPGA 开发提到日程上来了, 因为赛灵思在解决“易用性”问题上已经迈出了几大步,其中包括:

赛灵思2012年就发布了Vivado设计套件集成环境,大大简化了FPGA 的开发流程,使画家的画笔更好用更易用。

HLS (High level Synthesis,高层次综合)工具给“画家”提供了新的画笔——可以直接用抽象级别更高的c/c++进行硬件编程。

SDSoC(Software Defined SoC)顾名思义,软件定义的SoC。它赋予了系统设计极高的灵活性,将设计灵活地在PS(ARM processor)/PL(可编程逻辑)进行分配。

System Generator作为matlab/simulink的插件,使算法仿真和FPGA设计进行bit级的无缝连接。

还有最近 赛灵思最近推出的又一力作Module Composer,极大地提高了算法仿真速度,并降低了在FPGA上实现复杂算法的门槛。

当然,赛灵思新的 CEO 在3月19日刚刚发布的ACAP (自适应计算加速平台)这个超越 FPGA 的新型产品,更是为 FPGA 在软件和算法工程师中的普及描绘了一个美好的蓝图。

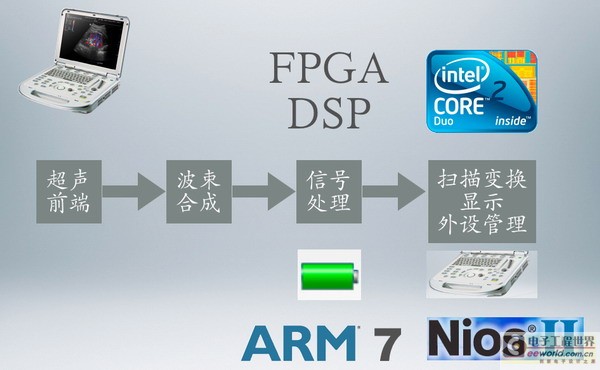

系统级:当今 FPGA 技术飞速发展,FPGA 早已经不是只能做 glue logic(胶合逻辑)或者 I/O 连接的硬件电路的一部分了。FPGA 越来越成为开发各种应用的系统中最核心的一部分了。除了PL(可编程逻辑),赛灵思还集成了 PS(ARM processor),以及各种高性能的硬核。2017年,我想业内最爆炸的新闻莫过于“Xilinx公布了基于16nm工艺的Zynq UltraScale + RFSoC 产品系列”。Xilinx 将高性能的 ADC/DAC 集成在 FPGA 中,这就相当于赛灵思 FPGA 不仅提供了精密的画布还提供了华美的边框,用户不再需要额外布置片外的 ADC/DAC 芯片和相应的模拟电路,就可以在数字与模拟之间自由切换。这个创举不仅在功耗/成本/面积上带来巨大的优势,还给用户(设计者)带来了极大的方便。(FPGA工程师轻呼一口气,终于可以扔掉恼人的 JESD 了)

功耗:如果对某个成熟的算法或者技术,已经有某种成熟的ASIC可以满足需求,我就不建议考虑FPGA了。因为无论是价格还是功耗,FPGA都可能略逊一筹。但是对于那些喜欢与众不同,喜欢用差异化甩开竞争对手, 并希望自己的设计能够与时俱进、灵活应变的企业,FPGA就是你最佳的选择。

随着科技的飞速发展,技术的更新迭代,昨天成熟的技术今天可能就已经过时了,这正是可重配置的“万能”芯片FPGA 的时代。当然, 如前所述,当今的FPGA是一个片上的系统,如果从整体系统的角度来看,FPGA在性能功耗比上无疑都有着巨大的优势。

总之,同十年前相比,FPGA的开发和使用的难度已经大大降低了。赛灵思已经不再满足于只向用户提供业界最领先的“画布”,它还提供了一整套的生态环境和解决方案,力争使设计者玩FPGA玩出乐高乐趣,玩出大师级画家的精彩。 通过简单的“插”“拔”,使用户更容易的完成系统级的masterpiece。

-

dsp

+关注

关注

554文章

8060浏览量

350859 -

FPGA

+关注

关注

1631文章

21806浏览量

606686

发布评论请先 登录

相关推荐

医疗电子平台选择:FPGA、ARM、X86、DSP还是GPU

选择赛灵思(Xilinx)FPGA芯片的N个理由

选择赛灵思(Xilinx)FPGA 7系列芯片的N个理由

大点数FFT运算选择FPGA还是DSP?

FPGA就像是一张精密的画布 - DSP 专家给你一个选择 FPGA 的理由

FPGA就像是一张精密的画布 - DSP 专家给你一个选择 FPGA 的理由

FPGA构建高性能DSP

DSP专家给你一个选择FPGA的理由

DSP专家给你一个选择FPGA的理由

评论