信号的上升时间,对于理解信号完整性问题至关重要,高速pcb设计中的绝大多数问题都和它有关,很多信号完整性问题都是由信号上升时间短引起的,你必须对他足够重视。

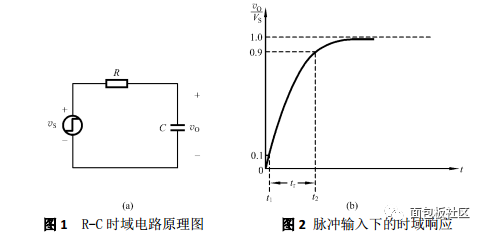

信号上升时间并不是信号从低电平上升到高电平所经历的时间,而是其中的一部分。对于信号上升时间通常有两种:

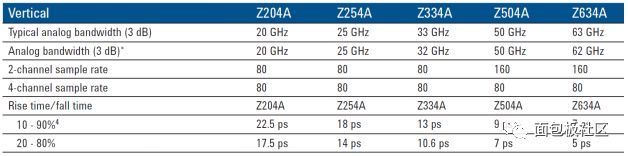

第一种定义为10-90上升时间,即信号从高电平的10%上升到90%所经历的时间。另一种是20-80上升时间,即信号从高电平的20%上升到80%所经历的时间。两种都被采用。

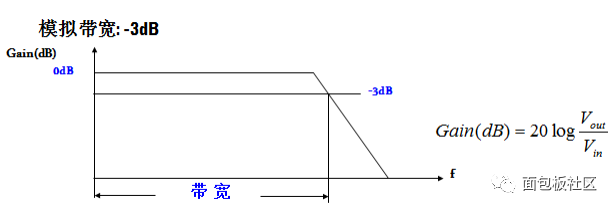

带宽是指被测信号幅值衰减到0.707倍时对应的频带宽度。幅度的平方即为功率,平方后为0.5倍,带宽也即功率衰减到一半时的频带宽度。

重要的是我们必须建立这样的概念:上升时间对电路性能有重要的影响,只要小到某一范围,就必须引起注意,哪怕是一个很模糊的范围。没有必要精确定义这个范围标准,也没有实际意义。因此只需记住,现在的芯片加工工艺使得这个时间很短,已经到了ps级,你应该重视他的影响的时候了。

随着信号上升时间的减小,反射、串扰、轨道塌陷、电磁辐射、地弹等问题变得更严重,噪声问题更难于解决。

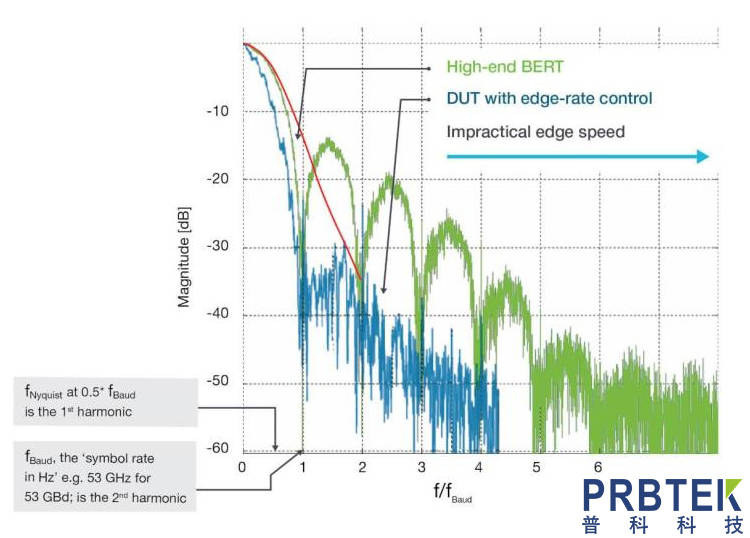

信号上升时间的减小,从频谱分析的角度来说,相当于信号带宽的增加,也就是信号中有更多的高频分量,正是这些高频分量才使得设计变得困难。互连线必须作为传输线来对待,从而产生了很多以前没有的问题。因此,学习信号完整性,你必须有这样的概念:信号陡峭的上升沿,是产生信号完整性问题的罪魁祸首。

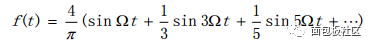

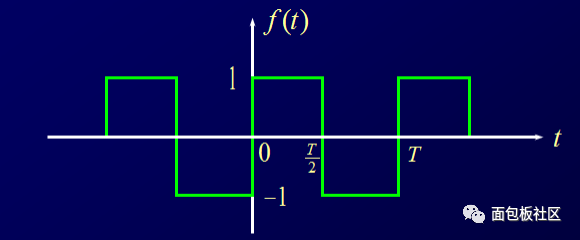

对于数字电路,输出的通常是方波信号。方波的上升边沿非常陡峭,根据傅立叶分析,任何信号都可以分解成一系列不同频率的正弦信号,方波中包含了非常丰富的频谱成分。如下图周期性方波信号的傅里叶级数展开为

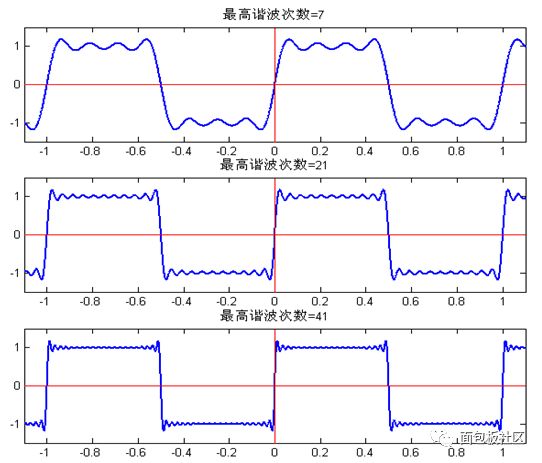

可以用实验来直观的分析方波中的频率成分,看看不同频率的正弦信号是如何叠加成为方波的。下图是7次谐波合成的波形,21次谐波合成的波形以及41次谐波合成的波形。这里可以直观的看到:叠加的谐波成分越多,波形就越像方波。

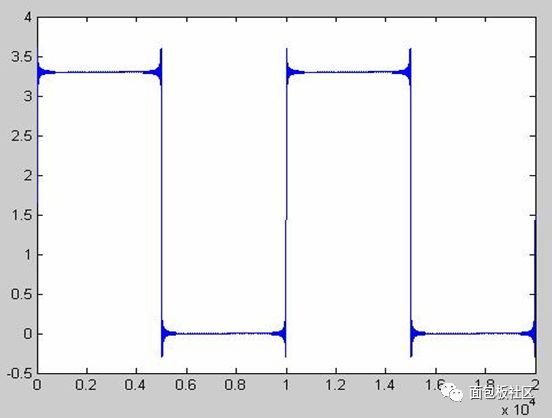

因此如果叠加足够多的谐波,我们就可以近似的合成出方波。下图是叠加到217次谐波后的波形。已经非常近似方波了,不用关心角上的那些毛刺,那是著名的吉博斯现象,这种仿真必然会有的,但不影响对问题的理解。这里我们叠加谐波的最高频率达到了21.7GHz。

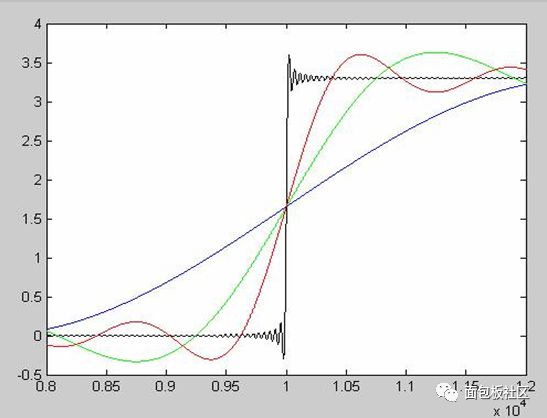

在通过下图我们可以看到,谐波分量越多,上升沿越陡峭。或从另一个角度说,如果信号的上升边沿很陡峭,上升时间很短,那该信号的带宽就很宽。上升时间越短,信号的带宽越宽。红色是基频+3次谐波+5次谐波+7次谐波后的上升边沿,黑色是一直叠加到217次谐波后的波形上升边沿。

这里说一下,最终合成的方波,其波形重复频率就是100MHz。叠加谐波只是改变了信号上升时间。信号上升时间和100MHz这个频率无关,换成50MHz也是同样的规律。如果你的电路板输出数据信号只是几十MHz,你可能会不在意信号完整性问题。但这时你想想信号由于上升时间很短,频谱中的那些高频谐波会有什么影响?

记住一个重要的结论:影响信号完整性的不是波形的重复频率,而是信号的上升时间。

-

带宽

+关注

关注

3文章

926浏览量

40913 -

信号

+关注

关注

11文章

2789浏览量

76730

原文标题:深入理解信号上升沿与带宽的关系

文章出处:【微信号:gh_bee81f890fc1,微信公众号:面包板社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

傅立叶变换与时域信号的关系 傅立叶变换在音频信号处理中的应用

弹性公网ip和带宽价格有关系吗?

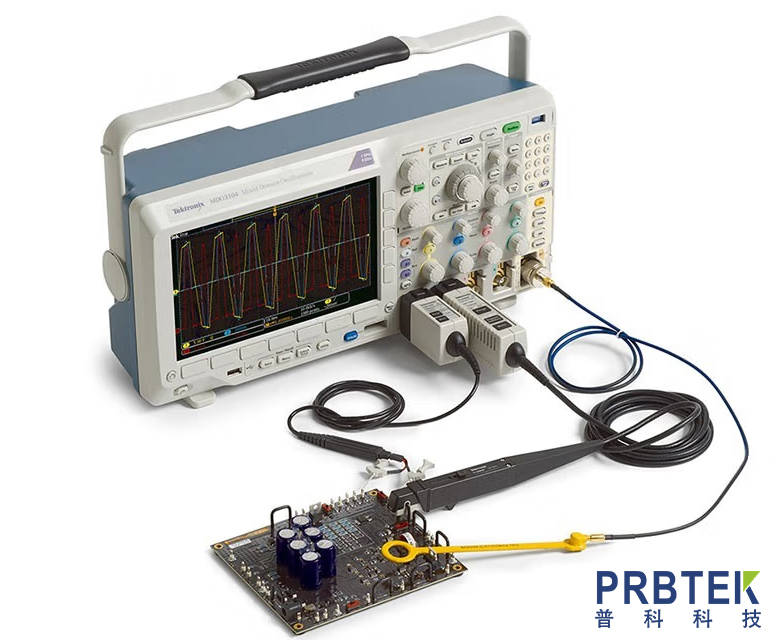

如何根据信号的频率特性选择合适的示波器带宽?

请问闭环带宽,信号带宽分别是什么意思?

测量串行数据信号:选择合适的示波器带宽

信号的时域波形和频谱间的关系是什么

频谱仪分辨率带宽和视频带宽的关系

信号的时域波形和频谱间的关系

示波器带宽与采样率的关系

浅谈示波器电压探头的带宽和上升时间

一文读懂宽带、带宽、网速之间的区别与关系

示波器带宽与探头带宽的关系揭秘

深入明白信号上升与带宽的关系

深入明白信号上升与带宽的关系

评论