AD版本要用AD6.9的,AD9不行,另存时会有错误,步骤如下:

工程师的巨大福利,首款P_C_B分析软件,点击免费领取

1.直接建一个只有原理图的项目。

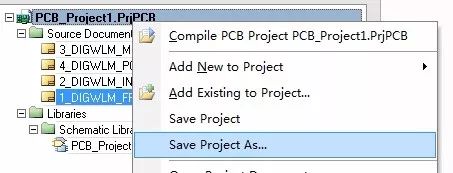

2.另存为OrCAD (.dsn)项目。如下图:

另存

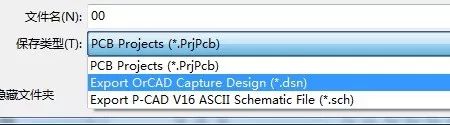

选择OrCAD格式

3.用Capture 打开保存的DSN文件即可。打开时会等一会,原理图尺寸大的会等的久一点。

4.注意点:原理图尺寸不能太大张,原理图尺寸在A3或A3以下转出来比较好,太大张会出现器件丢失的现象。小尺寸会也会出现小问题,如,器件错位,一般是电阻电容类会有错位。我估计是AD原理图用的同一类器件时引用的库不一样引起的。

二.AD原理图库转OrCAD原理图库

步骤如下:

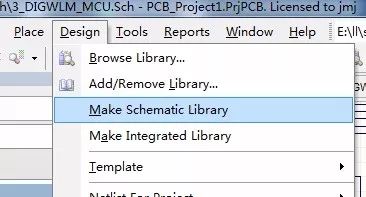

1.先在AD原理图导出AD 的原理图库,如果本来就有原理图库可以不用导出。

打开有原理图的工程,菜单命令:Design => Make Schematic Library

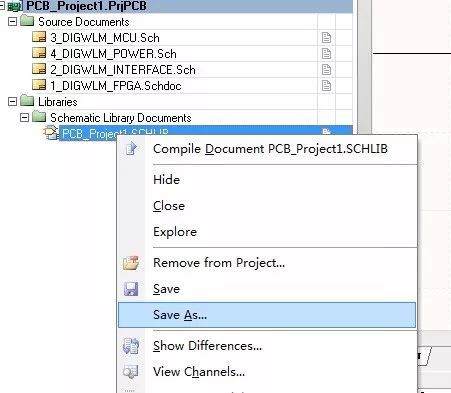

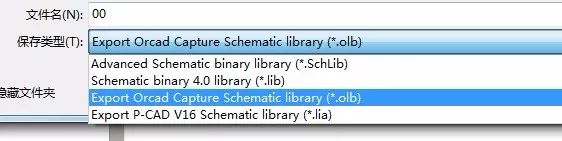

2.另存为OrCAD 格式的库文件

另存

选择OrCAD格式库文件

3.另存后直接用Capture打开即可

4.注意:AD原理图库转OrCAD原理图库时,AD版本没有要求,我试了AD6.9和AD9都可以。

三.AD PCB封装转Allegro封装或者AD PCB转Allegro PCB.

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把PCB转成ALLEGRO格式的,然后再用ALLEGRO导出PCB封装

步骤如下:

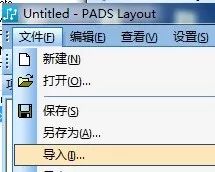

1.用PADS Layout (PADSVX.0)直接导入AD格式的PCB

导入

选择AD格式的PCB

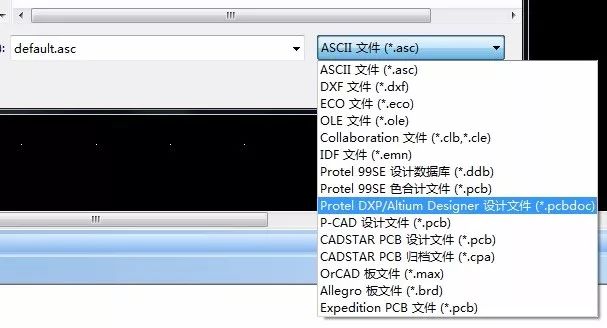

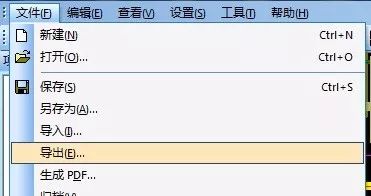

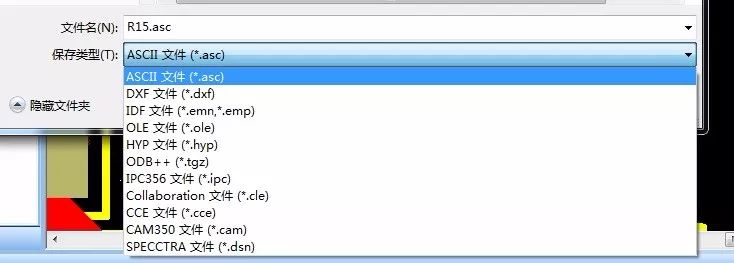

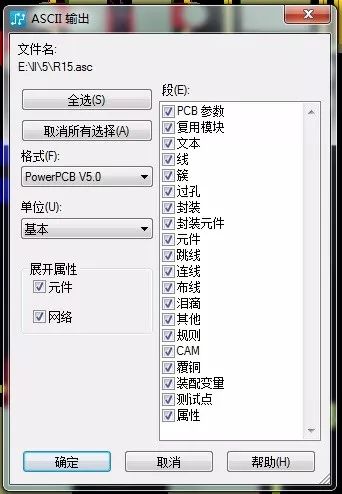

2. PADS Layout (PADSVX.0)导出ASCII文件(*.asc)

导出

选择导出ASCII文件(*.asc)

ASCII选项如上图,格式可选Power PCBV3.0 到V5.0,以及PADS Layout9.3以下版本都可以。

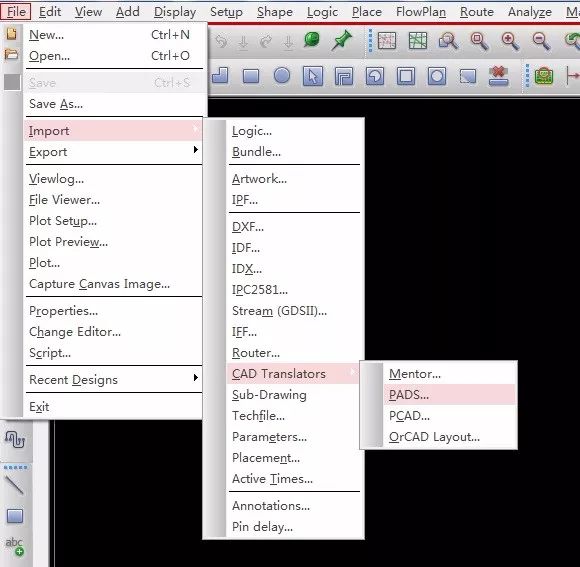

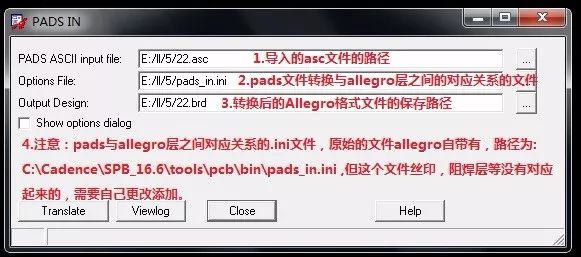

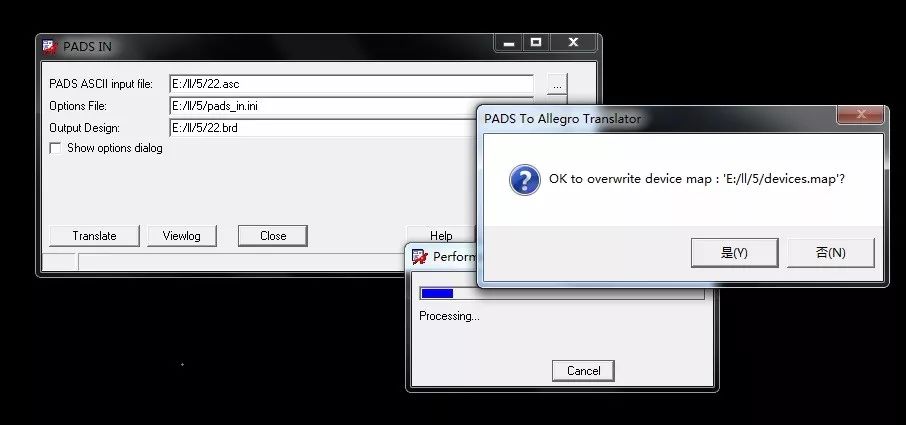

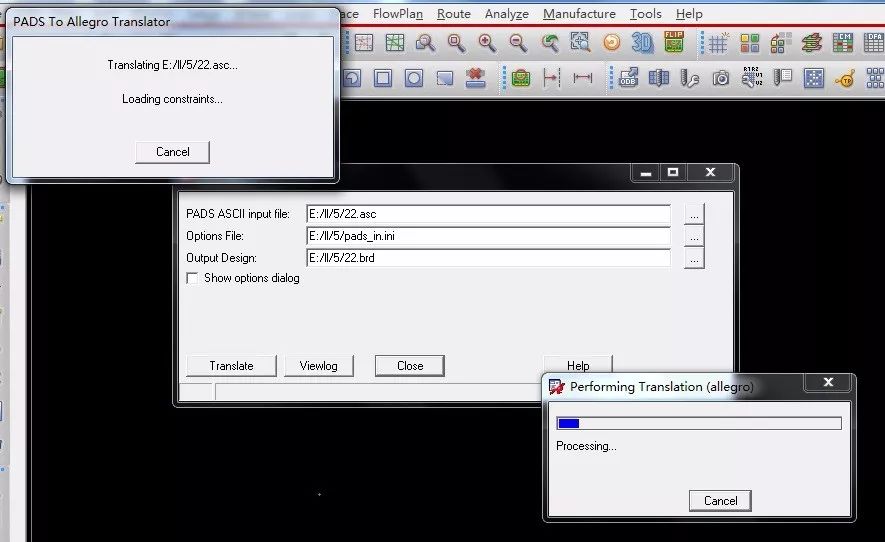

3.把ASCII文件(*.asc)导入到ALLEGRO,ALLEGRO 用的是V16.6版本的,其他的版本没有试。

如下:

选择导入PADS格式的文件

导入和转换后输出文件路径选择,以及层的配置文件选择。

按转换会弹出这窗口出来,按“是”确认。

左上角会有一个窗口弹出来,等待让它转换完成。

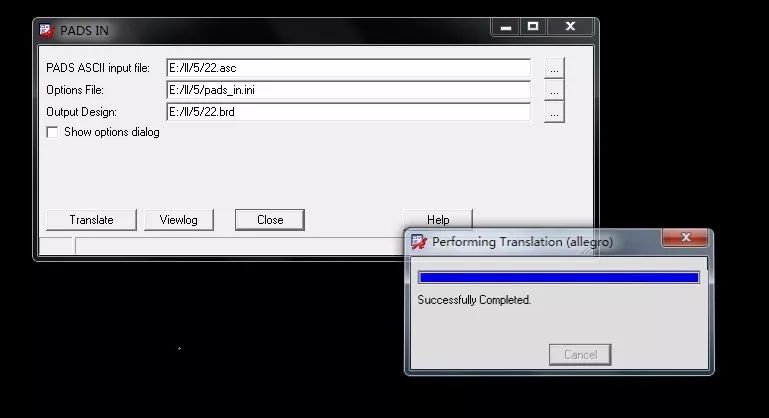

转换完成并成功

4.用Allegro打开刚才转换成功并保存的文件

丝印框和阻焊层都有。

5.Allegro 到处PCB封装方法:执行菜单命令:File => Export => Librarys

6.不足:转换的层配置文件,层配置好后仍然有一些封装焊盘的阻焊层和钢网层没有出来。需要手工进行完善。

7.ini层配置文件说明:

allegro自带的原始文件类容如下:

[Options]

CreateSolderLayers=0

SolderOversize=0

[Line Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Copper Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Text Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Decal Map]

0=PACKAGE GEOMETRY|SILKSCREEN_TOP

1=PACKAGE GEOMETRY|SILKSCREEN_TOP

2=UNUSED|-

3=UNUSED|-

4=UNUSED|-

5=UNUSED|-

6=UNUSED|-

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Pad Map]

0=ETCH|internal_pad_def

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

[Via Map]

0=VIA CLASS|internal_pad_def

1=VIA CLASS|TOP

2=VIA CLASS|INTERNAL1

3=VIA CLASS|INTERNAL2

4=VIA CLASS|INTERNAL3

5=VIA CLASS|INTERNAL4

6=VIA CLASS|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=UNUSED|-

22=UNUSED|-

23=UNUSED|-

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=UNUSED|-

29=UNUSED|-

30=UNUSED|-

我自己更改后的层配置文件类容如下:

[Options]

CreateSolderLayers=0.0254这里我改了发现也没变化

SolderOversize=0.0254这里我改了发现也没变化

[Line Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Copper Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Text Map]

0=BOARD GEOMETRY|ALL

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Decal Map]

0=PACKAGE GEOMETRY|SILKSCREEN_TOP

1=PACKAGE GEOMETRY|SILKSCREEN_TOP

2=UNUSED|-

3=UNUSED|-

4=UNUSED|-

5=UNUSED|-

6=UNUSED|-

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=PACKAGE GEOMETRY|SILKSCREEN_TOP

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=PACKAGE GEOMETRY|SILKSCREEN_BOTTOM

30=UNUSED|-

[Pad Map]

0=ETCH|internal_pad_def

1=ETCH|TOP

2=ETCH|INTERNAL1

3=ETCH|INTERNAL2

4=ETCH|INTERNAL3

5=ETCH|INTERNAL4

6=ETCH|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=UNUSED|-

30=UNUSED|-

[Via Map]

0=VIA CLASS|internal_pad_def

1=VIA CLASS|TOP

2=VIA CLASS|INTERNAL1

3=VIA CLASS|INTERNAL2

4=VIA CLASS|INTERNAL3

5=VIA CLASS|INTERNAL4

6=VIA CLASS|BOTTOM

7=UNUSED|-

8=UNUSED|-

9=UNUSED|-

10=UNUSED|-

11=UNUSED|-

12=UNUSED|-

13=UNUSED|-

14=UNUSED|-

15=UNUSED|-

16=UNUSED|-

17=UNUSED|-

18=UNUSED|-

19=UNUSED|-

20=UNUSED|-

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

22=PACKAGE GEOMETRY|PASTEMASK_BOTTOM

23=PACKAGE GEOMETRY|PASTEMASK_TOP

24=UNUSED|-

25=UNUSED|-

26=UNUSED|-

27=UNUSED|-

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

29=UNUSED|-

30=UNUSED|-

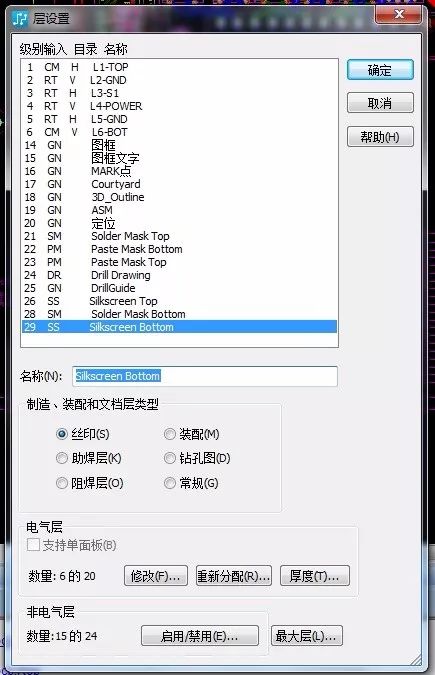

配置层的关系从哪里看出来的呢?从PADSLayout 里面的层定义可以看出来,执行如下的菜单命令:设置=》层定义,然后会弹出如下的窗口:

然后从这个层定义去看丝印或者阻焊是属于哪一层的,比如:

Silkscreen Top是第26层;Silkscreen Bottom是在第29层,Solder Mask Top是在第21层,Solder Mask Bottom 是在第28层,然后在相应的对象类型里面给他指定对应关系。

比如在Pad 焊盘这中类型[Pad Map]里面加上Solder Mask Top,和 Solder MaskBottom这个两层的对应关系,因为焊盘这种类型原则上是没有Silkscreen Top和Silkscreen Bottom的,所以焊盘里面可以不用加丝印的层对应关系。然后分别在21和28改为如下的对应关系。

21=PACKAGE GEOMETRY|SOLDERMASK_TOP

28=PACKAGE GEOMETRY|SOLDERMASK_BOTTOM

-

pcb

+关注

关注

4329文章

23192浏览量

400691 -

AD

+关注

关注

27文章

870浏览量

150647 -

Cadence

+关注

关注

65文章

932浏览量

142580 -

PCB设计

+关注

关注

394文章

4703浏览量

86597 -

可制造性设计

+关注

关注

10文章

2065浏览量

15743 -

华秋DFM

+关注

关注

20文章

3495浏览量

4806

原文标题:AD转cadence详细方法说明【包括原理图,原理图库,PCB封装库,PCB设计文件】

文章出处:【微信号:pcbgood,微信公众号:奈因PCB电路板设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AD PCB封装转Allegro封装或者AD PCB转Allegro PCB

AD PCB封装转Allegro封装或者AD PCB转Allegro PCB

评论