在快节奏的现代社会,时间变得越来越宝贵。对于时钟的电子设计,高精度且低功耗逐渐成为主流。笔者就有一个汽车显示屏的时钟显示项目,要求时钟一天的误差控制在1s以内。要想达到此要求,则必须满足晶振的频率偏差PPM《1/60/60/24*1000*1000=11.574ppm。世强团队明确了如此的高要求后,推荐我们采用EPSON的车载实时时钟RA8900CE,并全程为提供技术支持服务,给我们的研发缩减了不少时间。

RA8900CE符合AEC-Q200认证标准,是一颗集成32.768KHz晶体单元的高精度DTCXO,全温度范围频率偏差为5ppm,工作电流十分低,仅为0.7uA/3V(Typ.)。而且,RA8900CE支持高达400KHz的IIC通信,接口电压支持2.5V~5.5V。最主要RA8900CE的封装仅为2.5mm*3.2mm,小封装有利于PCB走线,方便我们把RA8900CE放置在MCU附近,大大降低了PCB布线难度。因此,其既满足晶振要求又降低了PCB布线难度,可谓是一举两得。下面我围绕项目研发设计过程中的关于RA8900CE使用情况及问题解决做了详细介绍。

问题总揽

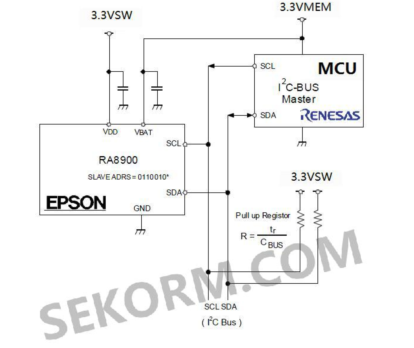

增加RA8900CE芯片后,我们发现样品初次上电后,DAB芯片无法和MCU正常通信。样品的电路框图如下图所示:

图1:汽车显示屏的时钟显示电路框图

问题分析及解决

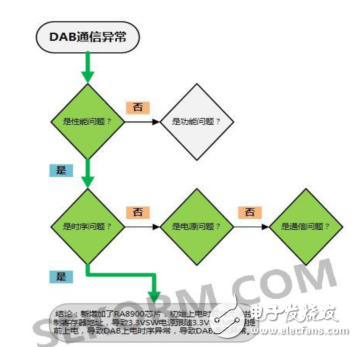

样品初次上电,DAB芯片无法和MCU正常通信。这是个富有挑战的问题,为了探究原因,我们采用排除法的思考方式,分析如下:

图2:问题分析

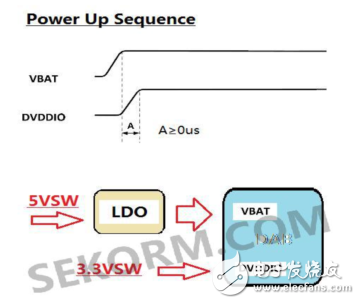

首先,要锁定导致问题的模块。我们先确认DAB上电时序,如图3所示,DAB芯片对上电时序有要求,即接口电源DVDDIO一定要在主电源VBAT之后上电。可是,我们测试后发现DVDDIO提前于VBAT上电,进而导致DAB通信异常。导致DAB通信异常的原因找到了,但是,究竟为何上电时序会不满足?

我们设计的DAB电源如图3所示,通过MCU控制5VSW和3.3VSW,保证5VSW提前与3.3VSW上电,理论设计完全满足DAB上电时序要求。但是,为何实际情况和理论设计的情况相差甚远?

图3:DAB上电时序

通过测量电源时序,最终我们发现是由于追加的RA8900CE芯片,在初始上电阶段导致电源串电,3.3VSW电源跟随3.3VMEM提前上电,导致不符合DAB上电时序要求。RA8900CE的内部电路如图4所示,为了防止3.3VSW没电时,发生串电现象,我们设置RA8900的寄存器地址为:VDETOFF,SWOFF=(1.1),这样设置是保证RA8900CE内部VDD和VBAT之间的开关永远保持关断状态。但是机器第一次上电的时候,RA8900CE的寄存器为默认值,而我们的软件只有在MCU起来后才可以设置RA8900CE的寄存器地址为:VDETOFF,SWOFF=(1.1)。这样,就会导致有一段时间VBAT和VDD直连,导致3.3VSW电源跟随3.3VMEM提前上电,进而导致DAB和MCU通信异常。

图4:RA8900CE的内部电路

知道了问题的根本原因,找到解决方案就变得很容易。由于RA8900CE工作时VDD电源消耗的最大电流是1.45uA,电流消耗非常小,因此我们决定采用VDD和VBAT共用一个电源的方案,即都使用3.3VMEM电源。如此一来就根本的解决了串电问题,进而保证了DAB的上电时序,解决了DAB和MCU无法通信的问题。

问题总结

简而言之,忽略了RA8900CE的寄存器设置条件,导致初始上电时DAB上电时序异常,最终导致DAB无法通信。虽然我们解决了此问题,但是如果从设计源头开始就注意RA8900CE寄存器的设置条件,则会从根本上杜绝此类问题的发生。电子设计容不得一点马虎,常常差之毫厘谬以千里,希望我的经历能给使用RA8900CE芯片的小伙伴们提供帮助,防微杜渐,不要让类似的问题再次发生。

世强作为全球最大的晶体时钟产品提供商EPSON官方指定代理商,全线代理EPSON旗下的晶体、晶振、实时时钟等芯片,在汽车车身、底盘、动力系统、车载、ADAS、安全系统,以及新能源汽车上都能提供成熟的解决方案、Demo支持和技术服务等。

作者:Ivan wu

-

显示屏

+关注

关注

28文章

4478浏览量

74229 -

时钟芯片

+关注

关注

2文章

249浏览量

39876 -

世强

+关注

关注

3文章

211浏览量

32553

发布评论请先 登录

相关推荐

LED显示屏驱动芯片应用及发展

基于车载时钟芯片的显示屏1s以内时钟误差实现

单片机时钟芯片DS12887的应用

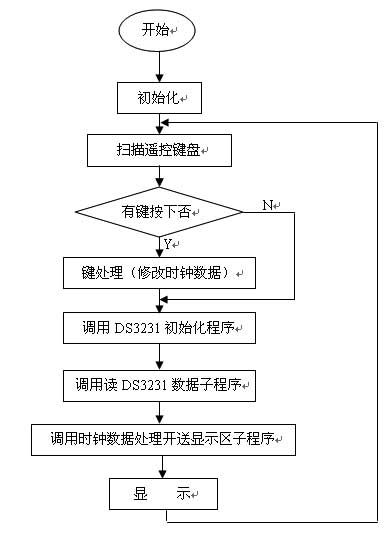

无线遥控LED时钟显示屏的设计与实现

实现LCD显示RTC实时时钟

使用ESP8266模块和12864显示屏实现网络时钟的资料合集

实例分析基于车载时钟芯片如何实现显示屏1s以内时钟误差

实例分析基于车载时钟芯片如何实现显示屏1s以内时钟误差

评论