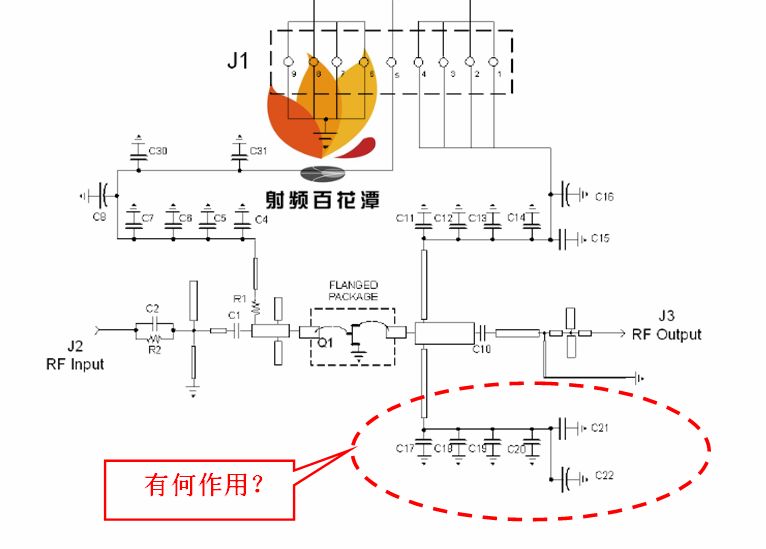

CGH40045F-TB漏级偏置电路采用对称设计,主要分析原因在于降低偏置网络阻抗,提高视频带宽VBW,从而减小功放管的电记忆效应。

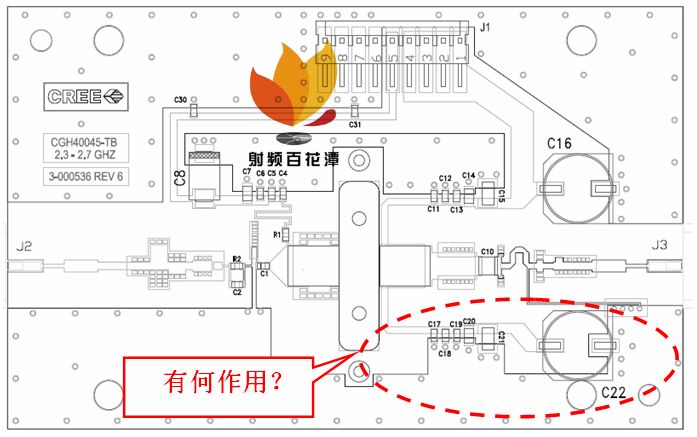

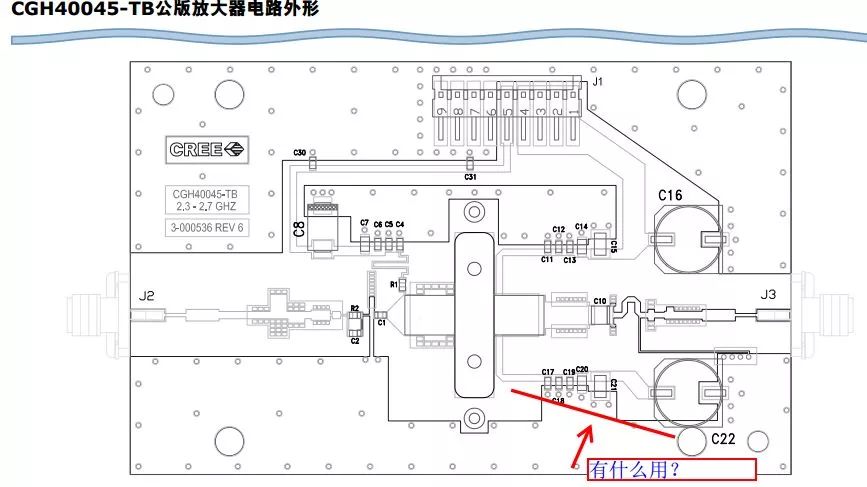

图1 CGH40045-TB PCB图

以下简单介绍下VBW与电记忆效应:

低阻抗通路的带宽被称为视频带宽(VBW),范围为100KHz~200MHz,个人理解为调制信号的带宽,即信道带宽,跟输入的调制信号有关。

功率管的记忆效应分为热记忆效应和电记忆效应,热记忆效应主要跟晶体管沟道温度周期有关,电记忆效应主要来源于功率放大电路的直流偏置。记忆效应的本质在于当前的时刻不仅跟输入信号有关,还跟过去的某一时刻有关,体现在增益和相位上。

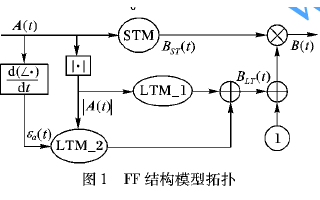

当功放管在数字预失真方案中,减小记忆效应对功放的影响显的尤为重要,偏置电路是记忆效应的一个重要来源,现实中,功率管的漏极到电源之间的电路阻抗(video impedance)在低频(VBW 10MHz)时并非为0,该阻抗的存在使得加载到功率管漏极的电压并非是个恒定值,而是随着功放输入信号变化。如果是纯阻性的,仅仅引起增益压缩,如果存在电抗部分,则引起记忆效应,因此在设计时,需要该阻抗越小越好。同时工程实验证明在同样的输入信号,同样的DPD系统中,较大的视频带宽(VBW)的ACPR要比较小的视频带宽(VBW)的ACPR要好。

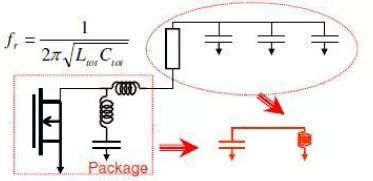

图2 晶体管VBW计算公式

图2所示,fr表征的是晶体管输出段低频谐振频率,频率越高,VBW越宽,Ltot指得是供电线跟旁路电容组成的等效电感,Ctot指的是晶体管漏级之间的电容,因此在可操作性上提高VBW的措施是降低Ltot。

具体措施如下:

1.如图1所示,漏级双供电方式,并联降低阻抗,减小低频信号的影响。

2.将uF级的电容靠近漏级放置,电容的工作频率实际大于其SFR,这样电容呈感性,从而减小Ltot,提高VBW。

3.缩短漏级供电线长度,小于1/4波长,但是这样会牺牲一部分功率。

-

电路

+关注

关注

172文章

5933浏览量

172459 -

射频

+关注

关注

104文章

5594浏览量

167911 -

Cree

+关注

关注

3文章

91浏览量

34605

原文标题:CREE射频功放提高视频带宽降低记忆效应设计分析

文章出处:【微信号:gh_f97d2589983b,微信公众号:高速射频百花潭】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

CREE射频功放提高视频带宽降低记忆效应设计分析

CREE射频功放提高视频带宽降低记忆效应设计分析

评论