DesignCon会议自举办以来一直都为我们带来业内最新的PCB layout和仿真软件工具。在DesignCon 2018期间,我有幸采访了Cadence的产品工程师Sam Chitwood先生。 Chitwood先生向我们解释了Cadence® Sigrity™的仿真软件如何允许用户在设计的早期阶段就作出决定,以及这样做如何有助于优化电源分配网络的设计并确保复杂PCB中的信号完整性。

Kelly Dack

现在我和Sam Chitwood都在DesignCon会议上。我了解到现在Sigrity工具可以解决电源完整性方面的一些问题。我们先来聊一聊设计师和工程师在电源完整性方面遇到了哪些问题好吗?

Sam Chitwood

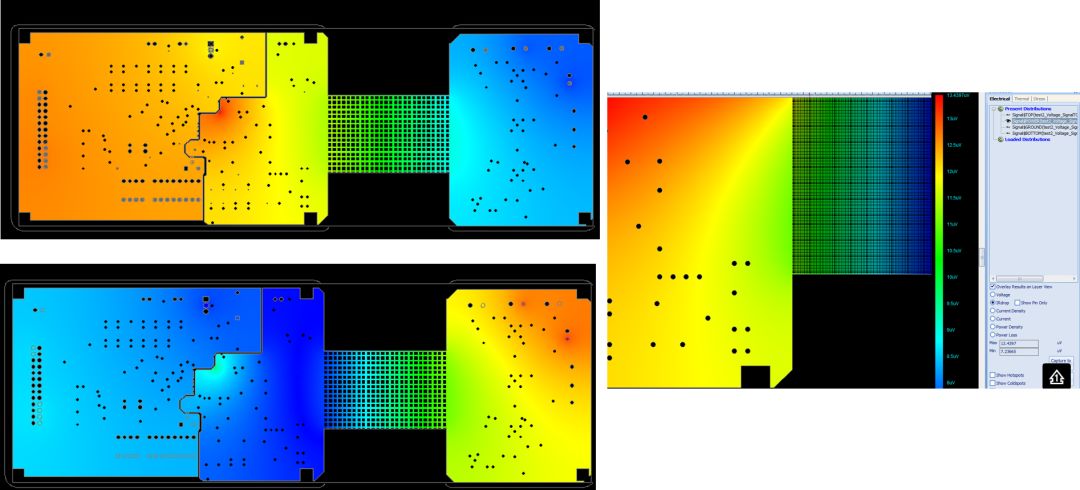

电源完整性问题有两个不同的方面:直流和交流。前者要求从根本上为器件提供充足的直流电源。就像你过去使用的移动电子设备一样,必须要有电池——一个直流电源。直流问题的起因在于大电流和布线金属不足的共同作用。

交流电源的完整性可以从频域和时域两方面考虑。在频域中,我们力求在相关带宽上获得平坦的阻抗分布。在时域中,以许多正在切换的I/O为例:如果它们的电源由于噪声较大而不稳定,那么噪声将在这些输出上表现为信号衰减。这种现象称为同步开关噪声(简称SSN),由此说明了电源完整性问题是如何影响信号完整性问题的。 Sigrity工具的特殊之处就在于它们可以在时域和频域两个方面同时进行信号、电源和地仿真。

Kelly Dack

仿真发生在前端、后端、还是两者均可呢?请告诉我们它最适用的地方。

Sam Chitwood

以往,大多数电源完整性仿真都是在布局后,接近设计周期的末期进行的。但是显然这种做法并不理想。设计末期的每个人都很繁忙,几乎没有人有足够的时间去执行优化设计或降低成本。PI工程师更是几乎没有时间去执行验收分析以判断设计的好坏。

实际上,过去两年我们一直在做的就是实现设计上的“左移/前移”(我的同事Brad Griffin喜欢使用这个形象的称呼)。意即:如何将所有类型的仿真分析移到设计周期的早期?以下是从原理图角度的一个示例:电源网络是否有足够的去耦电容?是否有正确的去耦电容?这些问题恐怕大多数原理图设计工程师都无法回答。我们的目的就是把以往仅在设计周期即将结束时才做的工作、那些PI专家几乎没有充足时间去进行检查的工作,提前到设计周期早期来做,并开放给设计工程师和layout工程师来协助完成。那么问题来了,你认为提前到设计周期早期协助完成电源完整性工作意味着什么?

Kelly Dack

“提前”对我来说,大概意味着从电路原理图阶段入手。

Sam Chitwood

没错,我们的目标是从一开始就让原理图设计人员参与进来。他们需要一种简便、快捷的自动化方式来提供有用的可操作的信息。例如,是否选择了正确的去耦电容?原理图设计人员一开始就需要这些信息,而不是让PI专家在最后紧要关头说“你选择的去耦电容一直都是错的”。这样的话,设计人员就必须进行返工。而从电源分配布线的角度来看,这相当于要全部重做了。显然,代价是非常昂贵的。

Kelly Dack

对于那些可能没有接受过仿真培训的新手而言,请解释一些仿真的要素,比如元件、数据表以及我们要寻求什么结果。

Sam Chitwood

对于一个可能是仿真新手的layout工程师来说,我们用一个很好的例子来解释他都能够做些什么。在我们的软件里,PDN电感检查是非常容易获取的,绝对不需要电气模型。Layout工程师需要的仅仅是包含正确层叠和指定电源网络名称的layout数据库。通过这些信息,我们的软件可以自动识别元件名称以及它们的位置。至于 IC器件,我们解决了IC与其每个去耦电容之间的环路电感。这么做的目的很简单,结果也很直观:识别所有异常的去耦电容。在确定具体问题之后,layout设计人员可以检查是否有不正确的布线或者是否有去耦电容被放置得太远。这些去耦电容是否需要被移动或从顶层换到底层等等。这些问题都可以很快被发现并提前进行纠正。

Kelly Dack

你这里说的“提前“就不是指原理图设计阶段了吧?

Sam Chitwood

是的,我刚刚说的例子适用于layout设计人员。现在,让我们“前移/左移”到原理图设计人员。正如我之前提到的,原理图设计人员需要在一开始没有可用layout的情况下就知道应该选择哪些去耦电容。而这一关键在于PDN的目标阻抗。我们倡议为系统客户提供芯片的IC供应商提供目标阻抗数据,以便原理图设计人员据此设计出恰好合格的性能方案。由于没有目标阻抗数据参考,原理图设计人员从根本上受困于“过犹不及“的两难境地。正如有些设计师所说的:“我可以继续添加去耦电容,并且可以继续提高性能,但是该提高到什么程度呢?”没有目标阻抗,就没有办法真正知道设计是否达成,更没有办法判定设计的好坏。这种情况通常会导致过度设计去耦电容和不必要的BOM成本。

Kelly Dack

那好,我们获得了一个目标阻抗,并且我们早在原理图阶段就使用了仿真分析工具。那么我们何时可以确定添加额外的板层会提高电源完整性呢?请告诉我们,如何运用Sigrity工具来确定层叠和板层。

Sam Chitwood

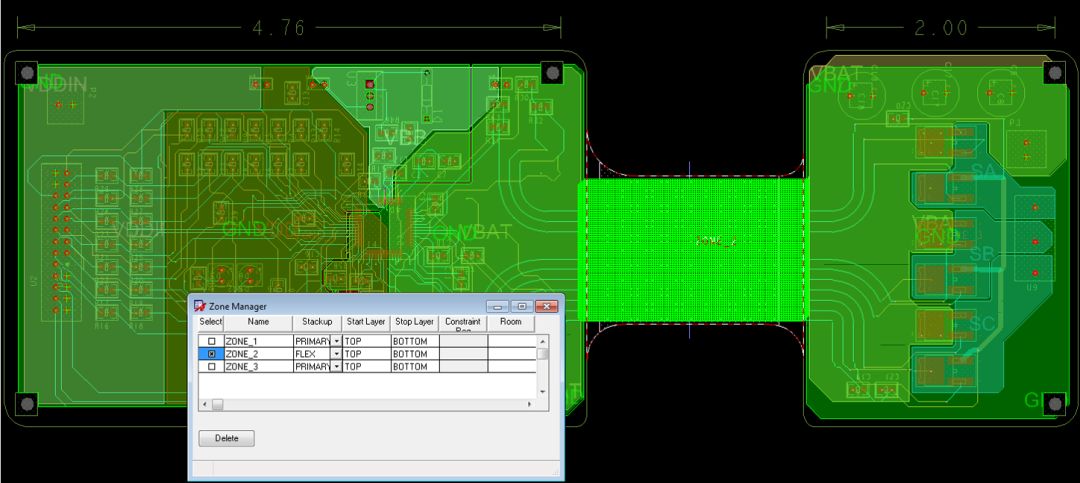

PDN层叠设计是一个很好的介于原理图和layout两者之间的设计区域。我们将此称为PDN的预布局。

Kelly Dack

因为我们轻易就可以在设计中添加一层。但是我们如何知道这会在多大程度上帮助我们实现成本合理化呢?

Sam Chitwood

PDN预布局是我们创建的工作流程之一,可以帮助指导用户选择层叠和PDN层分配。用户选择将电源层放置在层叠的顶部或是底部、以及选择在顶部或底部表面放置去耦电容,都会对性能造成差异极大的影响。这些关键决策都是我们的工具可以自动化仿真分析,并且生成去耦电容配置准则。在这里,不要将这些去耦电容准则视为强制规定,而应将其视为基于分析基础的建议。我们提供了三种去耦电容推荐列表:顶层、底层以及电路板背面元器件下方的去耦电容。基于这三种预布局去耦电容的配置列表,layout工程师便清楚知道要做什么了。该方法比传统的“尽可能靠近元器件放置去耦电容”的经验法则要优越很多。

Kelly Dack

这可以让layout设计人员根据设计中的其它目标参数来进行布局设计。例如,很多设计都是力求单面组装,因此设计人员知道成本是多少、知道将元件和电容作为单独的部件添加到电路板背面的成本。但他是否也知道这提升了多少性能,能否做个成本分析?

Sam Chitwood

当然可以。我们工具独一无二的特点之一就是能够将成本信息纳入去耦电容优化分析。在同类型的工程工具中,允许用户在电气性能与BOM成本之间进行权衡决策的产品并不常见。而我们的产品可以让用户知道每个元件成本、装配成本以及BOM库存成本(或是在装配期间存储该元件的成本),从而进行成本分析。

Kelly Dack

本次展会上很多与会者都十分关心高速信号和信号完整性问题,但也有设计工程师在应对、处理所有的“设计制约因素”。我们现在有“控制成本设计”参数,有“可制造/生产性设计”约束。我们谈到了诸如把元器件放在电路板的这一边或另一边之类的问题;DFX,或叫“卓越设计”。你们的工具则可以直接解决成本问题。

Sam Chitwood

是的,直接从去耦电容BOM的角度来看,或者间接从层叠和DC直流电源的角度来看都可以解决成本问题。

Kelly Dack

那么作为结束话题,我们不妨来讨论下关于DC直流电源。DC直流电源是个很大的话题。

Sam Chitwood

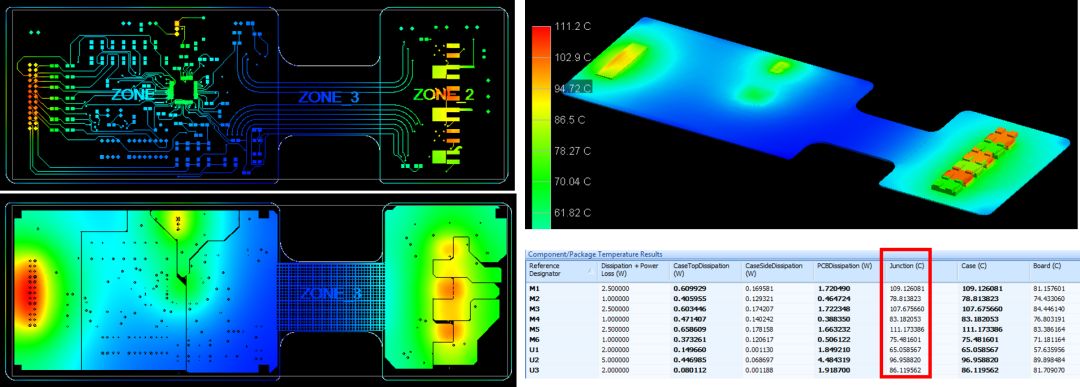

据我所知,Cadence Sigrity PowerDC™ 是第一个将电和热组合到一个协同仿真环境中的技术工具,仅仅只需一个按钮,用户就可以在同一个GUI界面内获得电结果和热结果。可以想象,这项技术会有多么炙手可热。例如,一个特定的过孔可以允许通过多大电流?将10安培从一层移动到另一层需要多少个过孔? Sigrity技术是该领域应用的先驱。

Kelly Dack

因为是电源相关,因此也是热相关的?

Sam Chitwood

是的,电和热是紧密相关的。开玩笑地说,你永远不想看到一封提到“火”的电子邮件。我看到过客户们用其他一些创造性的方式向管理层描述他们所遇到这个情况。例如,对于一个器件,他们可能会说发生了“放热事件”。另一个很好的例子是PCB的“光炭化”,但我个人最喜欢的是“过孔炸弹”。

Kelly Dack

我从未听说过这些。不过我们常说:“如果它变暖,没关系;如果它变热,也没关系;但当它冒烟时,就意味着失败了。”

Sam Chitwood

同意!我们有一位客户来找我们就是为了热问题:他们发生了级联故障,导致电路板上的过孔熔化。他们认为他们有足够数量的过孔,但分析显示这些过孔并未正确放置。

Kelly Dack

电路板材料通常不被制造或设计成拥有处理热问题的能力。热是电路板的大敌。无论是否“爆炸”,Z轴热膨胀对于过孔来说都十分糟糕。

Sam Chitwood

我们要记住FR-4中的“FR”代表阻燃,并不防火!

Kelly Dack

您还有什么要告诉大家的吗?

Sam Chitwood

Cadence近期发布了新的电源完整性实用技术Allegro PowerTree™ 工具。该工具可在原理图设计人员、layout设计人员和PI专家之间共享PI分析的新的生态系统。我们希望真正实现PI方法的自动化,在该方法中,所有这三种用户都可以为PDN分析做出贡献,最终在预算和截至日期内实现设计优化。

Kelly Dack

请向我们介绍下PowerTree™工具以及它是如何处理PI问题的。

Sam Chitwood

我们的目标是实现直流和交流仿真的自动设置,让过去非常复杂的问题变得非常简单。例如,大型服务器主板上的电源部分可能非常复杂,有数十个与之关联的网络名称。这些网络名称并不易读,因为它们是自动生成的、随机的文本字符串。显然,任何人都不愿意跟踪这些名字。PowerTree™工具能够自动识别从源到全部负载的所有电源网络,实现元件,例如滤波电感、电阻、电容的自动识别与分配型号;还可实现自动应用检测约束,例如每个引脚的压降和目标阻抗。而仿真过程实际上也仅仅只需几个按钮就可以自动完成。

Kelly Dack

哇,听起来很简单。

Sam Chitwood

是的,无论从DC直流还是AC交流的角度来看都是这样的。我相信你知道Cadence是以基于信号完整性规则约束下的布线而闻名的。我们希望在电源完整性方面做出同样的成就。我们有许多类型的DC约束和AC目标阻抗约束。只要提供了这些限制条件,那么从原理图阶段到整个设计周期直至电路板验收的各个环节,PCB设计人员都可以保证得到正确的电源分配。

最后,我们在DesignCon有一家IC供应商介绍了他们如何为PCB客户提供目标阻抗的流程。我们希望能广泛传播这种方法,以便整个行业都可以从中受益。

-

电源

+关注

关注

184文章

17693浏览量

249909 -

pcb

+关注

关注

4318文章

23070浏览量

397231 -

信号完整性

+关注

关注

68文章

1403浏览量

95454

原文标题:DesignCon2018专题采访:如何在设计周期早期自动实现电源完整性仿真

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

设计师和工程师在电源完整性方面遇到了哪些问题好吗?

设计师和工程师在电源完整性方面遇到了哪些问题好吗?

评论