做芯片设计的同学应该或多或少的听到过“异步电路”(Asynchronous Circuit)。和我们实践中使用的同步电路相比,异步电路好像一直是一个传说中的存在。虽然甚至有过完全基于异步电路的处理器,但它始终没有进入过主流的数字芯片领域。不过,伴随AI芯片的热潮,异步电路越来越多的出现在我们视野当中,甚至成了一些芯片的卖点。本文和大家一起探讨一下异步电路原理及其优势和劣势,并通过Intel的Loihi芯片看看它的实现,希望能够给大家一个更清晰的认识。

如果要了解异步电路,[1]是一个比较好的参考。首先我们可以从下面4个图简单回顾一下异步电路的概念。

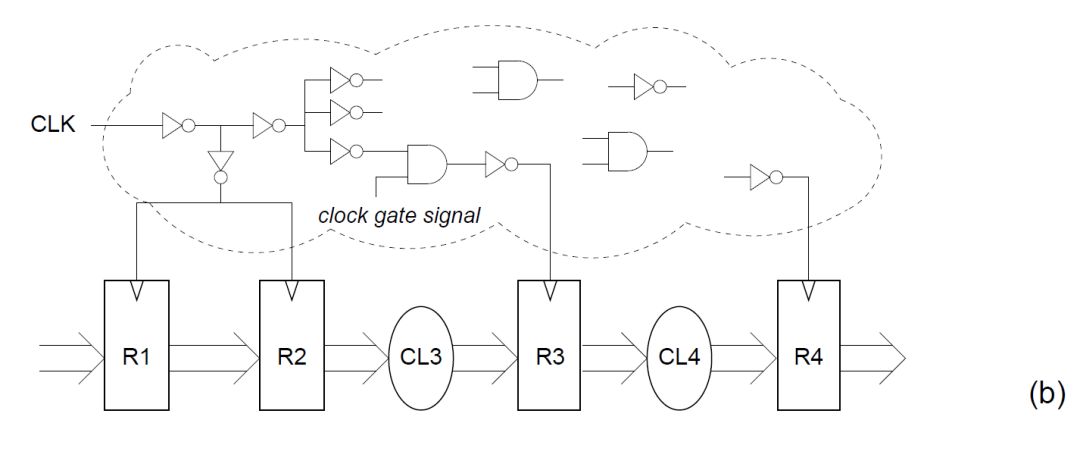

目前数字芯片的主流设计都是同步电路(Synchronous),它的基本结构如上图所示。数据的流动靠一个全局时钟信号(Clock)来同步。所有的时序器件(图中的Rn)都是在时钟边沿采样数据并向后传输。数据被处理(比如逻辑和算数操作)后到达下一级。相当于大家都只在约定好的时间点才观察输入数据线上的数据,只要保证数据在这个时间点是稳定正确的,数据就可以正确的被传递和处理。可以说,这种以时钟信号驱动的流水线结构是现代数字电路的基础。随着设计和测试的复杂度的不断提高,加之低功耗设计(比如clock gating)的需求,在一个实际设计中,时钟信号会变得异常复杂,如下图所示。这也是困扰目前大规模芯片设计的主要问题之一。

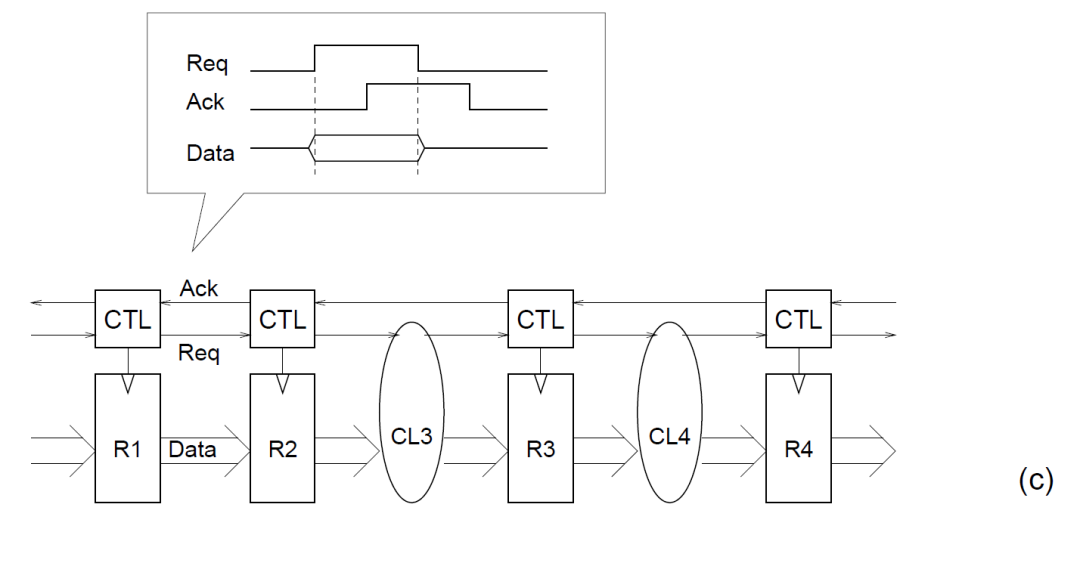

言归正传,我们还是重点看看异步电路。异步电路有时也称为无时钟(clockless)或者自定时(self-timed)电路,顾名思义,就是没有全局时钟的电路,如下图所示。在异步电路中,大家没有一个统一的时钟,前后级直接告知对方能否接收数据。具体来说,就是通过前后级直接发送握手信号(Request和Acknowledge)来保证数据传输的正确性。Bundled-data是这种机制的一个标准术语,其含义是数据和控制信号捆绑在一起,而其中控制信号则起到了在同步电路中时钟信号所起的作用。

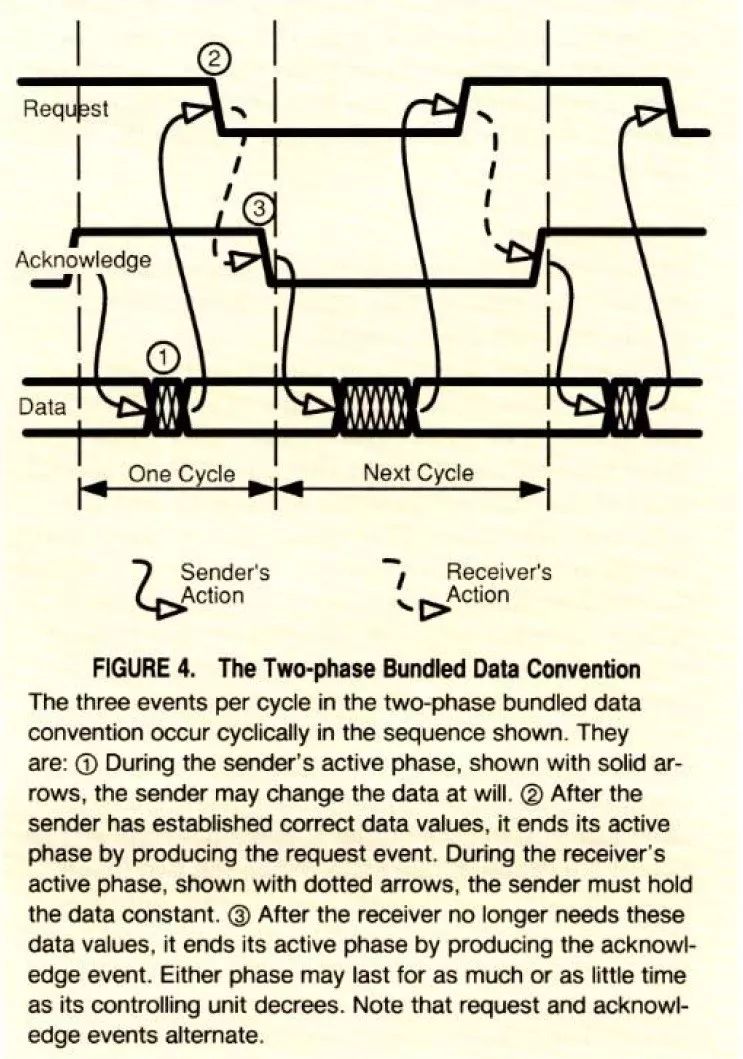

Bundled-data使用的控制协议包括几种,比如数据传输要进行4次握手的4-phase bundled-data protocol,和只要两次握手的2-phase bundled-data protocol。下图来自[2],图灵奖得主Ivan Edward Sutherland的一篇论文。正是这篇论文提出了2-phase bundled-data protocol(论文还包括了其它非常丰富的内容和思考,非常值得一看)。这张图非常清楚的描述了用两次握手来实现数据传输的方法,我就不多解释了。这里要注意的是,控制信号Request和Acknowledge的上升沿和下降沿是完全等效的。

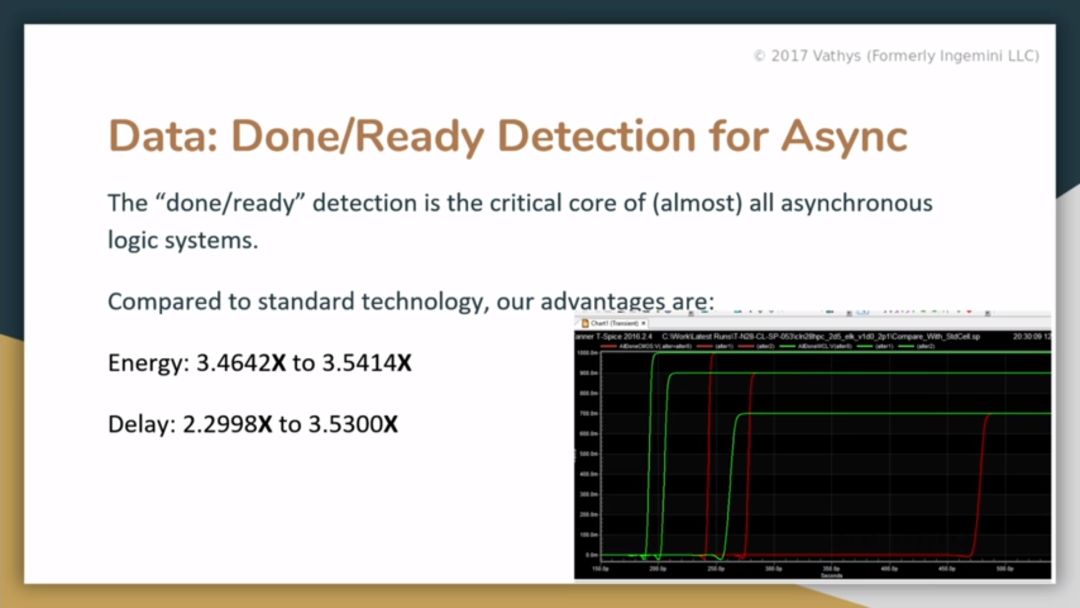

从这里不难看出在异步电路中控制信号是非常重要的。回想一下Petascale AI芯片Vathys:靠谱项目?清奇脑洞?还是放卫星?,印度小哥给的一页PPT就是在说他们的异步电路设计的控制信号性能多好。不管是不是忽悠,关键点还是抓住了。

•••

下面我们来讨论一下异步电路和同步电路相比的优势和劣势,以及它在AI芯片里的应用。在Wikipedia的“Asynchronous circuit”词条里,对两者进行了比较完整的对比。(可能因为主题词是异步电路,对优势讲的比较多)

优势:

Robust handling ofmetastabilityofarbiters.

对做数字芯片的同学来说,亚稳态(metastability)一直是个头疼的问题。它主要是指数字信号在翻转(比如从低电平‘0’变为高电平‘1’)的过程中会有一段时间(transition time)信号不稳定,如果我们正好在这个过程中对信号进行采样,则结果是不确定的,可能是‘0’也可能是‘1’。因此在同步电路中,必须保证在采样的时刻(时钟边沿)信号必须是稳定状态。这在时钟频率很高,和跨时钟域数据传输时是很有挑战的。而在异步设计中,由于控制信号本身就和数据信号的状态相关,可以比较容易的解决这个问题。

Higher performance function units, which provide average-case (i.e. data-dependent) completion rather than worst-case completion.

使用异步设计,有可能实现更高性能的功能单元。这是因为在同步设计中,由于大家都在相同时钟下工作,最小的时钟周期必须保证电路在信号传输的最差情况(worst-case)下仍然能正确工作,所以整体性能被最差的点限制。而异步设计中,每一级完成操作的时间只和本级相关,整体性能是平均的结果,因此可能在整体上超过同步电路。可以说异步设计如果发挥“出色”,在性能上是可以超过同步设计的,当然这对技术能力是个巨大的挑战。

Early completionof a circuit when it is known that the inputs which have not yet arrived are irrelevant.

当知道尚未到达的输入数据与功能不相关时,可以提前早完成这一级电路的操作。

Lower power consumption because no transistor ever transitions unless it is performing useful computation...Also, clock drivers can be removed which can significantly reduce power consumption. However, when using certain encodings, asynchronous circuits may require more area, which can result in increased power consumption if the underlying process has poor leakage properties (for example, deep submicrometer processes used prior to the introduction ofHigh-k dielectrics).

低功耗是可能异步电路在宣传中最多的提法。原因也很简单,在没有数据发生变化的时候,异步电路是不工作的。此外,在同步电路中我们需要很多的时钟驱动电路来保证全局时钟信号的质量,这也非常耗电。异步电路当然没有这个问题。

但是,在说异步电路的功耗低的时候,我们必须相当谨慎。首先,异步电路需要额外的控制信号,当使用某些编码时,异步电路可能需要更多面积,而更多的面积意味着更大的静态功耗。我们知道,CMOS工艺尺寸越小,静态功耗在整体功耗里所占比例越大。因此,异步电路虽然只在必要时工作,但整体在能耗上的表现还是需要认真分析才能有准确结果。第二,目前同步设计也会采用各种低功耗设计手段,比如门控时钟技术等等,对比的时候应该考虑这个因素。

"Elastic" pipelines, which achieve high performance while gracefully handling variable input and output rates and mismatched pipeline stage delays.

异步电路可能实现“弹性”流水线,这个话题在[2]中有非常详细的说明,确实是“gracefully”。

Freedom from the ever-worsening difficulties of distributing a high-fan-out, timing-sensitive clock signal.

之前已经提到,目前的数学芯片设计中的复杂时钟信号已经是一个最有挑战性的问题。在一个芯片设计项目中,需要把大量的精力放在时钟树的设计和验证上。

Better modularity and composability.

更好的模块化和可组合性?这个可能还是强调异步电路的控制完全在本地进行,可以比较好的集成。

Far fewer assumptions about the manufacturing process are required (most assumptions are timing assumptions).

目前的芯片设计,必须对生产工艺做很多假设,特别是时序上的问题。而对异步电路来说,这个问题要简单一些。

Circuit speed adapts to changing temperature and voltage conditions rather than being locked at the speed mandated by worst-case assumptions.

相对而言,异步电路的速度可以比较好的适应变化的温度和电压条件,而不是必须考虑最坏情况。换句话说,如果温度,电压等条件发生变化,导致电路延时变大,异步电路本身就可以适应这种变化,“自动”降低速度,而不会发生功能的错误。

Immunity to transistor-to-transistor variability in the manufacturing process, which is one of the most serious problems facing the semiconductor industry as dies shrink.

对制造过程中的variation可以比较好的适应。而这个问题随着工艺尺寸的缩小,是半导体行业面临的最严重的问题之一。

Less severeelectromagnetic interference(EMI). Synchronous circuits create a great deal of EMI in the frequency band at (or very near) their clock frequency and its harmonics; asynchronous circuits generate EMI patterns which are much more evenly spread across the spectrum.

电磁干扰(EMI)问题相对要少。 同步电路的时钟信号,在其时钟频率及其谐波处(或非常接近)的频带内产生大量EMI; 异步电路会产生EMI,但其模式在整个频谱上是均匀分布的。

In asynchronous circuits, local signaling eliminates the need for global synchronizationwhich exploits some potential advantages in comparison with synchronous ones. They have shown potential specifications in low power consumption, design reuse, improved noise immunity and electromagnetic compatibility. Asynchronous circuits are more tolerant to process variations and external voltage fluctuations.

这个不解释了,基本是前面所说的优势的一个总结。不过还是强调一下,这些优势的原因是异步电路“local signaling”的本质特点。

Less stress on the power distribution network. Synchronous circuits tend to draw a large amount of current right at the clock edge and shortly thereafter. The number of nodes switching (and thence, amount of current drawn) drops off rapidly after the clock edge, reaching zero just before the next clock edge. In an asynchronous circuit, the switching times of the nodes are not correlated in this manner, so the current draw tends to be more uniform and less bursty.

还是由于不需要一个强有力的全局时钟,异步电路中对供电网络的压力也会减轻。

小结一下,异步电路还是有很多特点的,我们不能简单的说一句“异步电路可以降低功耗”就作为概括。它的很多优势都是源于“local signaling”的基本特点。抓住这一点,对于思考它在特定应用的作用非常重要。

劣势:

Area overhead may be up to double the number of circuit elements (transistors), due to addition of completion detection and design-for-test circuits.

由于增加了控制和用于DFT的电路,异步电路的面积开销可能高达同步设计的的两倍。

Fewer people are trained in this style compared to synchronous design.

与同步设计相比,了解这种风格的人要少很多。当然,这也是因为在实际设计中用的少的原因。

Synchronous designs are inherently easier to test and debug than asynchronous designs.However, this position is disputed by Fant, who claims that the apparent simplicity of synchronous logic is an artifact of the mathematical models used by the common design approaches.

与异步设计相比,同步设计更易于测试和调试。当然,这一观点也有争议。

Clock gatingin more conventional synchronous designs is an approximation of the asynchronous ideal, and in some cases, its simplicity may outweigh the advantages of a fully asynchronous design.

这一点之前已经提到了,同步设计中的时钟门控是异步设计的一种近似,并且在某些情况下,其简单性带来的好处要远比异步设计带来的好处多。

Performance (speed) of asynchronous circuits may be reduced in architectures that require input-completeness (more complex data path).

在需要输入完整性(更复杂的数据路径)的结构中,异步电路的性能(速度)可能会降低。这一点我也没想到很好的例子。

Lack of dedicated, asynchronous design-focused commercialEDAtools.

缺乏专用于异步设计的商用EDA工具。由于现在芯片设计的复杂度越来越高,EDA工具对芯片设计来说是不可替代的,因此这一点也是我们对异步电路的实用性诟病最多的地方。

异步电路曾一度在高性能处理器和低功耗设计领域占有重要地位的,但随着同步设计更快的发展,异步电路越来越边缘化;而用的人越少,这种倾向就更加严重。总的来说,异步电路目前还是“异类”,真正了解并且有经验的人非常少。没有EDA工具的支持下,做一个大型设计几乎是mission impossible。

•••

异步设计虽然比较冷门,但在AI芯片领域,还是看到一些有趣的尝试。特别是在类脑计算(Neuromorphic)芯片中,异步电路是一个比较普遍的选择。

如Intel的Loihi论文[3]所说:

“Biological neural networks are fundamentally asynchronous, as reflected by the absence of an explicit synchronization assumption in the continuous time SNN model given in the Spiking Neural Networks section. Accordingly, asynchronous design methods have long been seen as the appropriate tool for prototyping SNNs in silicon, and most published chips to date use this methodology.Loihi is no different, and, in fact, the asynchronous design methodology developed for Loihi is the most advanced of its kind. For rapid neuromorphic design prototyping, we extended and improved on an earlier asynchronous design methodology used to develop several generations of commercial Ethernet switches. In this methodology, designs are entered according to a top-down decomposition process usingthe CAST and CSP languages...

Given a hierarchical design decomposition written in CSP, a pipeline synthesis tool converts the CSP module descriptions to Verilog representations that are compatible with standard EDA tools.”

这段话里我们可以看到一些重要信息。1.生物神经网络从根本上说是异步的,因此类脑芯片使用异步电路也是很自然的选择;2. Loihi开发的异步设计方法是同类中最先进的。设计使用CAST和CSP语言,采用自顶向下的设计过程。3. 在使用了CSP描述之后,他们使用了一个“pipeline synthesis”工具把CSP描述翻译成Verilog,之后的流程就和目前标准的EDA工具流程兼容了。

其实,Loihi的设计方法可以给我们一些启示,因为这种设计方法尽可能的把传统EDA工具无法支持的部分限定到了最小的范围。这样,我们之前提到的目前EDA工具和异步设计无法兼容的问题就得到一定的缓解。当然,具体的设计和验证的细节我们还不得而知。

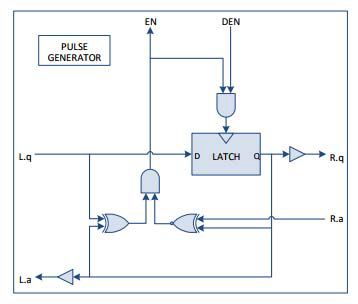

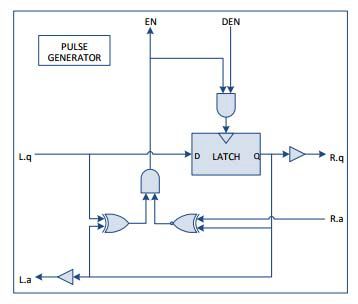

以下是Loihi中的Bundled data pipeline和Bundled data pulse generator电路,实现的就是前面介绍的2-phase bundled-data的机制。

•••

除了类脑计算外,目前的ML加速器和处理器很多也采用了数据流驱动的结构。因此,异步设计应该可能在其中发挥一定的作用。但由于ML加速芯片和类脑计算芯片在基本处理和数据传输的需求上有较大的差别,目前把异步电路用在其中的尝试还不是主流。虽然我们也看到一些宣传中提到异步设计的说法,但还不知道实现细节和设计的方法。在这种情况下,还很难断言异步设计能在ML芯片中发挥多大作用。

本文主要希望使读者对异步电路有一个比较全面和公平的认识。正如我多次说过的,脱离应用环境,很难评价一个架构的优劣。放在AI芯片的环境中,异步电路的一些特色确实可能发挥作用。大家可以把异步电路作为一种选择放进自己的工具箱,但也应该看到,它并非轻松就能驾驭的武器。

-

异步电路

+关注

关注

2文章

48浏览量

11184 -

AI芯片

+关注

关注

17文章

1925浏览量

35372

原文标题:“传说中”的异步电路是否能在AI芯片中异军突起?(纯干货!)

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

异步电路原理及其优势和劣势,并通过Intel的Loihi芯片看看它的实现

异步电路原理及其优势和劣势,并通过Intel的Loihi芯片看看它的实现

评论