PCI-X

PCI-X总线在PCI总线的基础上发展而来,其在软件和硬件层面上都是兼容PCI总线的,但是却显著的提高了总线的性能。也就是说PCI-X的设备可以直接插到PCI的插槽中去,PCI的设备也可以直接插到PCI-X的插槽中去。

从硬件层面上来说,PCI-X继承了PCI总线中的Reflected-Wave Signaling,但是在信号的输入端加入了输入寄存器以增强时序性能,提高了总线的时钟频率。在PCI-X2.0的Spec中还提出了DDR和QDR技术,进一步提高了PCI-X总线的带宽。

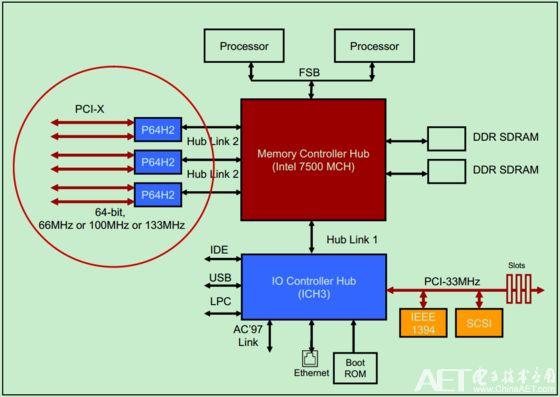

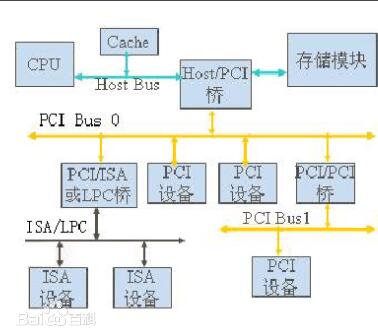

一个典型的PCI-X总线系统的例子如下图所示:

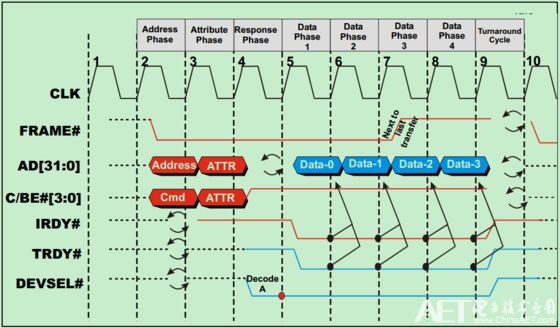

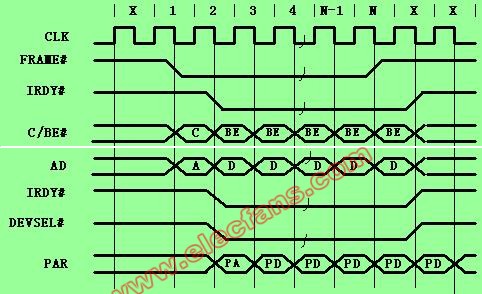

下面是一个PCI-X 突发读存储操作(Burst Memory Read Bus Cycle)的例子:

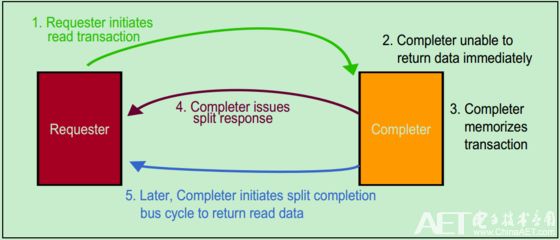

在PCI总线中,以总线主机从从机设备读操作为例,当从机设备尚未准备好结束这次操作(从机设备未就绪,且数据尚未发送完)时,可以通过锁存数据并插入等待周期,或者发起Retry操作。PCI-X总线采用了一种叫做Split Transaction的方式来处理这种情况,如下图所示。此时,发起读操作的总线主机被称为Requester,而接受并向总线上发送数据的从机设备被称为Completer。

注:PCIe Spec中继承了PCI-X的这种命名方式。

采用这种方式的PCI-X总线的总线传输利用率(效率)可以达到85%,而标准的PCI总线只有50%-60%。关于Split Transaction的详细内容,建议大家去参考PCI-X的Spec,这里不再详细地介绍。此外,PCI-X总线还配置地址寄存器(Configuration Address Register)中加入了NS(No Snoop)和RO(Relaxed Ordering)两位以提高总线传输效率。

前面的文章中介绍过,PCI总线的中断操作是通过一系列的边带信号(Sideband Signals)来完成的,在PCI-X Spce中引入了消息信号中断(MSI,Message Signaled Interrupts)的机制,以取代这些边带信号,进而精简系统设计。

注:关于MSI的详细内容,建议参考PCI-X Spec,此处不再详细介绍。

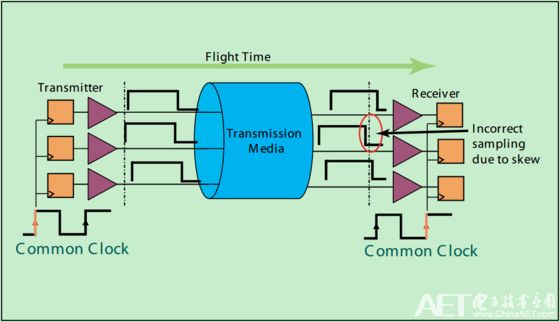

在介绍PCI-X2.0中提出的源同步模型之前,首先先来简单地聊一聊非源同步模型的内在问题。所谓非源同步,就是说,信号的发送端和接收端的时钟分别由一个或者两个时钟源驱动,发送端和接受端的时钟同频率,但是却很难保证其同相位(即存在时钟的相位偏差,skew)。

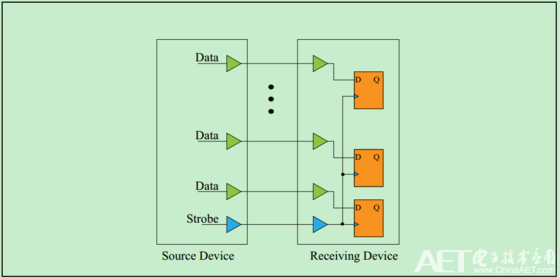

如上图所示,由于信号线众多,在PCB设计的时候,很难保证每一条信号线的长度都完全相同(更不要说还有过孔等因素)。因此,即使信号在发送时完全沿对沿的(实际上也是不可能的,对于PCI总线来说),也很难保证信号在同一时间到达接收端,此时的信号必然不再是沿对沿的了。如果不同信号线之间的传输延时差异较大,就很容易导致信号在接收端的采样错误,进而提高数据传输的误码率。

为了解决这些问题,在PCI-X2.0的Spec中提出了源同步模型(实际上,在目前高速的FPGA逻辑设计和数字ASIC设计中采用的基本上都是源同步的模型)。如下图所示,此时系统的时钟由发送端(即Source Device)直接提供,并和数据信号一同传输至接收端,这就很好地解决非源同步模型中的时钟相位差(Skew)的问题。此外,PCI-X2.0还在接收端输入寄存器的基础上支持了DDR输入,甚至是QDR输入,极大地提高了总线的带宽。64-bit的133MHz PCI-X2.0 QDR总线的带宽甚至达到了惊人的4262MB/s!基本上算是并行总线的巅峰了(DDR SDRAM不算是总线)。

然而,有意思的是,PCI-X2.0似乎生不逢时,虽然它显著地提高了PCI总线的带宽,但依旧无法掩盖并行总线在高速总线数据传输中劣势。PCI-X2.0总线虽然性能优异,但是却几乎很少得到应用,由于其高功耗高成本,且并行总线的引脚过多,需要极其复杂的PCB设计,导致PCI-X2.0只在极少数高端的市场中得到了应用(如服务器市场等)。导致PCI-X2.0未能达到大规模应用的另一个因素就是PCI Express(PCIe)总线时代的到来,其标志着高速串行总线取代传统的并行总线的时代的开端。

-

PCI

+关注

关注

5文章

689浏览量

134482 -

总线

+关注

关注

10文章

3057浏览量

91864

原文标题:【博文连载】PCIe扫盲——PCI-X总线基本概念

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCI PCI-X PCI-E介绍 精选资料分享

PCI-X Initiator/Target Core pd

PCI-X总线FPGA开发板资料说明

从PCI、PCI-X到PCI-Express之间的连接

基于PCI总线的信号定义

LSISAS3080X-R PCI-X到3.0 Gbit/s SAS主机总线适配器安装

关于PCI总线和PCI-X总线的简要介绍

关于PCI总线和PCI-X总线的简要介绍

评论