PCB应用广泛,但由于成本以及技术的原因,PCB在生产和应用过程中出现了大量的失效问题,并因此引发了许多质量纠纷。为了弄清楚失效的原因以便找到解决问题的办法和分清责任,必须对所发生的失效案例进行失效分析。

沉锡焊盘上锡不良失效分析

1.背景:

送检样品为某PCBA板,该PCB板经过SMT后,发现少量焊盘出现上锡不良现象,样品的失效率大概在千分之三左右。该PCB板焊盘表面处理工艺为化学沉锡,该PCB板为双面贴片,出现上锡不良的焊盘均位于第二贴片面。

2.分析说明:

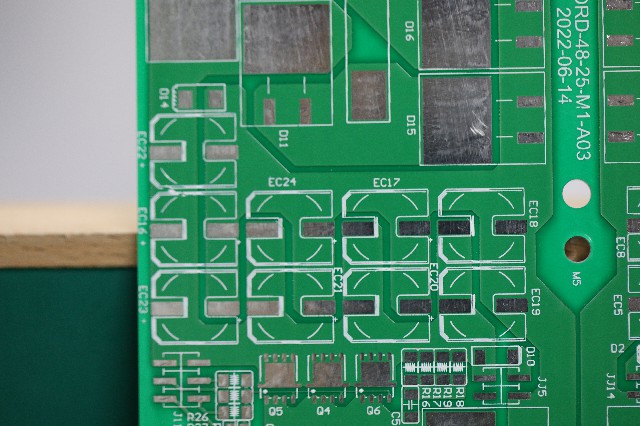

首先进行外观检查,通过对失效焊盘进行显微放大观察,焊盘存在不上锡现象,焊盘表面未发现明显变色等异常情况,结果如图1所示:

图1 失效焊盘

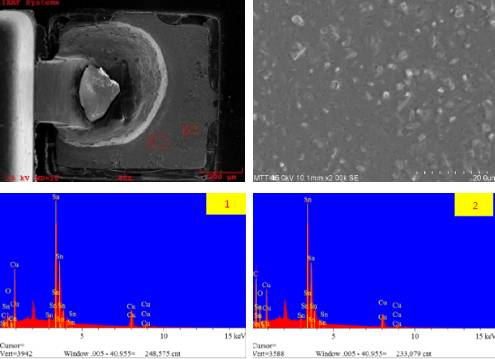

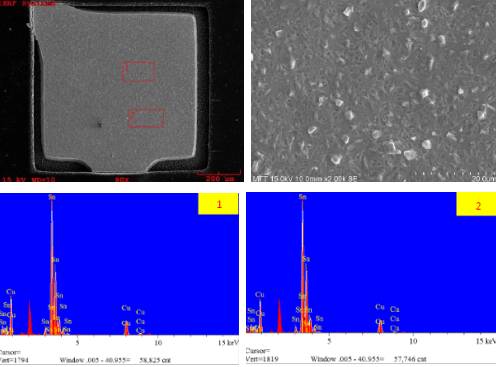

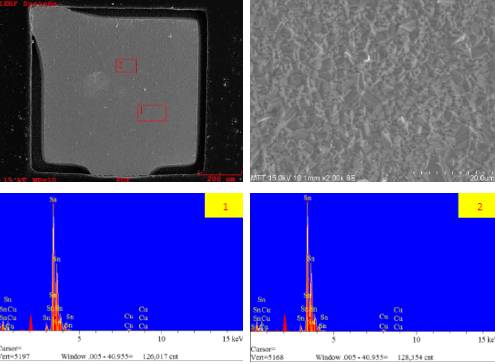

再对NG焊盘、过炉一次焊盘、未过炉焊盘分别进行表面SEM观察和EDS成分分析,未过炉焊盘表面沉锡层成型良好,过炉一次焊盘和失效焊盘表面沉锡层出现重结晶,表面均未发现异常元素,结果分别如图2、3、4所示:

图2 NG焊盘的SEM照片及EDS能谱

图3 过炉一次焊盘的SEM照片+EDS能谱图

图4 未过炉焊盘的SEM照片+EDS能谱图

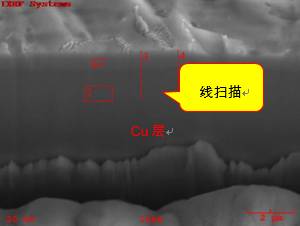

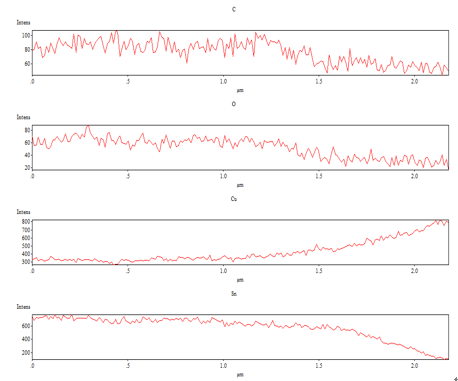

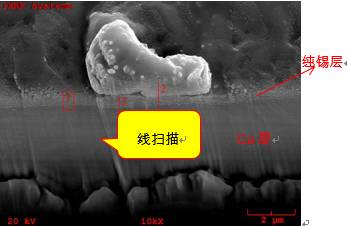

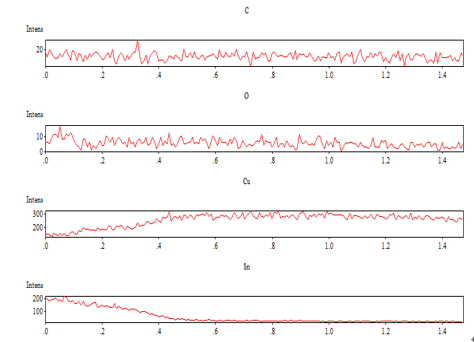

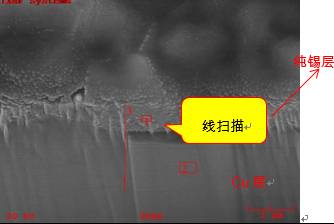

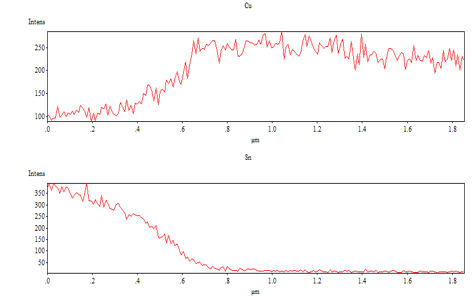

再利用FIB技术对失效焊盘、过炉一次焊盘及未过炉焊盘制作剖面,对剖面表层进行成分线扫描,发现NG焊盘表层已经出现Cu元素,说明Cu已经扩散至锡层表面;过炉一次焊盘表层在0.3μm左右深度出现Cu元素,说明过炉一次焊盘后,纯锡层厚度约为0.3μm;未过炉焊盘的表层在0.8μm左右深度出现Cu元素,说明未过炉焊盘的纯锡层厚度约为0.8μm。鉴于EDS测试精度较低,误差相对较大,接下来采用AES对焊盘表面成分进行进一步分析。

结果如图5、6、7所示:

图5NG焊盘剖面的SEM照片及EDS能谱

图6过炉一次焊盘剖面的SEM照片+EDS能谱图

图7 未过炉焊盘剖面的SEM照片+EDS能谱图

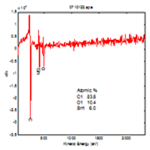

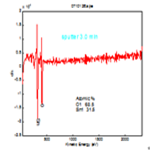

最后对NG焊盘和过炉一次焊盘的极表面成分进行分析,NG焊盘在0~200nm深度范围内,主要为Sn、O元素,200~350nm深度范围内,为铜锡合金,几乎不存在纯锡层;过炉一次焊盘在0~140nm深度范围内主要为锡层,之后出现元素Cu(金属化合物),结果如图8~15所示:

图8.NG焊盘测试位置

图9.NG焊盘极表面的成分分析图谱

图10.NG焊盘表面(约50nm深度)的成分分析图谱

图11.焊盘表(0~350nm深度)的成分分布曲线

图12.过炉一次焊盘表面成分分析位置示意图

图13.过炉一次焊盘表面的成分分析图谱

图14.过炉一次焊盘表面

(约50nm深度)的成分分析图谱

图15.过炉一次焊盘表面(0~220nm)深度的成分分布曲线

过炉3次焊盘切片示意图

结论: 由上述分析可知,NG焊盘在SMT贴装前已经过完一次炉,在过炉过程中,表层锡会被氧化,同时高温加剧锡与铜相互扩散,形成铜锡合金,使铜锡合金层变厚,锡层变薄。当锡层厚度小于0.2μm,焊盘将不能保证良好的可焊性,出现上锡不良失效。

-

PCB板

+关注

关注

27文章

1503浏览量

55522 -

焊盘

+关注

关注

6文章

605浏览量

39886

原文标题:[技术分享]PCB板上锡不良失效分析案例

文章出处:【微信号:pcbems,微信公众号:PCB商情】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB板上沉锡焊盘上锡不良失效分析

PCB板上沉锡焊盘上锡不良失效分析

评论