EDA软件中allegro的模块复用非常实用,可能通常我们的PCB工程师还用的不多,但它在某些场合下还是很有用的,一个是它能减少我们重复性的工作,可以重用的原理图和PCB我们就不需要重复设计了,也就是REUSE。

以下给大家讲解详细操作:

1、在orcad中画好模块的原理图,设定好封装,做好drc,做好元件编号。

2、检查元件属性是否设为current properties,其它设定可能出错。

3、在annotate-->allegro reuse中,选中generate reuse module,renumber design for using modules,选中unconditional,其它不选。

4、生成netlist.

5、将netlist导入到allegro,布线,布局,若无rename等需要与orcad交互的动作,选tools-->creat modules生成mdd文件.mdd文件的文件名一定要定义为:DSN NAME_ROOT SCHEMATIC NAME.mdd。DSN NAME为你定义的orcad中的dsn文件名,ROOT SCHEMATIC NAME是这个文件中的页名字。这里若定义不对,在reuse时找不到mdd文件。之后跳到第6步。

6、在orcad中back annotate,之后回到第2步。

7、模块制作完成。

使用生成的模块

1、在新的orcad设计中,选place-->herarhical block,reference中填入BLK?(注意,这里使用BLK是为了与原理图中的U?R?C?区别,保证BLK这个名字专用于moduel,不然在做完allegro后,rename 时,导回到orcad中出问题。)在implementation type中选schematic view,在implementtation name中填入先前模块的页名称,在path and file name中选择相应的dsn文件,之后在你的原理图中出现一个block.

2、继续其它设计,之后在annotate-->packageing中,选中reset part name to "?",同时选中update occurrences,执行一下,将所有的元件(包括module的name改为?),在annotate-->allegro reuse中,选中 renumber design for using modules,选中incremental,选中do not change the page number,选中select modules to mark for框里的内容。其它不选。

3、drc后,出netlist.

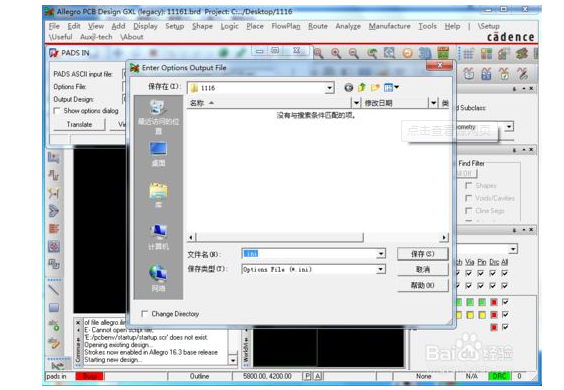

4、导入到allegro后,palce-->manually place,选mudule instances,将module放入。注意一下mdd文件路径的设定,不正确会找不到mdd 文件的。

5、在allegro中布好线后,可以rename到arcad中,与正常设计无区别。

6、over.

做reuse时的几个注意事项:

1:当reuse模块已经放在电路中使用,重新修改reuse模块的port口后,在使用的原理中右击这个模块,选synchronize up,则实现修改的同步。

2:在reuse模块中,不能使用room属性,不然可能与使用reuse的电路图混淆。

3: reuse模块中不能使用全局变量,特别是电源和地,使用port口传递数据。

4: reuse模块内部修改后,只要port口没有变,则在使用它的原理图不用同步。

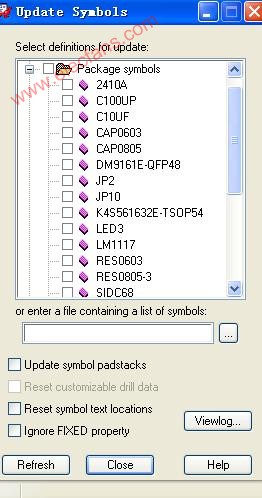

5: 做好的模块文件用在pcb中后,若需要修改这部分文件,在修改完成后,在原pcb中使用update symbol功能,选相应的moddle,之后更新就行了,注意生成mdd文件时,原点的选择,这然更新后一些线会错位。

6:当导入到allegro的模块出现dummy net的错误时,怎么办?

出错的可能原因是由于模块的orcad文件造成的,可能是对原始的orcad取一部分进行修改,这些元件带有原来文件的一些属性。将相关orcad文件的所有元件和连线copy到一个新的页内,将当前页的内容删除,从刚才copy到新页的内容copy回来,这时看元件的属性时,没有黄色的部分,按正常步骤重新生成mdd文件,在调用这个模块的orcad文件中,重新编一次元件编号,生成网表,问题解决。

7:当含有reuse的设计导入到allegro并布线完成,若重新修改原理图,比如换一个10pin的IDC插座到16pin,不能用annotate-->allegro reuse命令,不然生成的网表会导入到allegro中会出错,不知是什么原因?

答:在原理图设计中,当使用reset to ?后,使用annotate-->allegro reuse命令,将netlist导出到allegro后,不能再使用使用reset to ?,新增的元件使用increase功能,不要将所有的元件reset to ?,不然会出错。

-

PCB设计

+关注

关注

394文章

4688浏览量

85601 -

eda

+关注

关注

71文章

2758浏览量

173244 -

PCB工程师

+关注

关注

1文章

22浏览量

7760 -

可制造性设计

+关注

关注

10文章

2065浏览量

15550 -

华秋DFM

+关注

关注

20文章

3494浏览量

4516

发布评论请先 登录

相关推荐

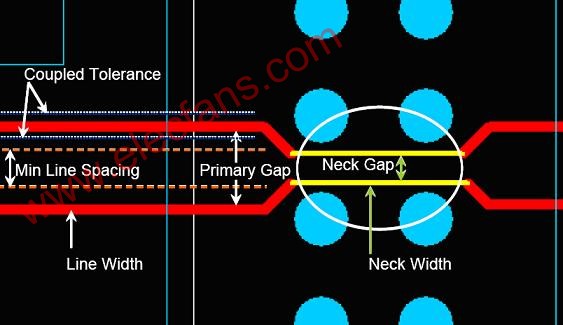

教你设置Allegro差分线

也谈PADS的reuse功能

PADS通过Add Reuse拼板出现错误

PADS使用复用(Reuse)功能的一些体会

在allegro中实现铜皮挖字,填补allegro功能空白

Pads-Make_reuse模块电路复用功能简析

Allegro软件的菜单功能介绍

Allegro 16.2 新功能介绍

教你在allegro中更换元件封装

allegro 软件常用功能

教你使用allegro 的reuse功能

教你使用allegro 的reuse功能

评论