设备上的各种外拖电缆就是贯通屏蔽机箱的导体。

设计师们想到的,解决这些电缆的电磁辐射问题的基本方法就是屏蔽。但是,在实际中,通过屏蔽获得理想效果的情况却很少。这是因为没有了解屏蔽解决电缆辐射的本质。

图中所示的是一个导体贯通屏蔽界面的情况。为了防止内部电磁场通过这根导体泄漏,我们将屏蔽界面右侧的导体屏蔽起来。

可以看到,这时,实际上可以看成屏蔽界面外延了一部分,实际上不存在贯通导体穿过屏蔽界面的情况,当然也就没有电磁泄漏了。

我们还可以从共模电流路径的角度解释屏蔽的效果。当有了附加的屏蔽以后,导体上的共模电流就可以通过这个附加的屏蔽体返回骚扰源,这个路径显然比原来的路径小得多,因此,也就产生更小的电磁辐射。

请大家注意一个细节,这就是,无论哪种机理,都需要一个保证条件,这就是附加的屏蔽体与原来的屏蔽体之间必须导电连接,否则,机构不成一个完整屏蔽体,也不能为共模电流提供一个返回的路径。

实际上,两个屏蔽体之间的搭接十分重要,理想的情况是360度(一周)连续搭接。

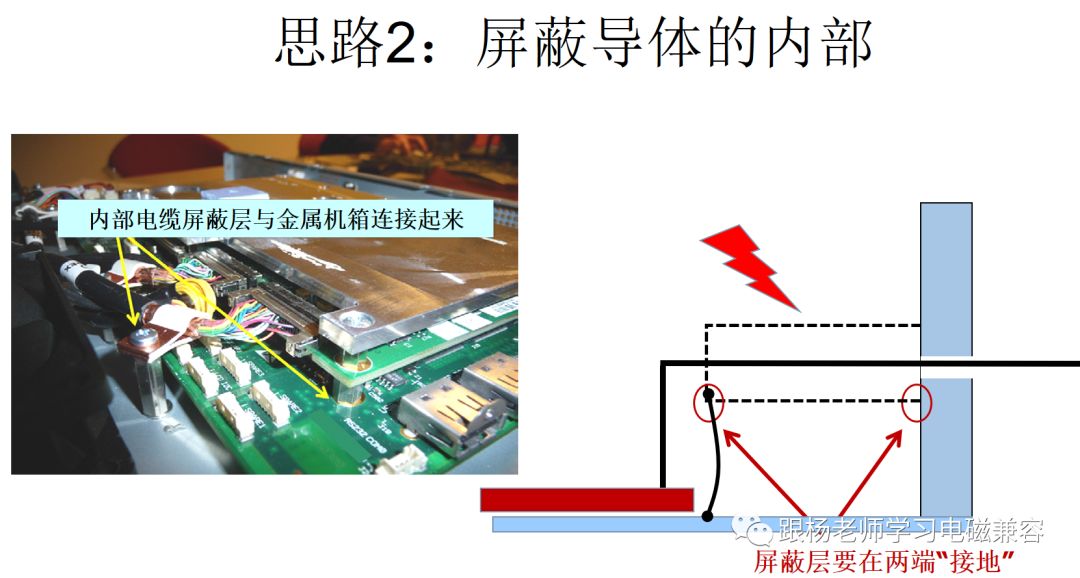

对设备内部的导体部分进行屏蔽也能起到同样的效果。

右图是对贯通导体内部进行屏蔽的情况。由于附加的屏蔽,削弱了内部电磁场在导体上感应的电压,因此,也就减小了电磁泄漏。

这里同样需要注意附加屏蔽体的“接地”,也就是与原来屏蔽体之间的导电连接。附加的屏蔽体应该在两端接地,并且保证搭接阻抗尽量低。

左图是一个实际的内部电缆屏蔽的例子,这里,屏蔽层通过良好的压接,保证了低阻抗接地。

在内部对贯通导体(电缆)进行屏蔽往往效果不够满意,其中的一个原因是,电缆总是与PCB上的电路连接在一起的,即使我们将电缆屏蔽起来,PCB还暴露在外边,因此,不可能彻底消除感应电压,除非将PCB一起屏蔽起来。

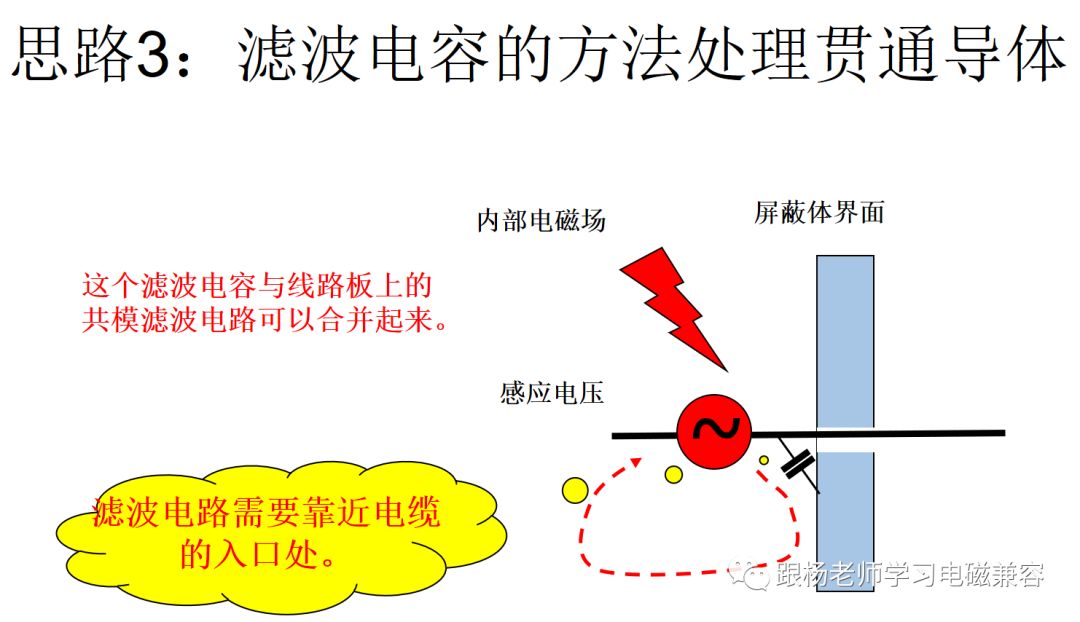

一种十分有效的方法是,在贯通导体穿过屏蔽界面的位置,在贯通导体与屏蔽界面之间安装一个高频电容,这时,贯通导体的电磁泄漏就会大幅度减弱。

这个方法的原理如图所示。

前面我们分析贯通导体的电磁泄漏时,分析了共模电流的路径,导体与屏蔽界面之间的杂散电容是共模电流路径的重要组成部分。

现在,我们有意识地提供了一个电容,就改变了原来的共模电流路径。这个新增加的电容为共模电流提供一条返回骚扰源的路径,因此,共模电流不会沿着导体传导到屏蔽界面的另一侧,也就不会导致电磁泄漏。

具体多少电流会从这个新增加的电容分流,取决于着新增加的电容提供的路径阻抗与原来的共模电流路径阻抗比值。这类似于我们计算电阻并联电路时,两个电阻的电流的情况。

原来的路径阻抗越高,新增加的电容的效果越明显。原来的共模电流路径的阻抗与电缆的长度,铺设方式等因素有关。

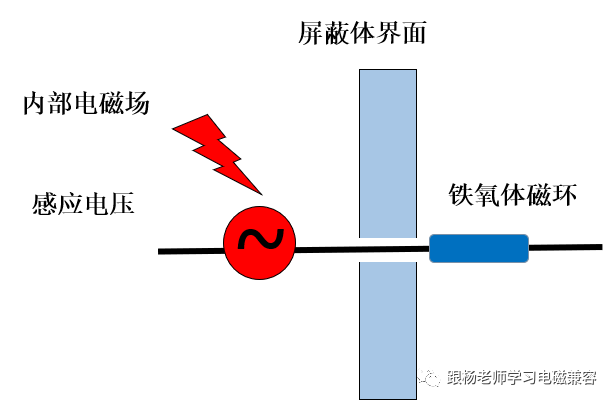

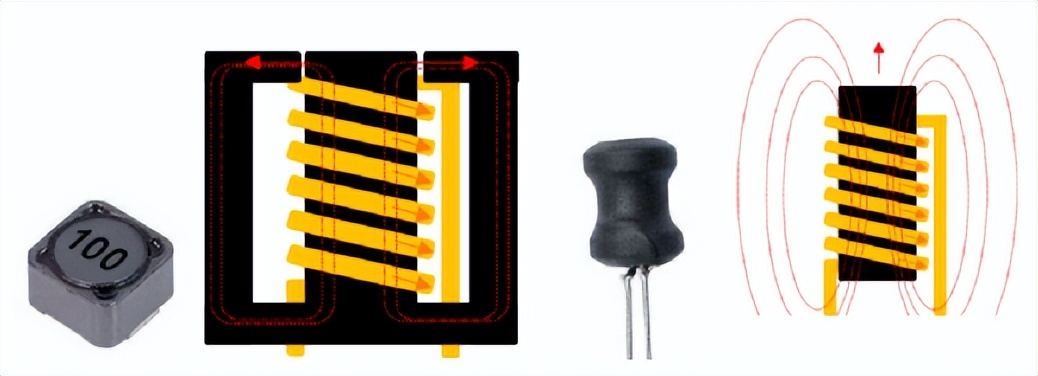

有时,我们在电缆上套上一个铁氧体磁环,实际上起着增加外部回路阻抗的作用。

我们通过一个实例是大家加深对前面所提的滤波电容方法的认识。

左图是一个实验装置。在一块PCB上安装一个时钟电路。前面我们知道,时钟电路是最典型的骚扰源电路,因此,我们一般用这种电路来做实验。

我们用一个电流钳来监测电源线上的共模电流。

右图是用来监测共模电流的频谱分析仪和电流钳。频谱仪上显示的共模电流的频谱。

通过监测电缆上的共模电流来间接预测电缆的辐射是一个非常有用的方法,设计师们应该熟悉,并能够熟练应用。

后面,我们会给出从共模电流预测辐射的方法。

左图是在电源线与金属外壳之间连接了一个电容的情况。

图中的红色圆圈内,显示的是,用鳄鱼夹把电容连接到金属外壳上的状态。右图的频谱分析仪屏幕上显示的是这时候的共模电流情况。

可以看到,共模电流的幅度已经大幅度降低。这说明,一部分共模电流被电容分流掉了,没有传导到外部电源线上。

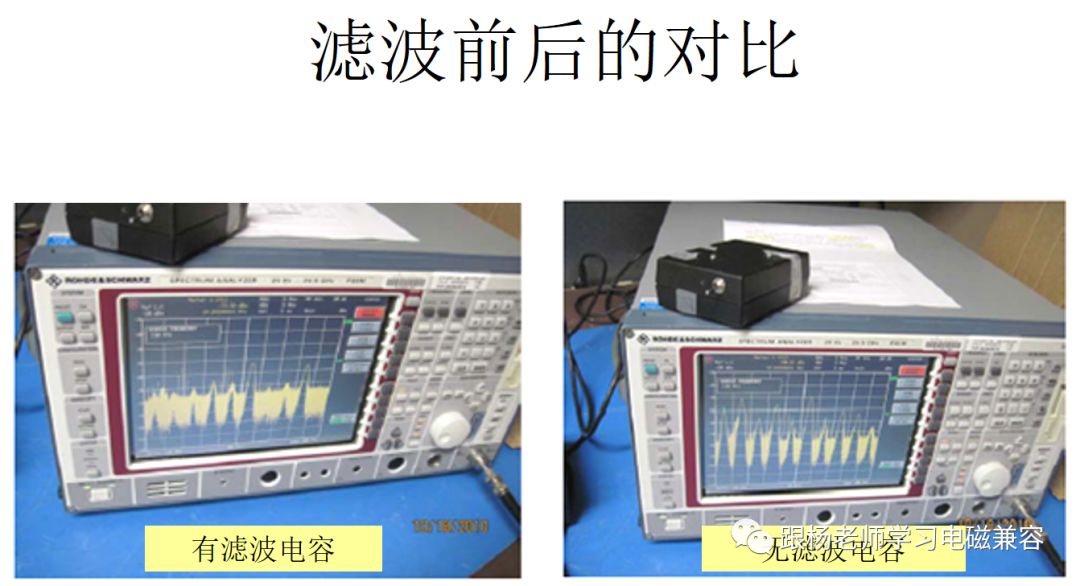

为了使大家便于比较滤波前后的情况,我们有滤波,没有滤波的两种情况下的共模电流频谱放在一起。

左边是有滤波电容的情况,右边是没有滤波电容的情况。他们之间的差异一目了然。

思考题:

某设备由于有贯通屏蔽体的导体,辐射发射超标。设计师在导体上套了一个铁氧体磁环,请预测这个铁氧体磁环能将辐射降低多少?

-

电缆

+关注

关注

18文章

2769浏览量

55338 -

emc

+关注

关注

170文章

3986浏览量

184351 -

屏蔽

+关注

关注

1文章

96浏览量

18983

原文标题:顺利通过EMC试验(三十)文字版

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

探秘 EMC 本质:比创达为你解析 EMC 设计整改核心原理与解决方案

EMC/EMI电磁兼容设计中抗干扰滤波器的作用

【EMC家园】滤波器对EMC的帮助!

屏蔽电缆的作用是什么

EMC电磁兼容测试有哪些方法、仪器和试验场所?

EMC中屏蔽线失效案例描述

电缆屏蔽层的作用 电缆屏蔽层的种类和使用场景

案例17:由电缆布线造成的辐射超标

EMC试验:了解屏蔽解决电缆辐射的本质

EMC试验:了解屏蔽解决电缆辐射的本质

评论