▍本文描述了Cadence® Sigrity™产品QIR2 的新增功能。

本节介绍Cadence® Sigrity™ 2017 QIR2版本中XtractIM™的新增功能。

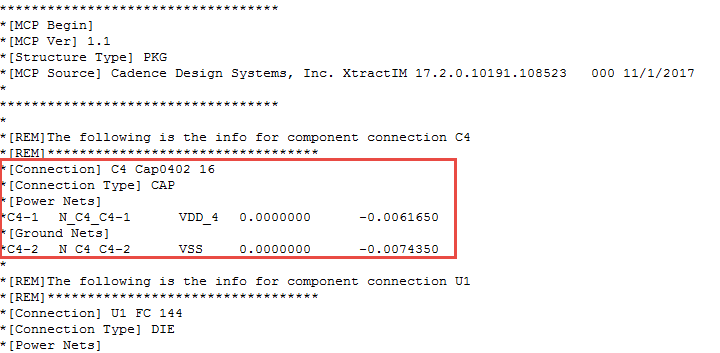

在MCP header中添加了去耦电容引脚

在该版本中,去耦电容的引脚信息被添加到由XtractIM生成的SPICE模型的MCPheader中。

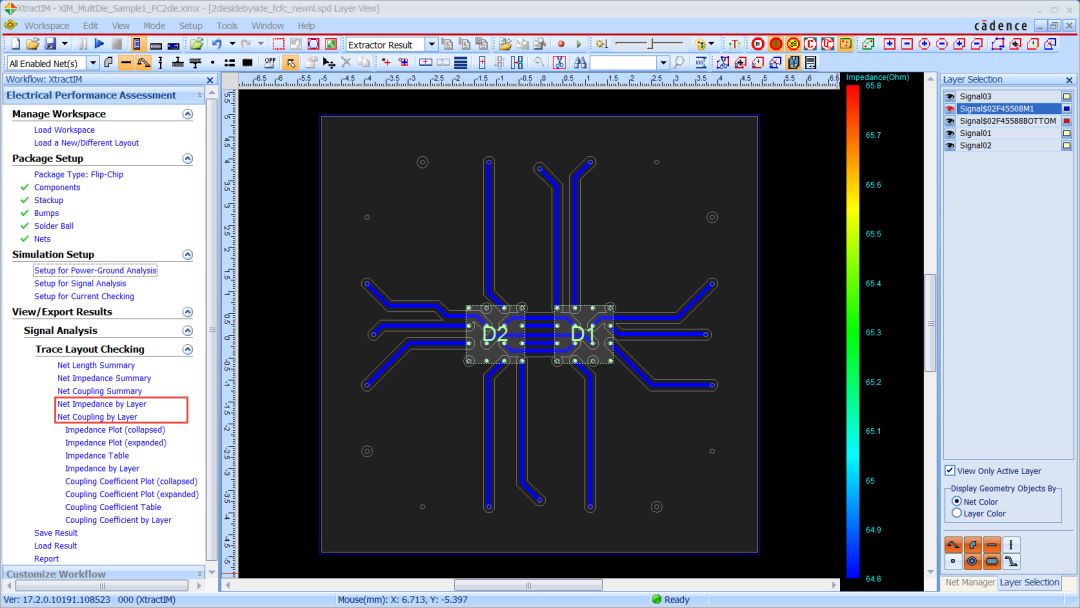

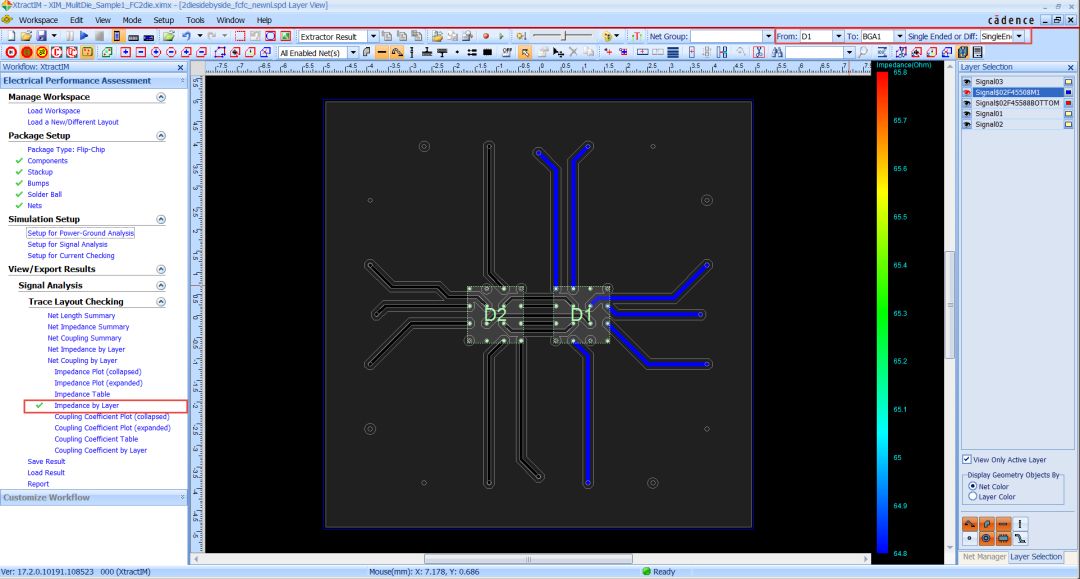

添加了新的选项来显示所有网络的阻抗和耦合结果,用于多Die封装设计

在该版本中,EPA模式中增加了一个新选项,用于显示多Die IC封装设计中所有网络的阻抗和耦合系数。

在以前的版本中,每层每次只能显示一个DIE到BGA的阻抗结果。

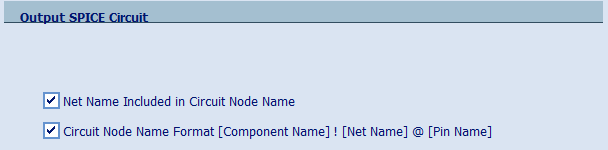

基于引脚的SPICE模型中增加了用于电路节点命名的新选项

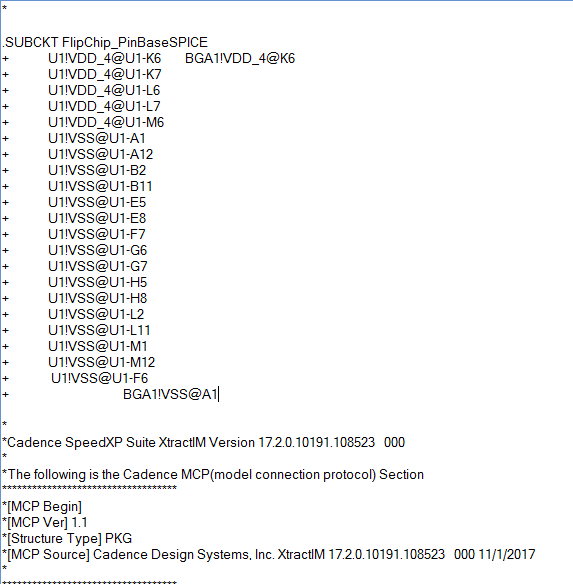

在该版本中,添加了一个新的选项Circuit Node Name Format [Component] ! [Net Name] @ [Pin Name] 以提供另一种方法来定义电路节点名称的分隔符号。

选择此选项时,元器件名称和网络名称由!分隔,网络名称和引脚名称由@分隔。

在以前的版本中,基于引脚的SPICE模型中用于电路节点命名规则的分隔符号是下划线(_)。例如,U1_U1-A1。

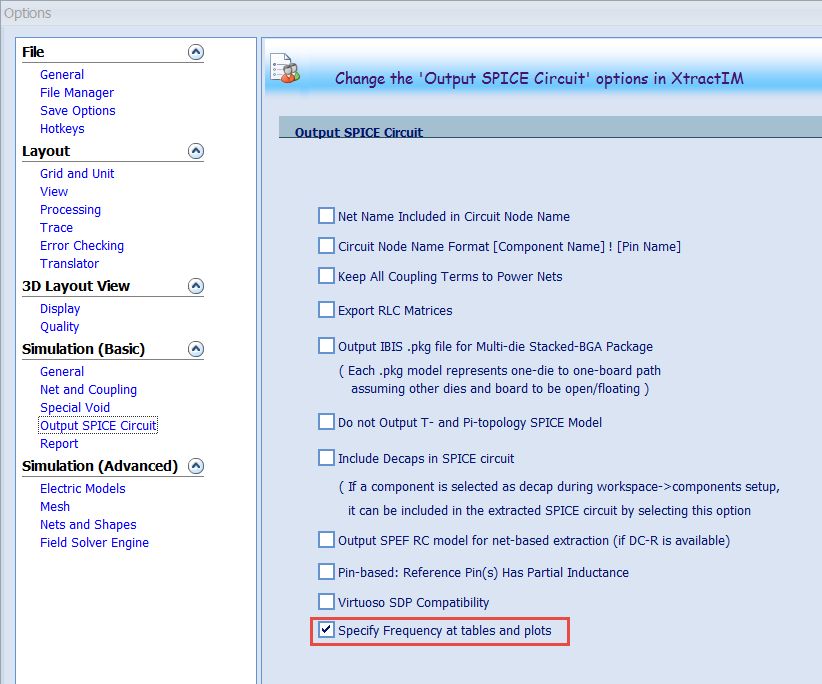

添加新选项用于在RLC报告中显示提取频率

新增加了在表格和图形结果中显示频率的选项,用于以GUI或者report方式查看仿真结果时,显示RLGC提取频率。

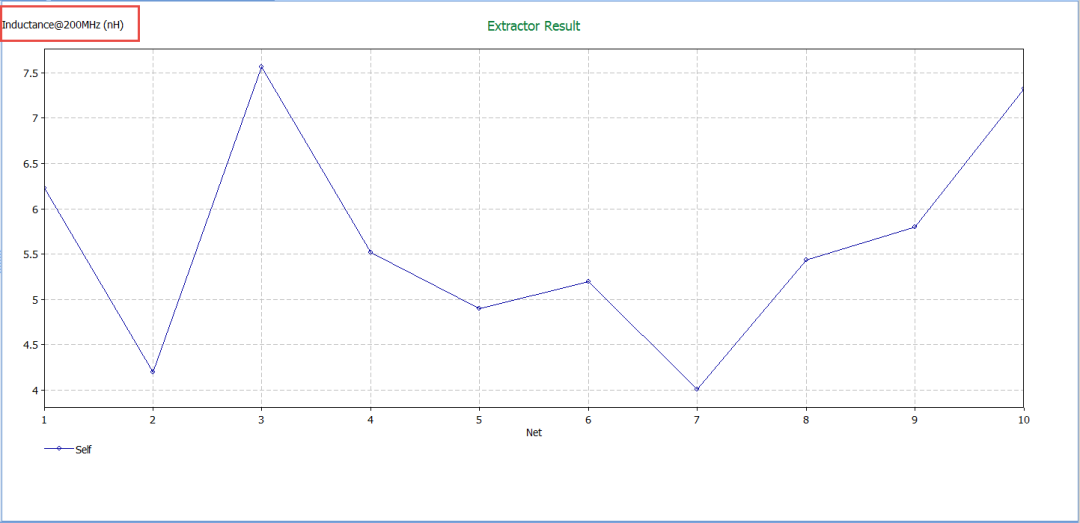

每个网络的RLC:

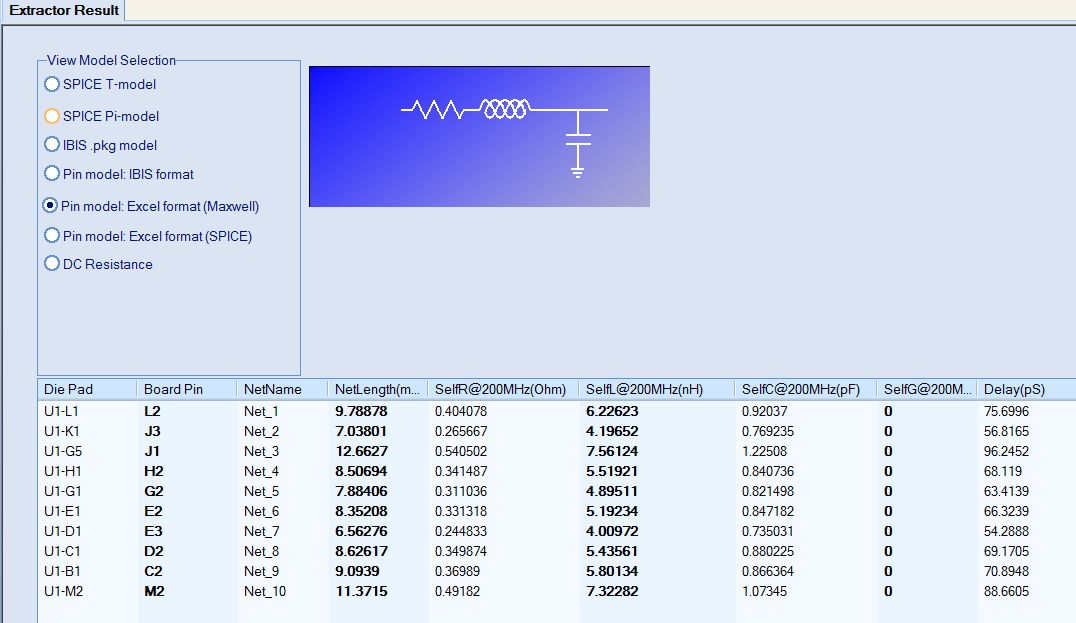

RLC表格:

添加了新的Tcl命令

模型提取模式中添加了以下新的Tcl命令:

-

导出耦合项的阈值

-

优化的带宽

-

电路拓扑

-

提取的频率范围

-

-

Cadence

+关注

关注

65文章

931浏览量

142555 -

SPICE

+关注

关注

6文章

187浏览量

42778

原文标题:Cadence Sigrity QIR2 更新 | XtractIM

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文读懂什么是「雷电4」

SOLIDWORKS 2025设计新增功能

HyperLynx 2409的新增部分功能

HyperLynx 2409新增功能和改进功能

Cadence 扩充系统 IP 产品组合,推出 NoC 以优化电子系统连接性

Cadence扩充系统IP产品组合,推出NoC以优化电子系统连接性

电主轴:教您如何一文读懂?|深圳恒兴隆机电.

Cadence 扩充 Tensilica Vision 产品线,新增毫米波雷达加速器及针对汽车应用优化的新款 DSP

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析

一文读懂Cadence® Sigrity™产品QIR2 新增功能

一文读懂Cadence® Sigrity™产品QIR2 新增功能

评论