在ARM体系中,通常有以下3种方式控制程序的执行流程:

• 在正常程序执行过程中,每执行一条ARM指令,程序计数器寄存器(PC)的值加4个字节;每执行一条Thumb指令,程序计数器寄存器(PC)的值加2个字节。整个过程是顺序执行。

• 通过跳转指令,程序可以跳转到特定的地址标号处执行,或者跳转到特定的子程序处执行。其中,B指令用于执行跳转操作;BL指令在执行跳转操作的同时,保存子程序的返回地址;BX指令在执行跳转操作的同时,根据目标地址的最低位可以将程序状态切换到Thumb状态;BLX指令执行3个操作:跳转到目标地址处执行,保存了子程序的返回地址,根据目标地址的最低位可以将程序状态切换到Thumb状态。

• 当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。在当异常中断处理程序执行完成后,程序返回到发生中断的指令的下一条指令处执行。在进入异常中断处理程序时,要保存被中断的程序的执行现场,在从异常中断处理程序退出时,要恢复被中断的程序的执行现场。

ARM体系中异常中断种类:

• 复位(Reset):当处理器的复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。复位异常中断通常用在下面两种情况:系统加电时和系统复位时。跳转到复位中断向量处执行,称为软复位。

• 未定义指令(Undefined Instruction):当ARM处理器或者是系统中的协处理器认为当前指令未定义时,产生未定义的指令异常中断。

• 软件中断(Software Interrupt SWI):这是一个由用户定义的中断指令。可用于用户模式下的程序调用特权操作指令。在实时操作系统中可以通过该机制实现系统功能调用。

• 指令预取中止(Prefetch Abort):如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,当该被预取的指令执行时,处理器产生指令预取中止异常中断。

• 数据访问中止(Data Abort):如果数据访问指令的目标地址不存在,或者该地址不允许当前指令访问,处理器产生数据访问中止异常中断。

• 外部中断请求(IRQ):当处理器的外部中断请求引脚有效,而且CPSR寄存器的I控制位被清除时,处理器产生外部中断请求(IRQ)异常中断。系统中各外设通常通过该异常中断请求处理器服务。

• 快速中断请求(FIQ):当处理器的外部快速中断请求引脚有效,而且CPSR寄存器的F控制位被清除时,处理器产生外部中断请求(FIQ)异常中断。

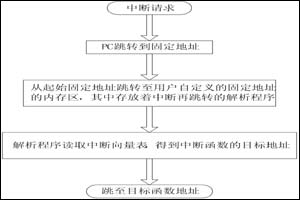

对异常中断的响应过程(这几点都是ARM核自己已经完成的动作):

• 保存处理器当前状态、中断屏蔽位以及各条件标志为。这是通过将当前程序状态寄存器CPSR的内容保存到将要执行的异常中断对应的SPSR寄存器中实现的。各异常中断有自己的物理SPSR寄存器。

• 设置当前程序状态寄存器CPSR中相应的为。包括:设置CPSR中的位,使处理器进入当前相应的执行模式(处理器模式);设置CPSR中的位,禁止IRQ中断,当进入FIQ模式时,禁止FIQ中断。

• 将寄存器lr_mode设置成返回地址。

• 将程序计数器值(PC),设置成该异常中断的中断向量地址,从而跳转到相应的异常中断处理程序处执行。

从异常中断处理程序中返回(这些返回动作是需要自己写代码完成的):

• 恢复被中断的程序的处理器状态,即将SPSR_mode寄存器内容复制到CPSR中。

• 返回到发生异常中断的指令的下一条指令执行,即将lr_mode寄存器的内容复制到程序计算器PC中。

复位异常中断处理程序不需要返回。在复位异常中断处理程序开始整个用户程序的执行,因而它不需要返回。

-

寄存器

+关注

关注

31文章

5387浏览量

121558 -

ARM处理器

+关注

关注

6文章

361浏览量

42009

原文标题:ARM异常中断处理

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ARM处理器中断处理的编程实现

ARM S3C4510B系统的异常中断机制解析

ARM体系中异常中断种类及处理办法

ARM体系中异常中断种类及处理办法

评论