张飞与弟子精彩技术探讨 郑同学之电路逻辑篇

在上期连麦某某同学后,另一个同学成功抢麦,问:“老师,我可以发言吗?”

张飞老师笑着说:“当然可以。按F2,郑同学你可以讲话了。”

“我觉得这个电路的逻辑有点问题。”

“讲。”

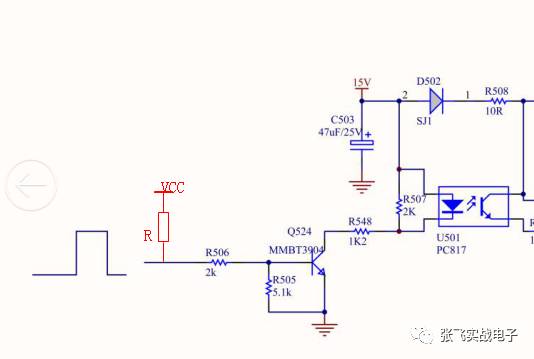

这位大胆的同学说:“就是逻辑为高的时候,MOS管是关的,低的时候它为开,这个很容易出问题。假设我这个板子给软件工程师来调试,一上电会吓死人的。一般,单片机常用的引脚正常的情况下都是高电平工作,低电平关断,这个电路就是一个逻辑反了的状态。”

张飞老师微微点着头说:“OK,你说的这个问题很好。这个电路确实是反逻辑的,然而反逻辑的电路,上电的时候是不是就会炸?就会出现问题?现在我这里有一个问题,假设这就是反逻辑的,那么单片机上电考虑的是三态,你有没有什么办法让上电的时候不是三态呢?上电这里就要是高,输入这里就要是高,有没有办法?”

“可以啊,程序里面就可以做了,让他上电的时候让控制这个引脚默认为高电平或者低电平,软件里面是可以设置的。”

张飞老师接着问:“Ok,如果现在由于软件干扰的问题导致单片机一直处于复位状态,那这里不还就是出问题了吗?因为如果单片机在复位状态的话,软件都是没有执行的。没有执行意味着IO口配置为本来应该配高或者配低。如果你现在是一个高阻态啊,怎么办?你有考虑到这种情况吗?因为所有的板子都要做一些安规认证的,要去走ESD的公共群干扰等等这些东西。如果一个高压静电过来的时候你这个单片机复位了,后来这个单片机就挂掉了,后面是不是会出问题呢,如何解决这个问题呢?”

“如果按照这个逻辑的话我只能加上拉电路,就是一开始不管单片机是否稳定工作,最起码控制引脚这里是上拉的高电平,保证后面的电路是关断状态,就是可以避免单片机是反复循环复位这个状态,或者打EMC的时候有干扰这个状态,可以确保利用上拉来避免刚才的不稳定状态。”

“你这个想法相当的好,相当的ok,确实是的,就是说通过在IO口加上拉的方式来确保这个电平的稳态输出。

我们从电路的各种保护来说,很多电路都是软件来保护的,比如电流、电压、位置、温度、速度等等,当超过某个范围了要去进行一个保护或者说限制,要么是限制不要继续往上增长,要么就直接关掉,这种方式很多都是软件里面的。但是如果我们做安规认证的时候,你会发现它会要求你把软件里面的那些保护全部给撤销掉,看硬件能不能保护,这时我们就会发现真正的保护是要靠硬件保护的,不能完全去信赖软件。也就是说更主要的电路安全还是要靠硬件去保障的,软件里面的保护是锦上添花。

但是硬件的保护是属于最后的一个保护,我们说要有硬件保护,也要有软件保护。那么这种情况下一般有两个阈值,首先一个阈值,肯定是软件去保护,软件先去保护,在软件没有去保护的情况下,达到硬件的阈值,硬件才会去保护。一般是有两种阈值保护状态,这样就做到软硬结合去保护。在这个地方通过上拉的方式确保高电平出现,这是一个很好的方法,你这边确实考虑到了。我们很多人在设计电路的过程中并没有考虑单片机复位这段时间是个什么状态,只考虑单片机正常工作之后应该是什么状态,这样的电路在来回的启动过程中往往会出现问题,这个是需要去考虑的问题。

-

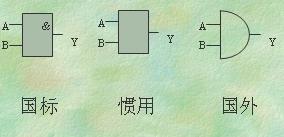

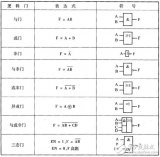

逻辑电路

+关注

关注

13文章

503浏览量

44299 -

MOS

+关注

关注

32文章

1800浏览量

101419

原文标题:张飞老师讲解电路逻辑,新思路启发疑惑的你

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新形势下数字逻辑电路教学实践探讨

组合逻辑电路的分析与设计-逻辑代数

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别

组合逻辑电路中的危害

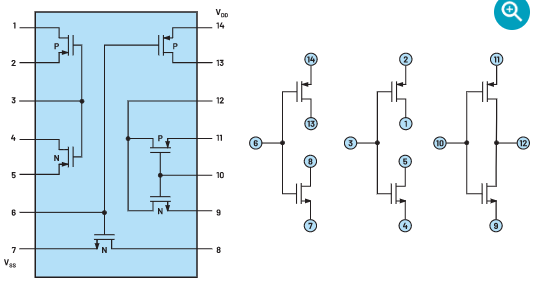

CMOS逻辑电路、传输门XOR

电路逻辑问题的探讨

电路逻辑问题的探讨

评论