随着电子技术的发展,在系统设计中对信号频率的稳定度和准确度要求越来越高,一般的LC,RC 振荡器已不能够满足要求。晶体振荡器的高精度与高稳定度刚好满足了这一要求,但其频率单一,且频率值不高。于是出现了以这一稳定频率为核心的,同时能产生大量具有相同精度和稳定度频率的方法,这就是频率合成“。 它用个高稳定度和高准确度的标准频率源作为参考,通过对频率进行加、减、乘、除运算,产生大量的同一稳定度和准确度的不同频率。频率合成器是电子设备的重要组成部分,是影响电子设备系统性能的关键因素之一。

一、国内外发展趋势

频率合成器在国外已经发展得相当成熟,形成了一系列的单片集成频综芯片,包括锁相式整数/ 分数频率合成器、直接数字频率合成器、双环或者多环锁相式频率合成器、DDS 与PL 混合式频率合成器。

美国National Semiconductor 的LMX243X 锁相式频综芯片的噪声基底已经达到- 219 dBc /Hz,而ADI 公司的ADF4107 工作频率可以达到7GHZ。目前,国内还没有生产单片双环或者多环锁相式频综的能力。

目前DDS 的杂散一般可以做到- 70dB 左右。AD 公司生产的单片集成DDS芯片AD9858 采样频率达到1GHz,最大输出为400MHZ。本世纪初出现的ROM-LESS 的DDS 方式,降低了电路功耗,是直接数字频率合成中最前沿的技术。国内采用0.35Hm 常规互补金属氧化物半导体电路( CMOS)C艺,研制出合成时钟频率达2GHZ 的新一代ROMLESS DDS 高速芯片。

国外混合式频率合成器所达到的技术指标是: DDS + DAS 合成方式下,转换速度可达IlHs,杂散分量- 65dBc,频率范[ 围10MHz~ 18GHz,步进间隔1F Iz,比较典型的代表是Wathing Johnson Company的WJ45 100 型频率合成器。 而在DDS+ PLL 合成方式下,转换速度可达100H,杂散分量-75dBc,相位噪声- l15dBc /Hz@ 10 kHz,频率范围500MHz~ 2 5 GHz,分段合成,步进间隔1Hz,比较典型的弋表是Commun icat ion Techniques Inc.的FSFR 频率合成器系列。

二、技术体制分析

频率合成技术主要分为三类: 直接模拟式频率合成技术( DAS)、直接数字式频率合成技术(DDS) 和间接琐相式频率合成技术( PL)。

各种体制的合成器具有相应特点: 直接模拟式频率合成器技术是以一个或多个高稳定参考信号为基准,通过倍频、分频、混频及开关滤波放大等多种方法组合而成的一种频率综合器,具有频率稳定度高、频率转换速度快、相位噪声低等优点,但系统复杂、体积大、成本高、并且因混频环节多容易引起较高的杂散电平,通常使用于频率点较少、相位噪声要求高的场合。

直接数字频率合成技术是近年来刚刚发展起来的一种新型频率合成技术,它具有频率转换速度快、相位噪声低、相位连续和极高的频率分辨率、体积小、重量轻等优点,主要缺点是工作频段较低、频段较窄,不能直接用于宽带微波频段,通常用于基带信号的产生。

间接锁相式频率合成技术是利用锁相环(PLL) 通过标准频率源来控制压控振荡器得到所需的频率,它具有电路简单、相位噪声低、输出频带宽和控制灵活等优点,但是由于环路滤波器的存在,使得其转换速度慢,一般使用于具有宽频带、较高频率分辨率要求的场合。

1、直接模拟式频率合成

直接模拟式频率合成是最早出现的一种频率合成器类型,其工作原理就是用倍频、混频电路对个或几个基准频率进行加、减、乘和除运算,从而产生所要求的频率信号,根据其合成方法分为相关合成和非相关合成两种。

直接模拟式频率合成器的优点是频率转换快(一般可以做到1~2Hs)、分辨率高、相噪低、输出频率高; 缺点是合成结构复杂、尺寸及重量大,且输出谐波、噪声及寄生频率难以抑制,适于频率步进大、点频数不多的电子系统。

2、锁相式频率合成

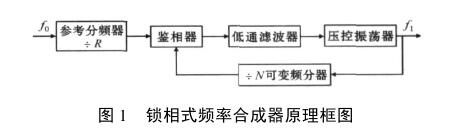

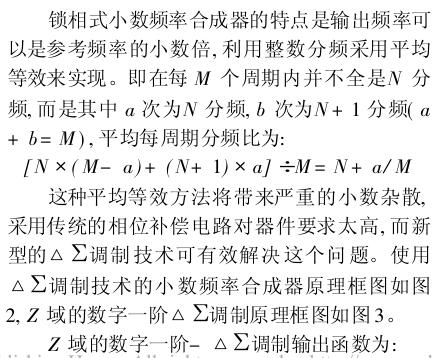

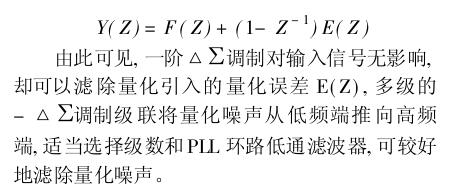

锁相式频率合成器是采用锁相环( PIL) 进行频率合成的一种频率合成器,其工作原理是将压控振荡器产生的射频信号和晶振输出的参考信号分别进行分频,得到两个频率近似相同的信号,并送到鉴相器进行比较,输出误差信号,经滤波后去控制压控振荡器的输出,使压控振荡器输出的射频信号保持稳定,工作原理如图1所示!

锁相式频率合成器分为整数频率合成器和小数频率合成器两种。整数频率合成器的频率分辨率为参考频率fr,为了获得较高的频率分辨率必然要减小fr,必然同时减小环路带宽( 为保证环路稳定,一般要求环路带宽小于参考频率fr 的十分之一),从而导致转换时间变长。因此,在实际应用中,为了获得较高的频率分辨率、快速转换时间和宽频带特性,通常采用多环频率合成技术和小数频率合成技术。多环频率合成器由多个锁相环路组成,其中高位环提供频率间隔较大的较高频率输出,低位环提供频率间隔较小的较低频率输出,将两部分输出相加,便可获得工作频率和频率分辨力高、转换速度快的合成信号输出。

锁相式频率合成器的优点是结构简单、体积小、易于集成、调试方便、杂散低,所以应用非常广泛,缺点是频率转换时间相对较长,难以满足对跳频时间要求快的电子系统。

3、直接数字式频率合成

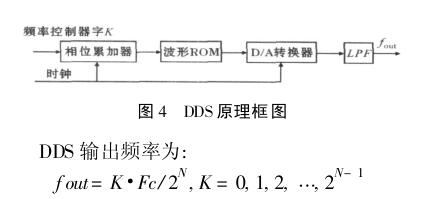

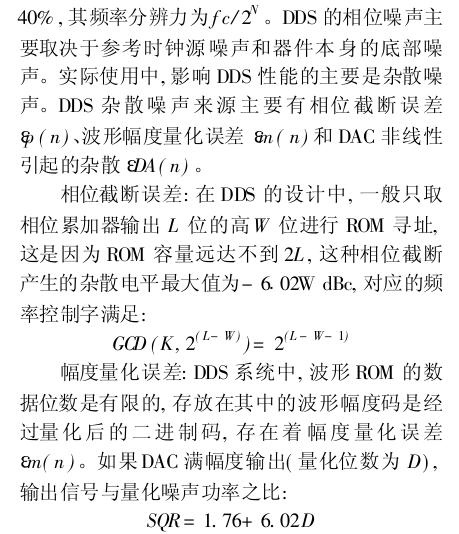

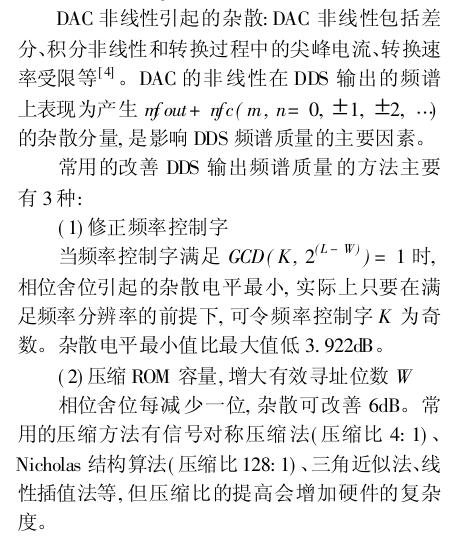

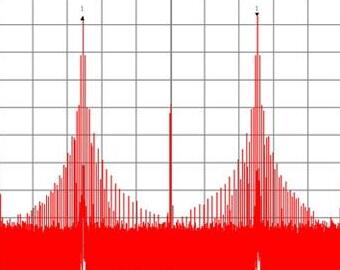

直接数字式频率合成( DDS) 技术是采用全数字化实现方式。近年来,随着集成电路工艺技术水平的提高,DDS 技术得到了迅速发展。DDS 主要由相位累加器、正弦波形表、D/A 转换器、低通滤波器组成,工作原理如图4。在系统时钟fc 的控制下,将频率控制字K 送到相位累加器,更新相位累加器的数据,然后把相位累加器中的数据N 作为地址对正弦ROM 表进行查询,通过改变相位增量就可以改变DDS 的输出频率值。由波形ROM 存储器取出的波形量化数据,经过A/ D 转换器转换成模拟电压/ 电流,再经过低通滤波器将波形中的高次谐波滤除,得到DDS 的输出频率。

(3) 扰码注入技术

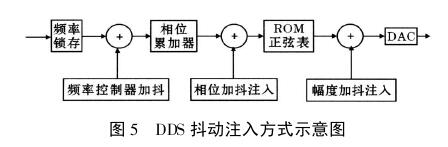

相位舍位引起杂散最根本的原因是$( n )是一个周期序列,因此破坏这种周期性成为减少DDS 杂散的主要研究方法。几种抖动主入的方法; 可以对频率控制字加抖; 可以对ROM 的寻址地址加抖,即相位抖动主入; 还可以对DAC 转换前的数据加抖,即幅度抖动主入,如图5 所示。

DDS 是- 一个全数字化的系统,具有易于集成、极快的跳频速度、极高的频率分辨率和频率切换时相位连续等优点,缺点是杂散比较大、输出频率低。

4、混合式频率合成

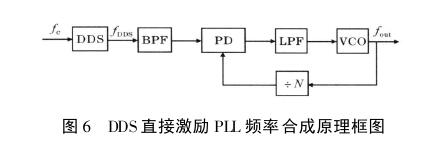

混合式频率合成是近几年非常流行的合成技术,主要有DDS 激励PLL.DDS 内插PLL.DDS+ 倍频( DAS)、DDS+ 混频几种合成方式。DDS 激励PLL 频率合成原理框图如图6。这种方案利用了DDS 的高分辨力来提高PLL 输出的频率分辨力和实现较高的频率输出,同时PLL 环路内的低通滤波器对带外DDS 杂散起到很好的抑制作用,但频率转换时间取决于PIL。

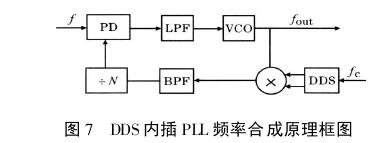

DDS 内插PLL 频率合成原理框图见图7。由于DDS 输出不经过PL 的倍频,使DDS引入的相位噪声和杂散不会使输出端恶化,具有低的相位噪声和良好的杂散性能,频谱纯度大大优于DDS激励PL,作!这种方案仍然基于PL,频率转换时间仍然很慢。

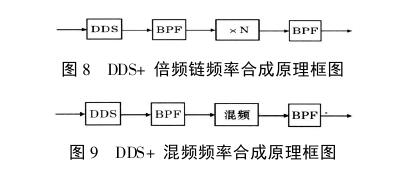

DDS+ 倍频频率合成原理框图见图8。用模拟倍频器代替PLL,克服了DDS+ PLL 的频率转换时间长的弱点,同时利用多个倍频器和滤波器组成的倍频链提高频综器输出频率,拓展了频综器的输出带宽。但随着输出频率扩高扩宽,输出滤波器的复杂度越来越大,甚至不能用单一滤波器而是要用开关、滤波器组件来实现,目前国内研制的超高速频率综合器大都采用了这种方案。缺点是输出带宽均不宽,一般只有几十兆赫。

DDS+ 混频频率合成原理框图如图9 所示,使用混频器将DDS 输出频率直接搬移到微波频段。第- 一级BPF 用来滤除DDS 的宽带杂散,第二级BPF 用来滤除本振频率、无用边带频率和其它无用的混频产物。本方案的优点在于DDS 本身的杂散电平和相位噪声不增加,且频率的捷变速度和分辨率均保持不变,即保持了DDS 的良好性能; 缺点在于输出频率范围窄(当DDS 输出频率范围超过一个倍频程时,其低频端二次谐波在混频器输出端变成杂散而无法滤除),且存在双边带输出、本振泄漏和其它混频产物。

三、结束语

频率合成技术从上世纪70年代开始,先后经历了直接模拟式( DAS)、间接锁相式、直接数字式(DDS): 三个阶段的发展。随着电子设备系统性能要求的不断提高,频率合成器技术也得到了快速发展,如体积小、性能高、高度集成的频率合成器以及将DDS 和锁相结合的混合式频率合成器逐渐成为发展趋势。同时,频率合成器的小型化、低成本、高性能、多品种特性,也进一步推动了各种军/ 民用电子系统的更新换代。

-

频率合成

+关注

关注

1文章

19浏览量

22011 -

频率合成技术

+关注

关注

1文章

4浏览量

6050

发布评论请先 登录

相关推荐

集成电源是电源技术发展的必由之路

浅析开关电源技术发展趋势

什么是集成无源元件?对PCB技术发展产生了什么影响?

光学活性中间体化学合成技术发展趋势

浅析低成本CMOS图像传感器对医学技术发展前景

锁相与频率合成技术图书下载

频率合成技术发展浅析

频率合成技术发展浅析

评论