OptimizePI

本节介绍Cadence® Sigrity™ 2017 OptimizePI™ QIR2 版本中的新增功能。

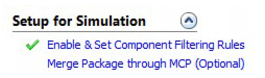

Post-Layout优化流程支持MCP封装模型

Sigrity的MCP(模型连接协议)是一个text header,被写入由Sigrity工具生成的模型中。它允许模型和物理layout之间的自动连接。“通过MCP协议合并封装”的步骤已经添加到Post-Layout分析工作流程中(去耦电容优化),这使得Post-Layout分析和PDN阻抗检查工作流程可以通过Switch Workflow功能保持一致性和便携性。

支持频率扫描,从0 Hz开始

对于一个典型的去耦电容优化,没有必要仿真到极低的频率,因为Bulk去耦电容主导着响应。然而,许多用户希望使用OptimizePI来提取其PDN的宽带模型。

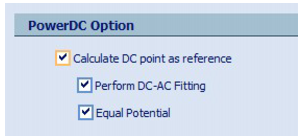

该新版本允许以0Hz作为起始频率,并且是推荐的最佳实践设置。请注意,还有其他高级选项可用于低频精确建模(PowerDC DC点计算,等电势选项和执行DC-AC拟合选项)。这些选项将起始频率锁定为0Hz。

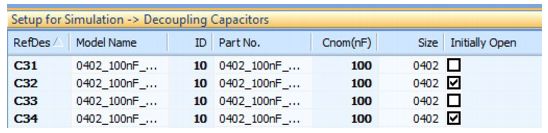

PDN阻抗检查流程中支持电容位置开路

由于各种原因,一些设计的去耦电容元器件在制造过程中可能或可能不会被放置。在此版本中,添加了在PDN阻抗检查工作流程中将去耦电容指定为初始开路(不放置)的功能。此功能以前在layout后分析(去耦电容优化)工作流程中执行。从这个版本开始,这两个工作流变得更具一致性和便携性。

从结果查看器中卸载阻抗曲线

此版本增加了卸载仿真后手动加载的阻抗曲线的功能。这为仿真结果分析和比较提供了更多的灵活性。可以通过在2D结果窗口右键单击并从快捷菜单中选择该选项来访问此功能。

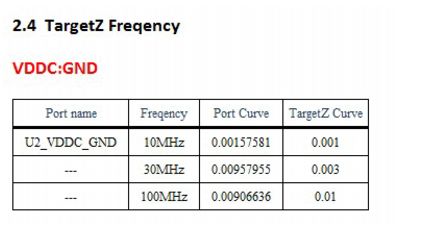

HTML报告中的定制频率设置,用于目标阻抗检查

目标阻抗检查是评判PDN性能pass/fail的极好指标。除了已经执行的连续曲线检查之外,OptimizePI还增加了在特定频率点报告阻抗结果的功能。这些频率点是在HTML报告选项窗口中定义的,如下所示。

生成的HTML报告包含一个结果表格,如下所示。

OptimizePI和 PowerTree

本节重点介绍与AC仿真和OptimizePI集成相关的PowerTree改进。有关PowerTree QIR2的更多新功能,请参阅PowerTree部分。

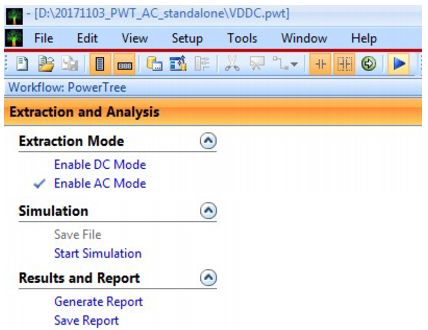

独立PowerTree实用程序中的AC仿真支持

此版本中,独立PowerTree应用程序实现了具有独立DC和AC模式的Sigrity风格的工作流程。AC模式具有直接从PowerTree应用程序中运行PowerTree原理图的AC仿真的功能。OptimizePI AC仿真通过TCL命令在后台运行。

注意:需要OptimizePI或Allegro PI选项的license才能在PowerTree应用程序中运行AC原理图仿真。

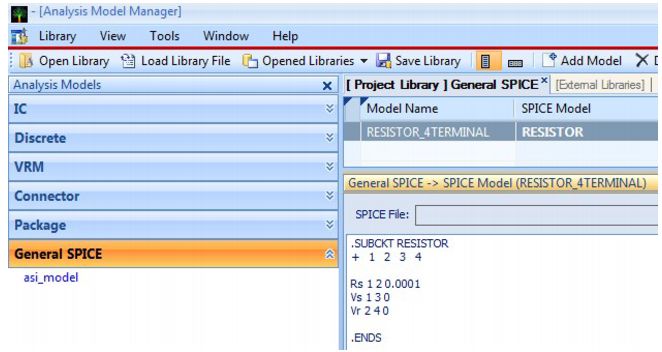

PowerTree中支持电阻和电感的AMM通用Spice模型

多终端AMM通用SPICE R和L模型现在可以在PowerTree中应用。

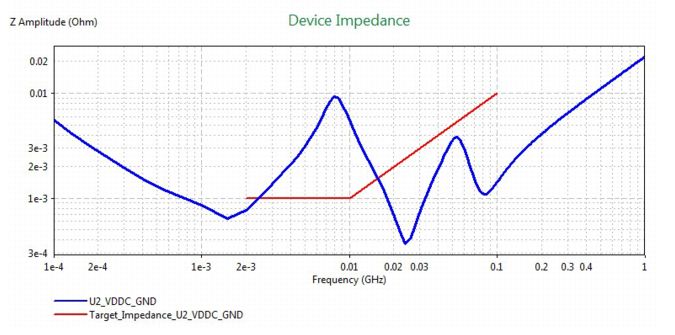

PowerTree AC原理图仿真中的目标阻抗支持

此版本新增功能可显示AC原理图仿真结果中覆盖的目标阻抗约束。这个功能对于电路设计人员来说是非常有用的,可用来确定是否需要额外的和/或不同的电容。

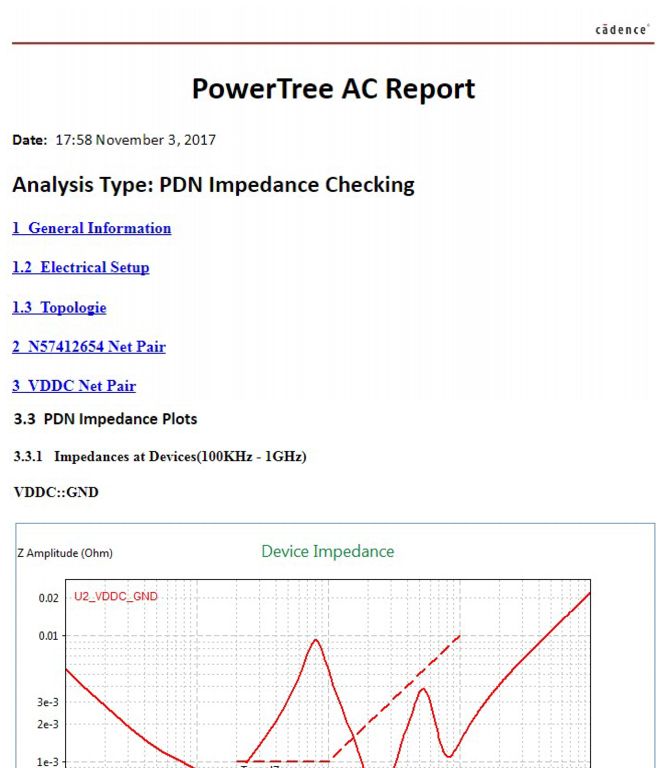

PowerTree AC原理图仿真结果的HTML报告

该版本增加了生成AC原理图仿真结果的HTML报告的功能。通过单击工作流程中的步骤创建报告。

下图为一个实际报告的摘录。

-

Cadence

+关注

关注

65文章

924浏览量

142239 -

去耦电容

+关注

关注

11文章

316浏览量

22408

原文标题:Cadence Sigrity QIR2 更新 | OptimizePI

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文读懂Cadence® Sigrity™产品QIR2 新增功能

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析

Cadence OrCAD 系列V16.0 新增功能

2015 Cadence OrCAD, Allegro以及Sigrity新技术研讨会-Invatation

Hanlp1.7版本的新增功能一览

Cadence发布创新Sigrity 2017快速实现PCB电源完整性签核

Cadence发布Cadence Sigrity 2018版本,可帮助设计团队进一步缩短PCB设计周期

电源完整性之Cadence Sigrity Power DC_IR_Drop仿真

2022 Sigrity Aurora SPB 17.4 版本更新 I 对未布线网络的拓扑提取及建模

2022 Sigrity Aurora SPB 17.4 版本更新 I 支持 Clarity 和 PowerSI 引擎直接集成

2022 Sigrity Aurora SPB 17.4 版本更新 I IR Drop 直流电压降仿真支持自动剪切功能

2022 Sigrity SPB 17.4 版本更新 I SystemSI 支持 MIPI-C 仿真与合规检查分析

2022 Sigrity SPB 17.4 版本更新 I SystemSI 为GDDR6接口增加基于JEDEC自动化分析功能

2022 SPB 17.4 版本更新 I Sigrity SystemPI 允许自定义搭建链路进行系统级PDN和电源纹波分析

Cadence® Sigrity™ 2017 OptimizePI™ QIR2 版本中的新增功能

Cadence® Sigrity™ 2017 OptimizePI™ QIR2 版本中的新增功能

评论