埋嵌元件基板由于元器件的三维配置而使PCB或者模组小型化,缩短元件之间的连接路径,降低传输损失,它是可以实现便携式电子设备多功能化和高性能化的安装技术。鉴于此,本文主要概述了埋嵌元件PCB的元件互联技术,以及对埋嵌元件PCB的评价解析。

1 前言

埋嵌元件基板由于元器件的三维配置而使PCB或者模组小型化,缩短元件之间的连接路径,降低传输损失,它是可以实现便携式电子设备多功能化和高性能化的安装技术。多层板中埋嵌LSI或者无源元件方式的埋嵌元件基板从2003年开始采用,从2006年开始正式用作高功能便携电话或者用于表用的小型模组基板。这些基板分别采用了元件制造商和PCB制造商独自开发的特征构造和工艺。本文就参考日本电子电路工业协会(JPCA)的规格中埋嵌方式的埋嵌元件基板技术的分类,采用的元件和安装技术和评价解析等加以介绍。

2 埋嵌元件基板技术的分类

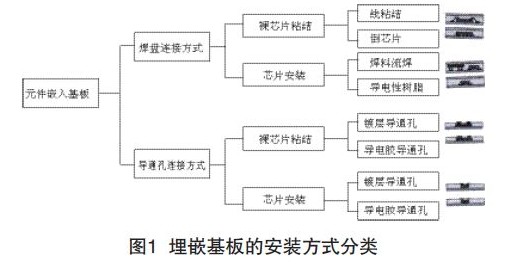

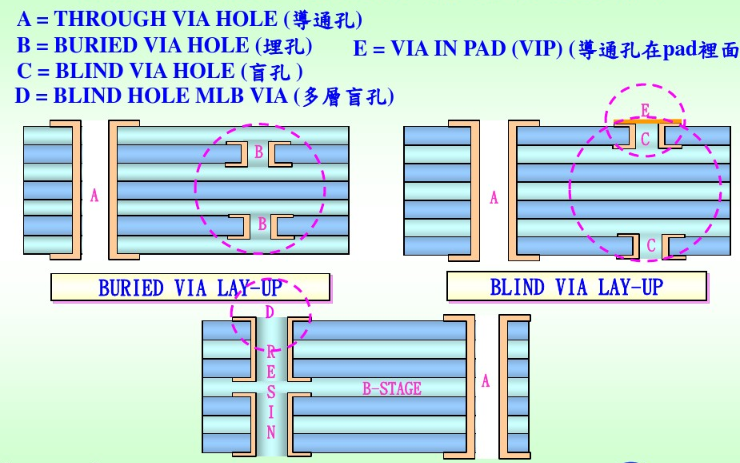

埋嵌元件基板大致分为埋嵌个别制造的元件的方式和在基板上形成直接元件的方式。本人只限于前者方式的技术。图1表示了埋嵌型的埋嵌元件基板按照嵌入元件的安装方式的分类。PCB上的元件安装方式大致有焊盘连接方式和导通孔连接方式两大类。

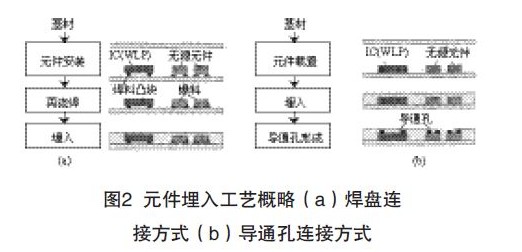

图2表示了焊盘连接方式和导通孔连接方式的代表性制造工艺。

在焊盘连接方式中,首先在基板上形成的电极上安装嵌入的元件并进行电气连接。连接完成以后采用绝缘树脂同时填充和埋没元件和电极。连接时采用现有的表面安装技术。连接材料采用焊料或者导电胶。嵌入元件的安装:元件为裸芯片时选择裸芯片粘结(Die Bonding);元件为无源元件或者模塑封装(Mould Package)或者WLP(Wafer LevelChip Scale Package)时安装选择(Mounting):裸芯片的倒芯片连接(Flip Chip Bond)采用超声波接合、C4(Controlled Collapse Chip Connection控制熔化高度芯片连接)、ESC(Epoxy Encapsulated SolderConnection环氧树脂囊包焊接)、导电性树脂和各向异性导电树脂(ACF/ACP,Auisotropic ConducliveFilm /Anisoropic Conductive Paste)和非导电性树脂(NCF/NCP,Non Conductive Film / Non CondctivePaste)等安装技术。无源元件的连接采用焊料再流焊或者导电性树脂。焊盘连接方式中由于元件连接采用传统的表面安装技术而具有有效利用现有制造设备的优点。另外,由于实施了元件安装连接以后和埋嵌以前的检查,所以可以对安装过程中发生的不良品进行筛选或者修理和返工。

导通孔连接方式中,PCB和元件进行电气连接以前采用绝缘树脂埋嵌元件。元件埋置以后,覆盖元件电极的树脂上进行激光加工,形成导通孔以后采用镀层填充导通孔,进行PCB与元件的电气连接。导通孔连接方式的特征是元件的电极上接合直接镀铜(Cu)层。由于没有介入表面安装中使用的焊料或者凸块那样的接合部,所以期待着与多层板的内部线路同等的低连接电阻和高连接可靠性,另外还可以采用全层IVH(Interstitial Via Hole)使用的导电胶进行导通孔连接,与多层板的层间连接同样的导电胶用于与元件的连接,采用同时进行埋置和连接的汇总积层工艺可以简化工程复杂的元件埋嵌基板的制造工艺。

上面介绍了按照埋嵌元件的安装技术分类的埋嵌元件基板的种类和大致的制造工艺。下面参照迄今的开发事例介绍埋嵌元件基板的制造中采用的各种安装技术。

3 焊盘连接方式的埋嵌元件基板

焊盘连接方式中在内层基板上安装元件以后,采用绝缘树脂埋置。嵌入的元件分为裸芯片(Bare Die)和其它元件,下面介绍连接用的表面安装技术。

3.1 裸芯片粘结方式

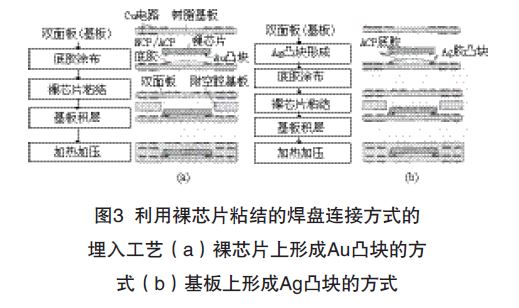

图3表示了利用倒芯片安装嵌入裸芯片的工艺。

图3(a)表示在裸芯片的电极上形成金(Au)堆积凸块。使用NCP与PCB的电极进行加热加压连接的方式。PCB的电极表面上没有进行镀金(Au)或者镀锡(Sn)等,而是原本的铜(Cu)。铜(Cu)表面上施行粗化处理,旨在提高与树脂的附着力。加热加压连接时,接合部必须维持压缩应力,对于提高连接可靠性至关重要。图3(a)中着眼于NCP的热机械特性,选择高弹性和高膨胀系数的树脂可以获得充分实用的连接可靠性。

另外还有使用ACP代替NCP的热压连接的安装方法。在裸芯片的铝(Al)电极上形成金(Au)球凸块以后,涂布底胶ACP,实施加压加热,即可电气连接。接合可靠性与NCP时同样取决于底胶树脂的物理性能。图3(b)表示了使用银(Ag)胶凸块和ACP的连接方式。PCB的电极上印刷银(Ag)胶形成银(Ag)凸块,涂布底胶ACP使用倒芯片粘结器热压接合。裸芯片的电极上没有形成铜(Cu)或者金(Au)凸块而是采用铝(Al)进行热压连接。

图3(b)的热压连接银(Ag)胶凸块的连接技术在积层板中已经量产化,它是应用了利用导电性凸块的层间连接技术(B2it,Buried Bump InterconnectionTechnology)。

图3(a)和(b)与多层板制造技术相组合的元件嵌入基板的实用化比例,利用NCP和ACP的元件连接技术,采用导电性凸块进行层间连接。制造利用导电性树脂凸块连接的双面板,在内层上安装元件以后,与外层的基板组合在一起加热加压而埋入元件,同时采用凸块使线路层间汇总连接。采用元件埋入以前进行线路形成的工艺有利于减少不良率和提高生产性。

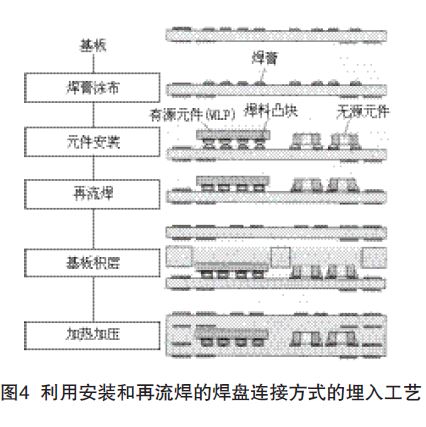

3.2 芯片安装方式

图4表示了印刷焊膏的内层的基板上采用芯片安装器(Chip Mouuter)搭载元件并采用再流焊工艺熔融焊料的连接方式。采用使LSI WLP化的芯片安装(Chip Mounting)和再流焊工艺同时的搭载和连接有源元件和无源元件。它是模型封装的LSI或者模组等大多数通用元件可以采用的嵌入技术。采用焊接连接嵌入元件时,由于基板表面上安装元件的模组基板第二次安装到母板上,经过再度再流焊工艺时担心焊料凸块(焊料球)熔融而影响到导通和绝缘特性。因此采用树脂覆盖焊料的周围,抑制再熔融产生的流动,从而可以避免上述问题。

4 导通孔连接方式的元件埋嵌基板

导通孔连接方式中,元件嵌入以后进行与基板的连接。有源元件和无源元件的全部元件的电极视为内层的线路图形,利用积层技术在元件上部形成线路层。

4.1 裸芯片粘结方式

嵌入的LSI WLP化,采用铜(Cu)线路引出WLP化的电极,扩大了电极间节距,实现了与现有PCB加工工艺亲和性高的埋入工艺。另外由于WLP化而确保良好的裸芯片(KGD,Known GoodDie)。相对与连接以后元件难以修理的导通孔连接方式来说具有很大的优越性。

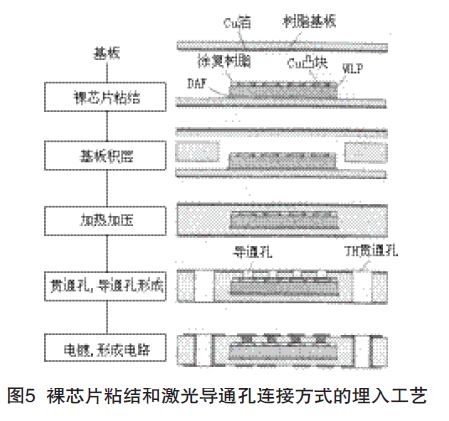

图5表示了代表性的导通孔连接方式的有源元件嵌入技术的制造工艺。嵌入的LSI WLP化,形成铜(Cu)线路和铜(Cu)凸块,施行树脂涂复。薄片化的裸芯片背面粘贴裸芯片附着膜(DAF,DieAttachment Film)以后进行位置重合,在基板上面朝上粘结。半固化片和表层基板积层,加热加压以后使裸芯片嵌入。在嵌入的WLP的电极位置上从基板表面进行激光加工,形成导通孔以后采用镀层填充导通孔,连接WLP的电极和基板的线路。由于裸芯片的表面由树脂保护,所以在嵌入加工工程中可以减少损伤或者污染等方面的危险。

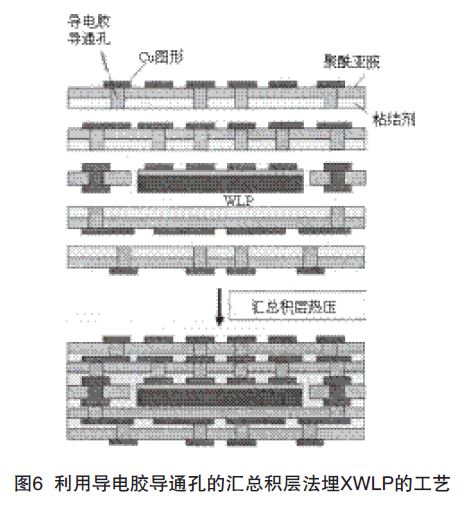

图6是导通孔的材料使用导电胶的方式。使用多层板的层间连接所用的铜(Cu),银(Ag)和烧结合金等材料,通过压接或者金属结合而连接元件。

图6表示了在聚酰亚胺多层板上嵌入经过背面研磨而薄型化的WLP例。嵌入的LSI经过WLP加工使电极的节距扩大到与PCB的导通孔同样的节距,厚度达到0.1 mm以下的薄型化。基板上形成的导通孔填充未固化的导电胶,基板/WLP和隔板(Spacer)/基板积层,一次加热加压。加热过程中依次进行导通孔中填充的导电胶固化,粘结材的流动和固化,同时完成了PCB/WLP之间的电气连接和嵌入粘结。利用导电胶导通孔的一次积层法中,由于在PCB的积层与元件的嵌入以前已经形成全层的线路,所以具有降低元件嵌入以后所发生的不良率的优越性。为了使该工艺适应将来的LSI的多针化,与裸芯片连接的导通孔节距的微细化是今后的课题。

4.2 芯片安装(Mounting)方式

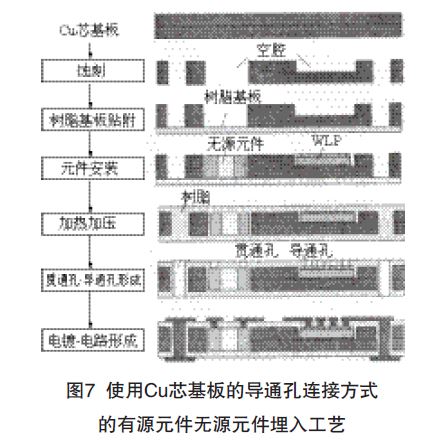

图7表示了使用激光导通孔加工和镀层连接的元件嵌入工艺。把嵌入的元件置于基板的一部分上设置的空腔(Cavity)内,然后用树脂填充而嵌入元件。使用厚铜(Cu)芯的基板,利用铜(Cu)的蚀刻形成空腔。芯板一面上贴附树脂片,堵塞空腔的一侧以后,在它的底面上固定元件。空腔的开口侧积层树脂片并进行加热,空腔内壁与元件的间隙用树脂填充使元件固定。嵌入元件的电极上的树脂形成激光导通孔开口。采用半加成法形成基板表层线路的同时采用镀铜(Cu)层填充导通孔。基板正反面的连接,空腔形成时预先在铜(Cu)芯的一部分开口,充填树脂以后采用激光形成贯通孔。采用该技术的基板具有优良的导热性,尤其是嵌入发热量多的元件时具有高散热性的特征。

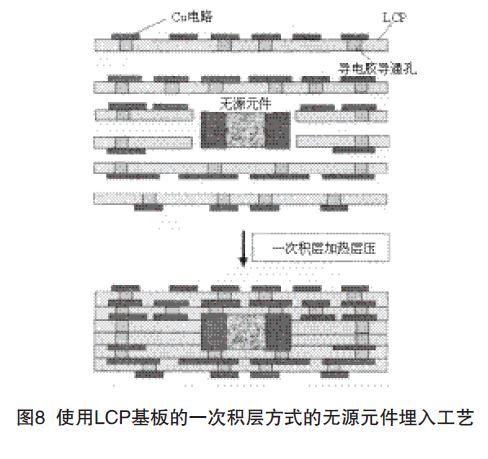

图8表示了利用一次积层法的元件嵌入工艺的概念图,作为利用导电胶的一次积层法的无源元件埋入技术,Ag-Sn系合金材料用于导通孔,LCP用作绝缘材料。配置元件处形成空腔的单面板积层规定的枚数,与此同时元件插入空腔以后进行加热加压。导通孔内填充的由Ag和Sn构成的胶材料由于加热而烧结,与此同时Sn扩散到线路板和元件的Cu电极上形成金属结合。热可塑性材料LCP(Liquid CrystalPolymer)由于加热而软化,使基板之间接合,与此同时流入到元件与空腔的间隙而嵌入元件。加热加压过程中由于树脂的流动影响到导通孔形成,元件与小型基板的间隙附近存在导通孔时,树脂流通的精确控制对于确保连接可靠性至关重要。

5 嵌入用元件

焊盘连接方式时,嵌入可以采用再流焊或者粘结剂等表面安装技术的大多数元件。为了避免板厚的极端增大而要使用元件厚度小的元件。裸芯片或者WLP情况下,它们的大多数研磨了硅(Si)的背面,包括凹块等在内的安装以后的高度为(300~150)mm以下。无源元件中采用0603型,0402型或者1005的低背型。导通孔连接方式时,上面介绍的镀层连接和导电胶连接的各种事例都是采用Cu电极的元件。用作嵌入元件时铜(Cu)电极的无源元件厚度150 mm成为目标之一,还有更薄元件的开发例。

6EPASD 评价解析T V (TestVehicle)

6.1 测试运载工具(TV)概要

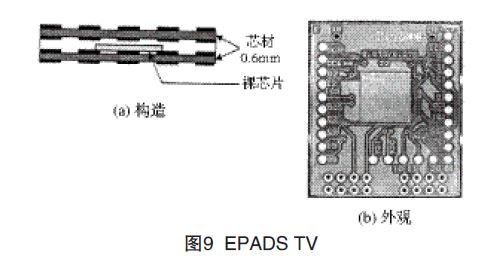

以阐明元件嵌入PCB的技术课题为目的,制作了评价解析***TV(Test Vehicle)并进行了评价。从2007年再次关于构造和设计的讨论,最终制作了如图9所示的裸芯片嵌入基板的构造。线路层为4层,L2~L3之间嵌入元件。根据元件嵌入PCB的用途,初期应该相同于HDI基板的评论,而提出元件嵌入特有的课题被视为最本质的问题,嵌入部分以外极为容易的优先制造,层间连接为贯通孔。分别使用无卤FR-4和FR-5基材进行制造。

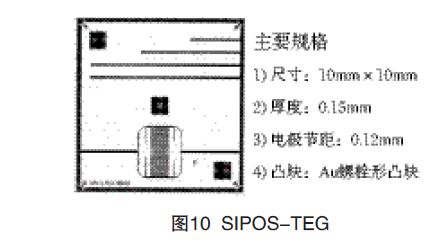

嵌入的元件是由SIPOS(System IntegrationPlatform Organization Standard)提供的“SIPOSTEG”,形成与PCB连接的菊链式图形那样的焊盘配置。图10表示了这种图形和主要规格。其中电极上形成金(Au)螺拴形凸块(Stud Bump),采用面朝下(Facedown)的倒芯片连接的安装方式。这时采用热压接合法和超声波法2种方法。因此制作成两种材料和两种安装方式的共计4种样品。

6.2 评价结果

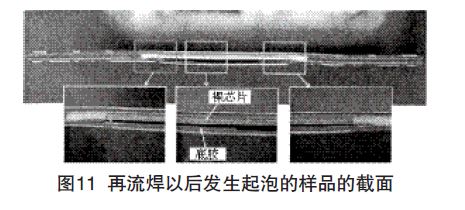

2008年实施了TV制作,2009年度进行了评价解析。首先为了评价再流焊耐热性,采用JEDEC3级的条件实施前处理。许多样品再流焊以后发生起泡。

另外还伴随着发生断线或者电阻上升。

图11表示了截面解析的一例。嵌入的芯片下方的底胶树脂与芯片之间发生剥离,部分剥离发生在螺栓形凸块与PCB电极界面。这种剥离是起泡的发生原因。耐热性的FR-5也发生若干起泡。由于四种条件中没有显着差别。所以认为发生起泡的主要原因在于构造本身。根据截面解析的结果芯片本身显着翘曲,由于嵌入以后内在的残留应力在再流焊时被释放而发生变形,或者由于芯片本身的尺寸或者PCB图形的影响等。关于翘曲方面,在内层板上安装时由于芯片与内层板的热膨胀系数差别而表现出凸状翘曲,但是如图11所示的起泡以后的截面中反而逆转为凹状翘曲而值得注意。

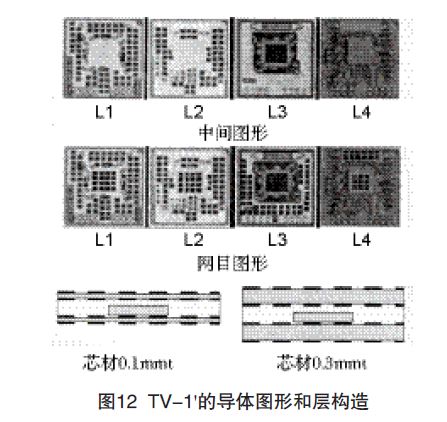

发生起泡的评价本质上是由于爆玉米花(Popcorn)现象引起的,使用不同的两种底胶树脂的安装方式都发现同样的起泡,因此认为PCB构造有很大影响。为了调查这种现象,第二次制作了TV-1′芯材厚度为0.1 mm和0.3 mm,导体图形有TV-1采用的铜(Cu)中间(Beta)图形和PCB的网且(Mesh)图形两种。共计四种样品。图12表示了TV-1′PCB的导体图形和层构造。各种构造实施了5次再流焊耐热试验,与TV-1′同样构造的芯材0.1mm/Cu中间图形再现起泡现象,而其它构造都没有发生起泡或者电阻上升,确认了构造变更的效果。

6.3 热变形解析

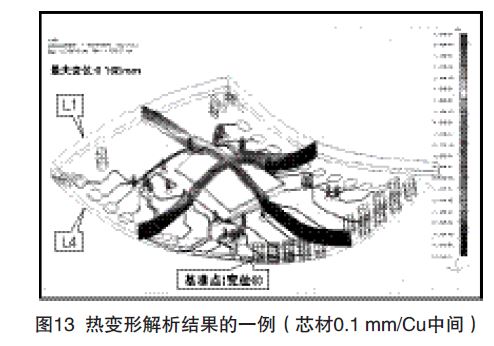

为了考察基材的厚度或者线路导体图形给予元件嵌入PCB的热变形行为的影响,利用模拟迄今获得的试验结果进行解析。根据前节叙述的EPADS TV的Geber数据制成三D模型(Model),通过解析从室温加热到260 ℃时的热变形行为而求得。解析时使用ADINA8.6(美国ADINA公司制造)进行非线性的弹性解析。解析以TV-1′为标准。基材厚度为0.1 mm和0.3 mm两种,PCB的导体设定为铜(Cu)中间图形和网目图形两种,实施共计组合成四种的解析。制成的模型如下。

(a)模型1 芯材0.1 mm厚/网目图形。

(b)模型2 芯材0.1 mm厚/中间图形。

(c)模型3 芯材0.3 mm厚/网目图形。

(d)模型4 芯材0.3 mm厚/中间图形。

另外嵌入的芯片为0.1 mm,厚度10 mm□,与TV同样的周边配置金(Au)凸块和下面填充底胶树脂的构造。实际的制造状况有所不同,在解析中室温下的应力和变形设定为0,求出加热到260 ℃时的热变行为。图13表示了热变形解析结果的一例。途中的PCB L1表示上面的,裸芯片嵌入部分的中心部表现出凸形状变形的倾向。它的周围收到裸芯部嵌入部变形的影响。变形行为随着部位而有所不同,这是由于导体图形的形状和疏密的影响所致。解析的四种模型中。模型2相当于TV-1发生起泡的构造。

解析所获得的热变形量以模型2为最大,表现出与实际基板同样的倾向。模型2的变形量为108 mm,其它模型的变形量范围为46 mm ~ 60 mm.

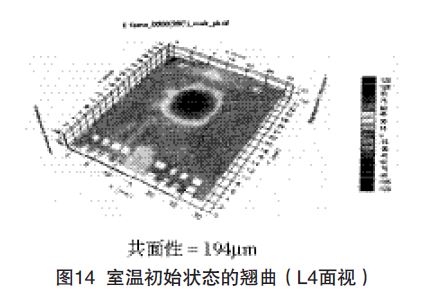

6.4 与热变形实测的比较

为了验证热变形解析的准确性,进行了热变形行为的实测。样品制造成TV-1′,构造相当热变形解析的模型1~模型4供给试验。根据莫瑞光影法(Shadow Moire)的非接触翘曲测量一边加热到最高260 ℃一边进行测量。图14表示了室温初始状态下翘曲分布图。与解析结果相反,由于L4侧具有凸状翘曲,所以在上面配置PCB L4.由于这种翘曲方向对应于图11中表示的起泡以后芯片翘曲方向,所以芯片在嵌入时和安装时表现出不同的翘曲。

从室温初始状态到260 ℃一边升温一边进行数点的测量,确认了室温初始状态时翘曲小的倾向,即L1侧表现出翘曲行为,这一点与模拟的倾向一致。以室温初始状态的翘曲量为基准求出L1测变位量,表1表示了它与模拟结果的比较结果。厚度0.1 mm的构造中实测结果大大超出模拟结果的变形量。特别是模型2中呈现出很大剥离,虽然外观没有确认,但是也有可能发生微细的层间剥离。然而厚度0.3 mm的构造中,实测结果与模拟结果比较一致,表明元件嵌入PCB的热变形预测是有效的。0.1 mm厚度的构造中两者的剥离点今后还有研究的余地,可以采用弹性解析预测热变形行为,在工业上比较有用,期待着有助于元件嵌。

7 标准化WG中无源元件嵌入的课题

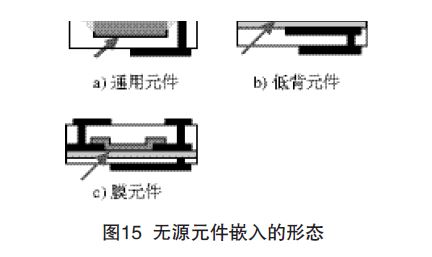

图15表示了无源元件嵌入构造的三种代表性形态。这种形态已经有10年左右的实用化,其优点是可以使用特性保证的元件,可以使用现有设备进行制造。

另一方面,对PCB的市场要求是“更薄”。特别是模组元件中“低背化”是重要的关键词。因此第一要求嵌入元件特别是无源元件芯片的低背化。由于元件制造商的开发努力,已经实现0.15 mm厚度(1005尺寸,0603尺寸)的薄型化。另外PCB本身也要求成品板厚的薄型化,但是由于为了实现高集成度的线路,不得不增加厚度,因此希望使用更薄的内层芯板,部分嵌入铜(Cu)箔的0.05 mm左右的内层芯板也已经实用化。在表面安装时的再流焊工程或者基板制造工程中存在处理困难的担心。根据这种状况,近年来采用图15(b)所示的导通孔连接方式。这种方法是在内层上安装的元件电极上进行直接线路板的导通孔连接的方式(有源元件情况下面朝上)。采用这种方式,元件安装只有安装(Mount)工程,与再流焊方式比较,简化嵌入工艺的同时降低了成本,然而为了实现这种方式正在提出若干技术课题。EPADS研究会的标准化WG中正在进行讨论。

第一是确保导通孔与元件外部电极的位置精度,它的影响因素如下。

(1)外部电极尺寸。目前的0603尺寸通用品中外部电极幅度为0.10 mm ~ 0.15 mm左右。一般PCB中激光导通孔内层焊盘径为φ0.20 mm左右。这样导通孔的一部分有可能偏离电极。

(2)元件安装精度。现在的安装机中一般安装精度为±0.05 mm程度。考虑到元件尺寸,咋一看数值较大,但是在表面安装中利用焊料的自动调准(Selfalignment)效果可以确保再流焊以后的元件位置精度。但是安装采用导通孔连接方式的元件时使用树脂系粘结剂,这时不能期望有自动调准效果。

(3)激光导通孔的调准(Alignment)。一般的激光导通孔加工时,以事前形成的线路层的对准标记(Alinment Mark)为基准进行加工。内层与元件的位置精度不能保证时,就会引起元件与导通孔的位置偏离。

第二是元件端子电极的镀层。通用元件的电极最外层一般是镀锡(Sn)层。由于激光导通孔进行镀铜(Cu)层连接,因此元件电极也希望是镀铜层。这时要经过PCB的去沾污和化学镀铜工程,因此必须形成经得起这些工程的保护膜。

第三是元件高度的波动度。元件高度的波动度即成为导通孔深度的波动度。希望从激光加工和镀层两方面进行导通孔深度的统一。

导通孔连接方式中,这些因素还会相互影响和重叠,希望以PCB制造商,元件制造商和安装机制造商为主的关系者作为开发的共同目标。

如图15(C)所示,PCB内层上制造进入元件的构造于1990年代后期进行研究开发,现在已有许多开发例,还没有适用的实用品事例。然而它对于PCB的薄板化极为有利,期待着它的实现。为此实现稳定的元件特性是第一的,希望同时进行材料研究和工艺技术的确认。

8 结语

进入21世纪以来,将会迎来元件嵌入PCB正式实用化的时期,今后将会迅速发展,为此嵌入元件的规格化或者评价方法等的标准必须紧紧跟上。新的嵌入技术的开发将会层出不穷,数年以后元件嵌入基板将会克服各种课题,成为通用的安装技术而固定下来。

关于元件嵌入PCB的可靠性评价本文只是介绍了制造上的技术课题,此外还有CAD设计上的相应课题或者包括元件检查在内的最终检查技术,PCB制造商与用户之间的品质保证契约上的课题等。

-

pcb

+关注

关注

4420文章

24022浏览量

426966 -

元器件

+关注

关注

113文章

5064浏览量

100624 -

焊盘

+关注

关注

6文章

606浏览量

39924

原文标题:埋嵌元件PCB的技术:二

文章出处:【微信号:pcb3com,微信公众号:小哥Allegro】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

全印制电子技术在pcb中的应用

埋嵌元件PCB的技术(第三部分)

埋容PCB的概念与设计

埋嵌铜块印制电路板的设计和关键工序的制造方法

全印制电子技术给PCB工业带来了怎样的积极影响

PCB元件如何创建?

埋嵌元件PCB的元件互联技术概述及对埋嵌元件PCB的评价解析

埋嵌元件PCB的元件互联技术概述及对埋嵌元件PCB的评价解析

评论