虽然芯片制造商希望能够尽快在7nm和5nm工艺中普及极紫外线光刻技术,也就是我们通常所说的EUV,但是,现实往往是残酷的!在芯片厂商坚持不懈的努力当中,他们悲哀的发现,EUV在应用当中,依然存在着这样或那样的问题,阻碍着这一技术用于实际的生产,这也是目前EUV工艺再三推迟的原因之一。

其中越来越让人担忧的一个问题就是,如何发现EUV过程中产生的缺陷。基于随机效应的原理,不难发现,EUV过程中产生的缺陷也是随机变化的,而不是可以用数据计算得到的。

这些难以避免的随机因素,在生产过程中就会导致难以预计的随机缺陷,譬如,图案粗糙度缺陷或者是芯片接触孔故障。

不过,这并不是EUV在生产过程中遇到的唯一问题!为了继续改进这一工艺,厂商们还在继续开发相关的光源和EUV掩模,涉及到随机缺陷的部分将会越来越多。而正如之前所说,EUV过程中存在的随机缺陷,对于整个工艺来说,所导致的后果往往是灾难性的,常常会导致芯片故障。所以,芯片制造商必须要发现和预防EUV生产过程中存在的这些随机缺陷,才能够确保EUV技术真正的在7nm和5nm工艺中普及。

问题在于行业内只知道随机缺陷问题出现在哪里,而对于为什么会发生却没能完全掌握,这也导致了,厂商难以预测缺陷会导致何种结果。此外,行业内的很多厂商并不具备这方面的技术来定位和测量EUV过程中随机产生的缺陷。

即便我们看到,现在在整个行业中已经有多种多样的计量和检测工具来定位和测量芯片中存在的缺陷。但是对于EUV过程中随机产生的缺陷,目前的方法常常都是无效的。

因此,对于整个行业来说,要么开发相应的解决方案解决这一问题,要么就只能一再延后EUV技术的应用。

幸运的是,一些新的技术和颇具前景的计量检测解决方案已经在实验室和Fab中出现。在实验室中,厂商正在用由巨型同步加速器存储环供电的X射线技术来获得新的认识。在Fab中,工具供应商正在开发新的电子束计量系统和软件技术。

定位问题

此前,由于芯片的工艺制程的提升越来越困难,格芯半导体,英特尔,三星和台积电都希望能够在7nm和5nm工艺中用到EUV光刻技术,来提升芯片的关键性能。

与此同时,ASML也正式发售了其首个量产型EUV光刻机。这一设备能够通过电源将等离子辐射转换成波长13.5nm的光子,然后将光线从多层反射镜中反射出去后,光线在照射到掩模板的同时不断向晶圆移动。

图一:精确的反射光 来源:ASML/Carl Zeiss SMT Gmbh

接着,光子撞击到光刻胶并产生化学反应。光刻胶作为一种光敏聚合物能够在化学反应的作用下使器件形成预设中的图案。

这一原理在今天的248nm和193nm波长的光刻技术中被广泛使用,虽然芯片厂商采用的是化学放大光刻胶(CARs),但是原理大致如此。在光刻过程中,光子撞击光刻胶产生酸,然后在曝光后烘烤的过程中,在进行酸催化反应。虽然原理大致相同,但是对于EUV来说,反应是完全不同的。

因为,EUV单光子所包含的能量(92eV)是193nm波长单光子所包含能量(6.4eV)的14倍以上。所以,在相同的曝光量下,EUV光子的数量减少了14倍。

在EUV工艺中,光子首先被光刻胶吸收,产生电子。然后这些电子产生次级电子,次级电子击中光酸产生剂,产生光酸。然后将光刻胶经过烘烤后,之前产生的光酸将会通过材料进行扩散。

而以上所说的化学反应就是随机缺陷产生的源头,然而最大的困难就是这些反应中存在这许多未知因素的干扰。“由于这一复杂的物理化学反应过程存在着一些未知因素,因此整个行业对它还缺乏相对完整的理解。”IMEC的董事Gregory McIntyre表示。

按照IMEC解释来看,在这一过程中至少存在着一对未知因素。

首先,在反应过程中被光刻胶吸收的光子数量的变化。

其次,光子能够产生多少电子,多少电子能够转化为次级电子,以及其中涉及到的能级的变化。

因此,当EUV照射光刻胶时,每一次都可能产生不同的结果,最要命的就是,这些结果几乎都是随机的。

在EUV过程中,当光子多次连续不断的击中光刻胶的时候,每一次产生的结果也可能不同。从其中一种结果向下一种结果演变的现象,我们称之为光量子散射噪声。

无论是随机性还是量子散射噪声都是关键问题,“整个行业在7nm工艺的生产过程中,还能够勉强使用EUV技术。但是,业界普遍认为,随着工艺的提升,量子噪声问题将会成为下一个EUV不得不克服的问题。”D2S的首席执行官Aki Fujimura表示。

在每一个工艺节点中,由随机效应产生的实际缺陷随时都会产生并且一直存在着。“但是由于芯片的尺寸在缩小,相对而言这些缺陷所造成的影响就会急剧增加,尤其是当工艺从7nm缩小到5nm的时候,问题更加严重。”Fractilia的首席技术官 Chris Mack认为。

此外,还存着在其他一些问题。

“在成像过程中,需要衬底和光刻胶之间能够很好的匹配。”Brewer Science的首席技术官James Lamb表示,“我们所要面临的挑战除了如何让芯片变得更薄之外,就是如何消除存在的随机缺陷,、LER 和 LWR图形边缘粗糙度。”

一个异常复杂的问题,“我们的目标是减少随机缺陷的数量和可能产生的影响,这往往需要付出更多的时间来发现和解决缺陷,”Lamb说。

发现缺陷是一项艰巨的任务,但是绝不仅仅是唯一需要克服的挑战。“当今我们要克服的不仅仅是缺陷的数量,还有在正确的节点发现真正需要克服的缺陷。”Lam Research的总经理Richard Wise认为,“问题在于,很多时候在工艺过程中,随机缺陷是很难被发现的,因为光刻胶与其内部物质的界限并不是很明显。而且,当光刻胶曝光不足的时候,就无法产生足够的光子,这时候产生的缺陷非常小,需要花费非常多的精力去寻找。”

哪一个缺陷才是必须要克服的。“通常需要一天的时间才能够找到一个缺陷。”Wise强调,在一般情况下,任何一个被忽视的缺陷都可能让产品报废。

实验室中的挑战

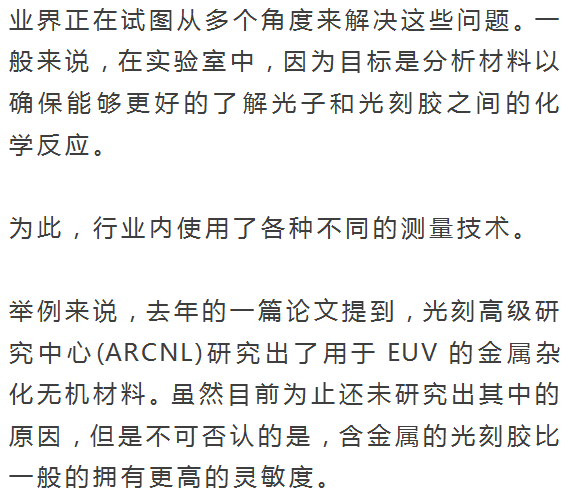

图2:EUV光刻胶中锡氧笼化合物的分子结构 来源:ARCNL

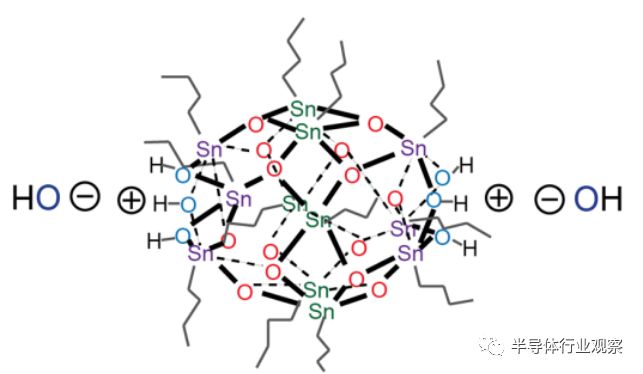

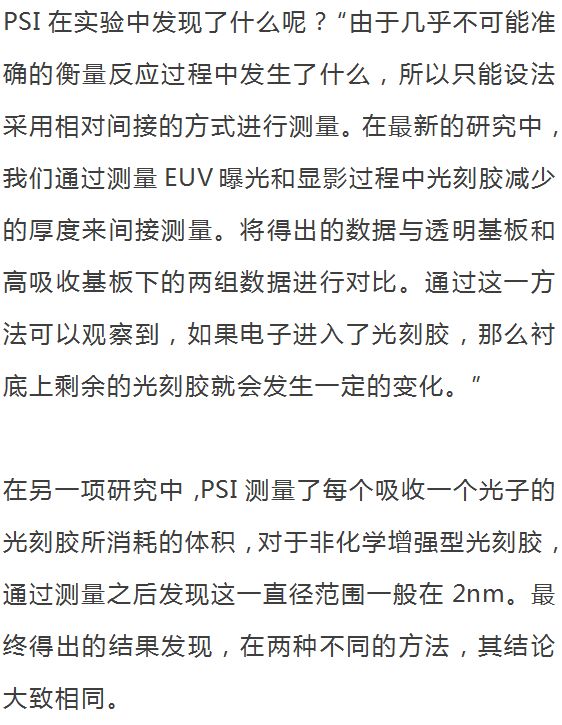

为了更加深入的了解这些分子结构,ARCNL用HAXPES(X射线光电子能谱技术)来测量和探测材料中的电子特性。

图3:HAXPES光谱仪 来源:HZB

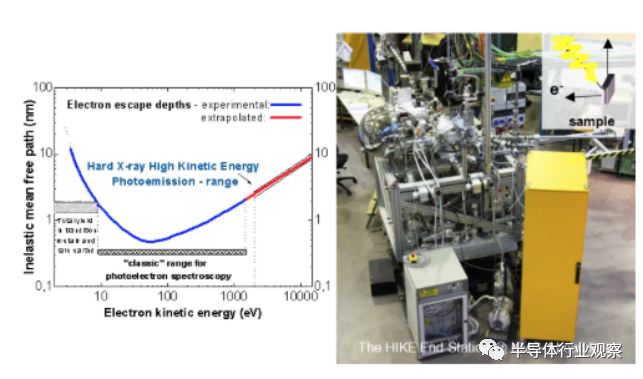

在这种情况下,HAXPES光谱仪是由来自HZB的同步辐射光源供电,同步辐射光源是一个巨大的圆环,能够产生X射线光谱辐射。

图4:电子储存环BESSY II 来源:HZB

Fab中的挑战

除了实验室中,在Fab中也存在着诸多的挑战。由于生产模式的不同,在EUV工艺过程中,往往会随机产生一些边缘粗糙的图案。事实上,图案边缘有时候是粗糙的,我们称之为线边缘粗糙度(LER),一般反映的是图案边缘上的变化。

图5:线边缘粗糙度(LER) 来源:Lithoguru, Fractilia

线边缘粗糙度也会产生非常严重的问题。

首先,它会影响晶体管的性能。

其次,线边缘粗糙度不会随着特征尺寸的缩小而缩小。根据Fractilia的说法尤其是在10nm以下,这些粗糙度将会对芯片本身的性能产生很大影响。

如何衡量这一粗糙度呢?有时候会使用扫描电子显微镜(CD-SEM)来进行量测。CD-SEM机台将电子束发射到样品当中,与样品中的电子相互作用,再将信号反馈回系统,从而实现自上而下,测量宽度与高度。

通过测量线边缘粗糙度,能够检测图案边缘处可能存在的问题。目前,根据国际半导体技术发展路线图ITRS的定义,线边缘粗糙度的度量范围为量测2μm长的图形的线宽的3σ 变异量。

Fractilia的Mack表示,”在10nm范围以下,半导体工程师需要更加清晰地认识图像粗糙对工艺和器件性能的影响,“问题在于,目前并没有更好的工具和技术来达成这一目的。

此外,CD-SEM在使用过程中的信噪比也会成为一个重要的问题,其产生的误差,与实际值之间总会存在一定的差值。

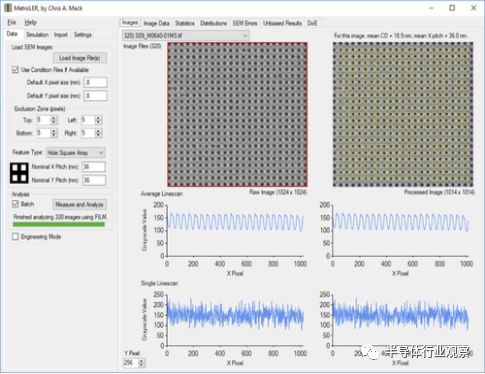

为了解决这一问题,Fractilia最近推出了一款用于测量LER的软件工具,并可与不同供应商的CD-SEM机台一起工作,这一软件能够帮助减少测量过程中产生的误差,并预测粗糙度可能带来的影响。

通常情况下,CD-SEM扫描产生的图像样本可以用ALM线性扫描量测模型进行处理。“而Fractilia提供的软件虽然不能直接使用ALM,但是却可以替代ALM检测SEM图像中的所有特征图案的边缘。这是该软件能做到的第一步。除此之外,该软件还可以检测并计算边缘的功率谱密度PSD,毕竟最难的部分就是从SEM图像中检测到边缘。”Mack强调。

图6:Fractilia技术测量的图像粗糙度

计算功率谱密度(PSD)非常关键。“PSD是一种统计粗糙边缘的数学方法。”Mack解释道,“PSD给出的不仅仅是简单的数据,完整的分析中还包含低频率下的粗糙度,以及高频下的粗糙度有多大。所以,我们能把PSD看做是超多信息的集合,远超我们所需要的数据。”

换句话来说,之前所说的3σ的数据并不足以支撑整个线边缘粗糙度(LER),实际工作中需要更多的数据。

“线边缘粗糙度的表征也不应当只局限在平均的偏差数计算上。”东京电子美国技术研发中心的蚀刻工艺开发经理Angélique Raley表示。

“想要了解从光刻到刻蚀底层的粗糙度传播,更深入地理解不同频域的线宽粗糙度是不可或缺的。”Raley认为,了解低,中,高频域是否造成整个过程的粗糙度变化是识别和解决这一变化的根本的途径和关键。

错误的接触

现在,Fractilia和其他一些组织正在着手解决下一个挑战——接触孔故障。

现在比较先进的逻辑芯片都包含了数十亿个或者更多的微型接触点,如果在EUV的过程中存在任何一点故障,都可能诱发随机缺陷,最可怕的就是,任何一个错误的接触,都有可能使整个芯片失效。

一个错误的接触孔可能包括一个并不需要的微连接micro bridge或者是两个接触孔完全合并到一起,通常我们称之为“缺失或者错误的接触孔”。

“在45nm的工艺下,你可能知道芯片缺陷是由特定位置的设计造成的。对于EUV工艺而言,更大的挑战在于,这些缺陷更加随机。”KLA-Tencor全球客户高级主管Neeraj Khanna认为,“在EUV工艺中,需要更多的过程控制,才能够控制成品率。虽然,通过调试,工程师能够找到尽可能多的缺陷。然而,我们真正要做的是找到缺陷的根源,而不是单纯找到缺陷。相对于16nm/14nm工艺而言,7nm工艺需要更小的工艺窗口。”

当然,挑战还不仅限于此。

“除了错误的接触孔。我们还需要看一下是否可以用EUV工艺来制作SAQP工艺的分割层。当然,只要解决了各方面的问题,原本需要用到多次不同掩膜版曝光才能完成的分割层,现在通过EUV一次掩膜版曝光就可以实现。”应用材料计量与过程控制部主任Ofer Adan认为,“我们不仅需要检查分割图形的CD,还需要检查布局。这就是所谓的边缘放置误差。”

以上所说的一切给Fab厂带来了不少麻烦。

理论上,芯片制造商必须对晶圆上的每一块芯片进行取样研究,寻找造成随机缺陷的接触孔。

但是这种工作往往是令人望而生畏的,因为数量过于庞大,因此,这就要求行业内必须推出一种测量工具,进行更加快捷的测量以针对即使不是上亿次也是数百万次的检测需求。

为此,应用材料和ASML正在开发一种新的电子束检验机台,或者所谓的大规模的CD量测机台。这一机台准确来说就是一个增强的电子束检测系统,类似CD-SEM和OVL套刻精度测量机台。

CD-SEM测量通常只能局限在比较小的范围内,这就使得电子束检测的时候需要降低灵敏度才能够发现芯片中的最小缺陷,所以检测速度并不快。

两全其美的方法则是电子束检验技术,设备制造商采用电子束检测系统,并在CD-SEM中加入图像测量算法,就使得机器能够在全局范围内进行测量。

“电子束量测机台测量的越快,在短时间内在每个晶圆上的测量值就越多。”GlobalFoundries的先进工艺模组副总监兼高级经理Alok Vaid强调,“虽然这仍然属于电子束的范畴,但是却可以获得更大的视野,也就意味着能够看到的更多。当视野的分辨率和成像技术足够成熟,就能够获得更多的信息来加速测量。”

不过,至少现在这一工具也存在着一些局限性。它只能够提供一部分测量数据,而不是全部的测量数据,该工具能够同时处理数以百万计的测量,所以,行业内还是需要更加先进的工具。

说在最后的话

-

芯片

+关注

关注

459文章

51600浏览量

429918 -

半导体

+关注

关注

335文章

28032浏览量

225594 -

EUV

+关注

关注

8文章

609浏览量

86394

原文标题:EUV真的准备好了么?

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DLPDLCR4710EVM-G2测试过程中发现三个问题,求解决

SMT生产过程中的常见缺陷

SMT组装过程中缺陷类型及处理

初始化AIC3104的过程中会产生杂音怎么解决?

TPA3110D2正常工作过程中产生的POP音,是不是输入阻抗匹配的问题,输入阻抗应该怎么改呢?

使用PCM1804时,发现ADC在转换过程中产生3次谐波较大,为什么?

调试THS3001过程中,发现当频率从5M开始随频率的增大信号增益增大,产生这种现象的原因是什么?

五大方法完美杜绝smt贴片加工过程中产生气泡现象

使用AFE03作为接收机的过程中,是什么原因造成噪声的产生?

什么情况下导体在磁场中产生电流

定华雷达知识讲堂:雷达物位计在测量过程中的干扰有哪些?

焊接质量缺陷产生的主要原因

如何发现EUV过程中产生的缺陷

如何发现EUV过程中产生的缺陷

评论