在计算和网络应用中采用PCI Express® (PCIe) 接口非常普遍,这些应用包括中央处理器(CPU)、图形处理器(GPU)、网络接口卡(NIC)、交换机、服务器以及诸如固态设备(SSD)之类更 新型的存储系统,等等。然而,当今的网络和快速兴起的人工智能(AI)应用均要求在加速器 和GPU中采用更大的带宽以及更快的互连,以便发送和接收更大量的数据。

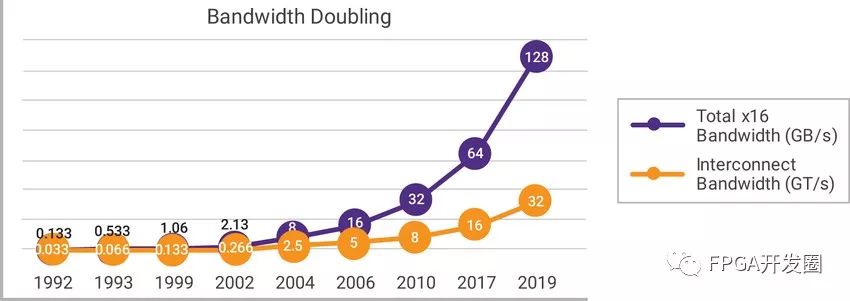

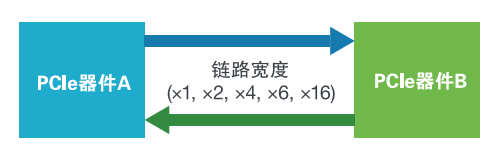

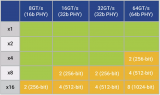

鉴于PCIe在此类应用中的广泛使用以及越来越大的带宽需求,PCI-SIG产业联盟最近宣布了最新规范PCIe 5.0,它把数据速率提高到32GT/s,并使链路带宽增加一倍,从64GB/s 提高到128GB/s。 图1显示了PCIe 互连和总带宽的演变。

图1:PCI-SIG带宽增长

PCIe 5.0规范主要处理速度提升以及相关物理层(PHY层)的修改。然而,转向32GT/s设计时,将会带 来 系统设计人员及PHY设计人员都必须考虑的几项挑战。本文描述了转向32GT/s速度的PCIe设计所面临的挑战,以及设计人员如何能够利用新的PCIe 5.0接口成功设计出系统。

系统设计师面临的挑战

印刷电路板(PCB)的走线、连接器、电缆乃至IC封装都是系统级的带宽限制因素,它们使 得高 数据 速率 的设计变得具有挑战性。高信号频率增加了铜损和功率损耗,这会导致传输距离减小。另外,更高 信号 频 率中存在的通道损失会导致信号完整性(SI)问题。

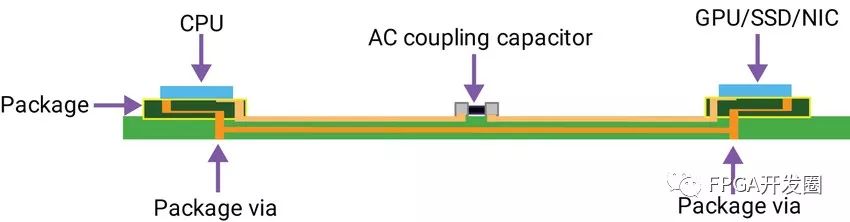

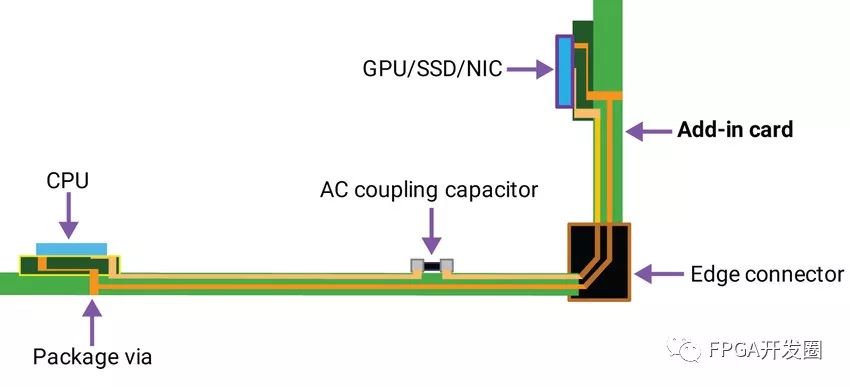

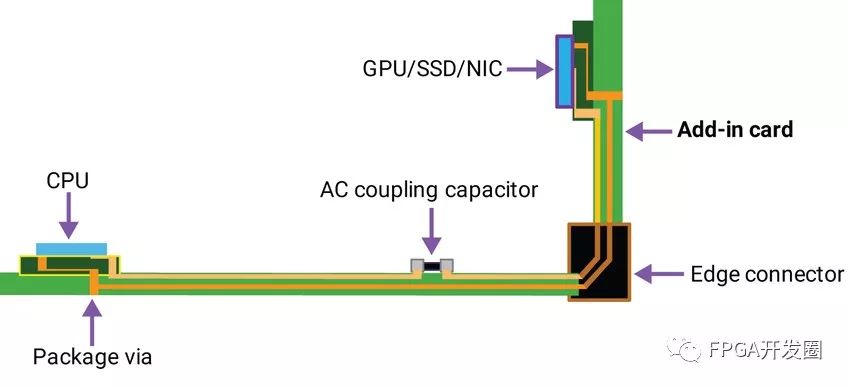

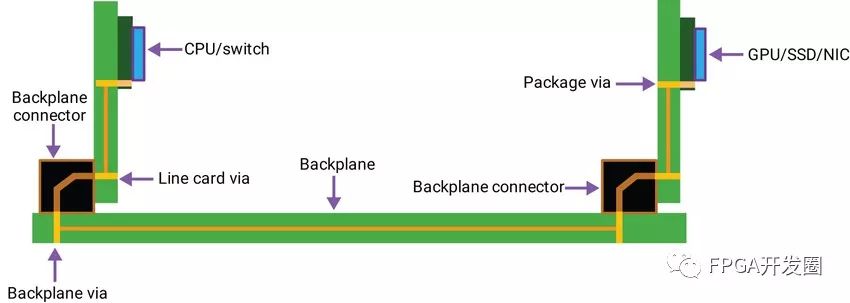

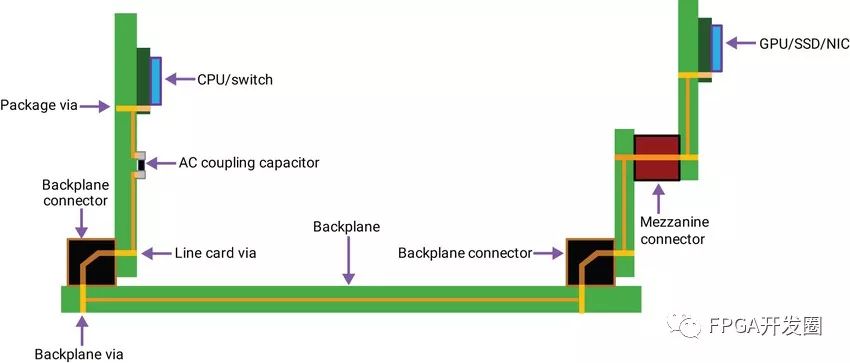

为了满足各种应用的需求,PCIe通道的种类有很多,既有不包含连接器的“芯片到芯片”拓扑结构,也 有 包 含背板接口的复杂服务器拓扑结构,而且这样的背板 接口还包括多个 PCB卡和两个 或多个连 接器。 如图2至图5所示,大多数PCIe通道在每一端都由一个IC封装组成,而且带有多个PCB,其中包括: 处 理 器 板、附加卡和转接卡;它们全部连接至一个或多个夹层卡或PCIe卡机电(CEM)连接器。

图2:“芯片到芯片”接口,最简单的通道,没有连接器

图3(a):带有一个夹层连接器的通道

图3(b):带有一个边缘连接器(附加卡)的通道

图4(a):带有两个连接器并使用一个转接卡和一个附加卡的通道

图4(b):带有两个线路卡和两个连接器的标准背板通道

图5:具有两个以上连接器的复杂背板通道

历史上,PCIe系统设计人员把通用低成本FR4 PCB材料和引线键合(wirebond)封装用于 高达 8GT/s 数 据 速率(Gen3)的大多数应用,这种做法已被证明是成功的。但是,在32GT/s的数 据速率下 使用 这 种材料 和封装并不可行。

由于通道损耗的增加,即使在最大速率为16GT/s的PCIe 4.0中(它对于在下一代电路板设计中保持 现有 的 通道长度是必不可少的),大多数设计人员也正在从FR4 PCB转向更低损耗的材料,如MEGTRON。 PCB在 设计上也可以在走线之间采用更宽的空间间隔,以便进一步提高系统级SI性能。同样,对于SI,许多设计将 使用增强的CEM连接器或定制的夹层连接器,并且将回钻PCB通孔,以便尽量缩短截线(stub)长度。在 某些通道很长的情况下,也可以使用重定时器。

然而,所有这些增强都是有代价的。MEGTRON材料的成本可能比标准FR4材料高出1.2倍至2.5倍,而且PCB 走线可能需要进一步加大间隔以获得更好的抖动(jitter)性能,从而导致更大、更昂贵的 PCB。如果 采用 截线(stub)回钻(电路板制造过程中的一个增量步骤),也会增加 PCB的总成本。 另一个需要考虑 的因 素是,增强的和定制的表面贴装连接器如何比标准通孔CEM连接器更为昂贵。此外,采用时脉 重驱器会 增 加物料清单(BOM)成本、数据路径延迟和系统功耗;它们也会占据PCB上额外区域,这会增加电路 板及 组装成本。

为了验证其设计,系统设计人员必须与信号完整性工程师、封装设计人员、SoC设计人员 以及电 路板 布局 设计人员密切合作,对其通道中的每个组件进行建模,并验证其整个端到端性能。

PHY设计师面临的挑战

对16GT/s PHY设计进行渐进式改进在大多数应用中并不足以满足PCIe 5.0通道 要求。 由于在 32GT/s 速 度下信道损耗显著增加,发射器(TX)和接收器(RX)中的均衡电路需要显著的改进。另外,更 严 格 的 抖动参数和抖动限制以及回波损耗规格也要求在TX和RX中重新设计许多子电路。

预计PCIe 5.0的PHY将通过控制器以及单独参考时钟独立扩展频谱计时(SRIS)来支持通道通路裕量(Lane margining)请保留英文描述等功能,同时满足在过程、电压和温度角(Corner)建议保留英文 等方 面 更 严格的时序和抖动要求。

此类增强和额外的限制使得设计PCIe 5.0 32GT/s PHY变得非常复杂,需要许多方面的能力来实现低功耗、小面积和低延迟的PHY,同时提供最佳信号和电源完整性(PI)性能。

具有精确模型、经过硅验证的PHY使得设计人员能够对端到端通道进行建模、设计和模拟,以便对 系统 设 计进行验证和优化。

小结

在诸如网络、存储和新兴人工智能等数据密集型应用中,对带宽的要求越来越高,这迫切需要更快的互连,例如在32GT/s速度下的新型PCIe 5.0技术。但是,设计人员必须了解并考虑在转向32GT/s PCIe设计时 面临 的诸多挑战。在更高的数据速率下解决信号完整性、封装和通 道性能等问 题需要在多 个领域具 备充分 能 力。这就是为什么越来越多的片上系统(SoC)设计人员采用经 过验证的第三方 IP来进行成功的 IC集成的 原因。

许多企业都在利用诸如Synopsys这样可靠且经过验证的第三方IP和电源完整性服务。借助于Synopsys以数十年PCIe专业知识为基础的面向PCIe 5.0的IP,SoC设计 人员可 以尽早启 动其32GT/s 的设计。 SoC设计 人 员可以与Synopsys合作,以讨论在更高数据速率下PCIe通道的性能需求,同时解决IP集成、时序收敛、信 号完整性、封装和制造方面的需求。我们将在随后发布的文档中详细阐述每项挑战。

-

印刷电路板

+关注

关注

4文章

877浏览量

37612 -

cpu

+关注

关注

68文章

11324浏览量

225836 -

PCIe

+关注

关注

16文章

1474浏览量

88896

原文标题:转向32GT/s PCI Express设计所面临的挑战

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

转向32GT/s速度的PCIe设计所面临的挑战

转向32GT/s速度的PCIe设计所面临的挑战

评论