台积电目前正在圣克拉拉举办第24届年度技术研讨会,它刚刚发布了一个可以为显卡带来革命性变革的技术Wafer-on-Wafer (WoW,堆叠晶圆)技术。顾名思义,WoW的工作方式是垂直堆叠层,而不是将它们水平放置在电路板上,就像3D NAND闪存在现代固态驱动器中堆叠的方式一样。这意味Nvidia和AMD GPU不需要增加其物理尺寸或缩小制造工艺即可获性能提升。

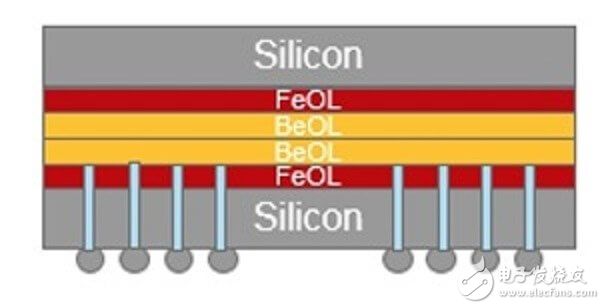

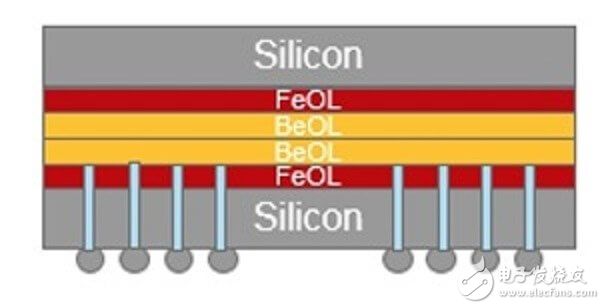

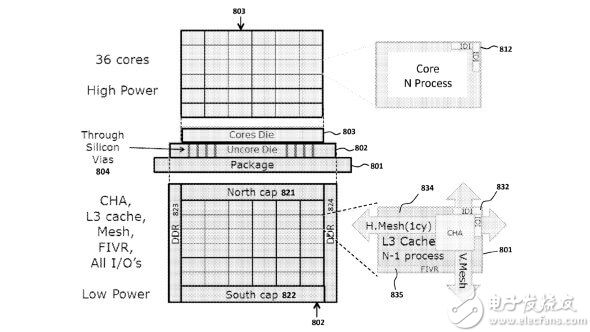

Wafer-on-Wafer (WoW,堆叠晶圆)技术通过使用形成硅通孔(TSV)连接的10微米孔彼此接触。台积电的合作伙伴Cadence解释说,Wafer-on-Wafer (WoW,堆叠晶圆)设计可以放置在中介层上,将一个连接路由到另一个连接,创建一个双晶立方体。甚至可以使用WoW方法垂直堆叠两个以上的晶圆。

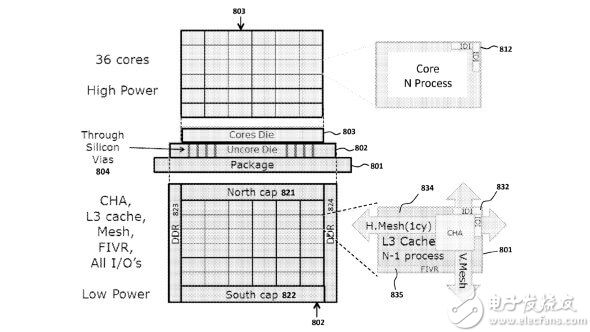

该技术将允许更多的内核被塞入一个封装中,并且意味着每个晶片可以非常快速并且以最小的延迟相互通信。尤其令人感兴趣的是,制造商可以使用WoW的方式将两个GPU放在一张卡上,并将其作为产品更新发布,从而创建基本上两个GPU,而不会将其显示为操作系统的多GPU设置。

WoW现在最大的问题是晶圆产量。当它们被粘合在一起时,如果只有一个晶圆坏了,那么即使两个晶圆都没有问题,它们也必须被丢弃。这意味着该工艺需要在具有高成品率的生产节点上使用,例如台积电的16纳米工艺,以降低成本。不过,该公司的目标是在未来的7nm和5nm制造工艺节点上使用WoW技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

尤其是先进封测技术,以期推动台积电进入下一个业务扩张的阶段。 晶

![的头像]() 发表于

发表于 07-21 00:04

•3838次阅读

进步,先进封装行业的未来非常活跃。简要回顾一下,目前有四大类先进封装。 3D = 有源硅堆叠在有源硅上——最著名的形式是利用台积电的 SoI

![的头像]() 发表于

发表于 12-21 15:33

•1029次阅读

、SPIL)和安靠(Amkor)正在扩大产能。根据DIGITIMES Research最新关注全球CoWoS封装技术和产能的报告,到2025年第四季度末,台积电的月产能预计

![的头像]() 发表于

发表于 11-01 16:57

•494次阅读

在图形处理单元(GPU)市场,AMD和NVIDIA是两大主要的竞争者,它们各自推出的产品在性能、功耗、价格等方面都有着不同的特点和优势。 一

![的头像]() 发表于

发表于 10-27 11:15

•975次阅读

在近期的一场半导体产学研交流研讨会上,三星电子晶圆代工业务部的副总裁Jeong Gi-tae展现出了高度的自信。他坚决表示,三星的技术并不逊色于台

![的头像]() 发表于

发表于 10-24 15:56

•599次阅读

近日,知名研究机构集邦科技(TrendForce)发布了最新预测报告,揭示了全球晶圆代工行业的一片繁荣景象。报告指出,台积

![的头像]() 发表于

发表于 09-24 14:52

•400次阅读

芯片堆叠在晶圆上。这一技术的推进是为了应对更强大的人工智能芯片以及AI趋势下集成更多HBM存储芯片的需求。 台

![的头像]() 发表于

发表于 09-13 00:20

•3973次阅读

晶圆代工厂商力积电近期宣布了一项重大技术突破,其Logic-DRAM多层

![的头像]() 发表于

发表于 09-06 17:33

•879次阅读

在近日于台湾举行的SEMICON Taiwan 2024国际半导体展会上,台积电展示了其在先进封装技术领域的雄心壮志。据台

![的头像]() 发表于

发表于 09-06 17:20

•746次阅读

在半导体制造领域,台积电一直是技术革新的引领者。近日,有知情人士透露,这家全球知名的芯片制造商正在积极探索

![的头像]() 发表于

发表于 06-22 14:31

•1473次阅读

1. 传台积电研发芯片封装新技术 从晶圆级转向面板级封装 知情人士称,

发表于 06-21 10:18

•944次阅读

近日,据业界知情人士透露,全球知名的半导体制造巨头台积电已成功获得英特尔即将推出的笔记本电脑处理器系列的3nm芯片订单,标志着双方合作的新里程碑。据悉,台

![的头像]() 发表于

发表于 06-20 09:26

•729次阅读

近日,SK海力士与台积电宣布达成合作,计划量产下一代HBM(高带宽内存)。在这项合作中,台积

![的头像]() 发表于

发表于 05-20 09:18

•589次阅读

展望未来,台积电正通过多个方向推动半导体行业持续发展:包括硅光子学的研发、与DRAM厂商在HBM领域的深度合作以及探索将3D堆叠

![的头像]() 发表于

发表于 04-29 15:59

•411次阅读

据悉,其中一项可能性是台积电有望引进其晶圆基片芯片(CoWoS)封装

![的头像]() 发表于

发表于 03-18 14:28

•541次阅读

台积电的堆叠晶圆技术可以将NVIDIA和AMD GPU性能提高一倍

台积电的堆叠晶圆技术可以将NVIDIA和AMD GPU性能提高一倍

评论