IP授权公司安谋(Arm)于 4 日宣布,旗下 Arm Artisan 物理 IP 将使用台积电针对 Arm 架构开发的单芯片处理器(SoC),并用于 22 纳米超低功耗(ultra-low power,ULP)与超低漏电(ultra-low leakage,ULL)的产品平台。

Arm 指出,台积电 22 纳米 ULP / ULL 制程是针对主流行动与物联网设备进行最佳化设计。不仅能提升基于 Arm 架构的 SoC 效能,与台积电前一代 28 纳米 HPC+ 制程平台相较,更可显著降低功耗及芯片面积。

Arm 物理设计事业群总经理 Gus Yeung 表示,这项次世代制程技术能在更低功耗和更小面积下加入更多功能,且结合 Artisan 物理 IP 及台积电的 22 纳米 ULP / ULL 制程平台,在设计与制造成本方面有优势。双方将为彼此的合作伙伴,提供立即显现的每毫瓦运算效能,以及节省芯片面积方面的利益。

Arm 进一步指出,采用台积电 22 纳米 ULP / ULL 制程技术的 Artisan 物理 IP,包含晶圆厂赞助提供的内存编译器,针对次世代网路终端运算设备在低漏电与低功耗的需求达到最佳化状态。这些编译器还附有超高密度与高效能物理 IP 标准元件库,其中包含功耗管理套件、厚闸极氧化层元件库等,协助优化低漏电功耗。另外,还提供泛用型 I/O 解决方案,确保达成最大程度的效能、功耗、以及面积(PPA)最佳化。

台积电设计建构行销事业处资深处长 Suk Lee 指出,Artisan 物理 IP 让台积电加速设计定案(tape-out)时程,瞄准主流物联网与行动设备,加快这些引领业界的 SoC 上市。延续台积电与 Arm 在 28 纳米 HPC+ 平台成功合作的基础,台积电与 Arm 携手大幅降低功耗与面积,为彼此共同的芯片设计伙伴提供许多机会,在更多设备呈现更完善的终端运算经验。

Arm 指出,与台积电 22 纳米 ULP / ULL 制程技术的积极整合时程下,确保满足 Arm 与台积电共同的芯片设计伙伴可在 2018 下半年完成相关设计定案。

-

ARM

+关注

关注

134文章

9097浏览量

367617 -

台积电

+关注

关注

44文章

5637浏览量

166527

发布评论请先 登录

相关推荐

台积电计划在美生产BLACKWELL芯片

苹果加速M5芯片研发,争夺AI PC市场,台积电先进制程订单激增

谷歌Tensor G系列芯片代工转向台积电

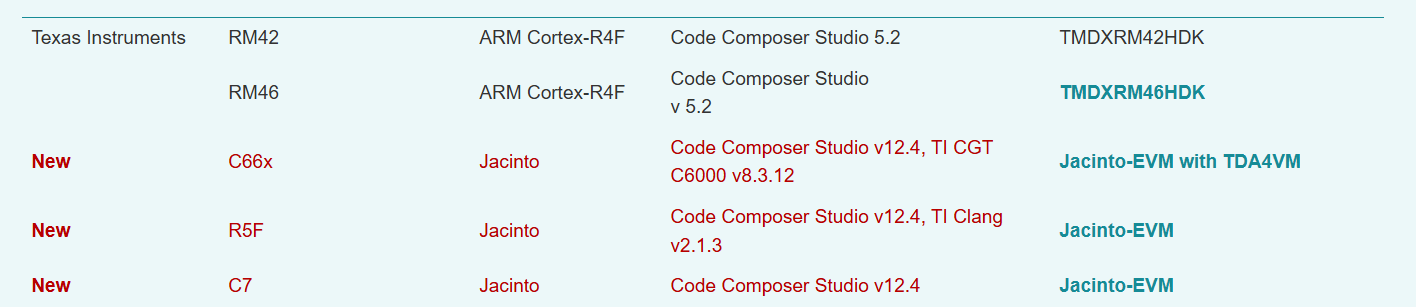

针对TI汽车处理器新的SAFERTOS库评估包

ARM处理器的寻址方式

ARM处理器和CISC处理器的区别

ARM处理器的结构和特点

ARM处理器概述和发展历程

什么是ARM处理器?与x86的比较及其优缺点

ARM将使用台积电针对其构架开发的单芯片处理器

ARM将使用台积电针对其构架开发的单芯片处理器

评论