目前主流的CPU制程已经达到了14-32纳米(英特尔第五代i7处理器以及三星Exynos 7420处理器均采用最新的14nm制造工艺),更高的在研发制程甚至已经达到了7nm或更高。但,就是这几个在常人看来稀松平常的数字背后,却暗藏着一场激烈的“标准之争”。

英特尔联合创始人戈登•摩尔在半世纪前提出的摩尔定律,是指每代制程工艺都要让芯片上的晶体管数量翻一番。纵观芯片每代创新历史,业界一直遵循这一定律,并按前一代制程工艺缩小约 0.7倍来对新制程节点命名,这种线性微缩意味着晶体管密度翻番。因此,出现了90nm、65nm、45nm、32nm—每一代制程节点都能在给定面积上,容纳比前一代多一倍的晶体管。

切入正题之前,先普及一下什么叫“制程工艺”?

按照百度百科的说法,半导体制造工艺指制造CPU或GPU的制程,或指晶体管门电路的尺寸,单位为纳米(nm)。制造工艺越先进,CPU与GPU这样的芯片内部就会集成更多的晶体管,使处理器具有更多的功能与更高的性能;更先进的制造工艺会减少处理器的散热功耗(TDP),从而解决处理器频率提升的障碍;更先进的制造工艺还可以使处理器的核心面积进一步减小,也就是说在相同面积的晶圆上可以制造出更多的CPU与GPU产品,直接降低了CPU与GPU的产品成本。

目前主流的CPU制程已经达到了14-32纳米(英特尔第五代i7处理器以及三星Exynos 7420处理器均采用最新的14nm制造工艺),更高的在研发制程甚至已经达到了7nm或更高。

但,就是这几个在常人看来稀松平常的数字背后,却暗藏着一场激烈的“标准之争”。

考不过就改分,不厚道吧?

战争总是激烈的,先讲个笑话放松一下:

一个班里,坐着I、S和T三位同学。期末考试结束了,家长会上老师说,我们班这次S同学和T同学成绩最高,值得表扬。I同学听后很委屈,回家跟家长说,我考了98.5,那是真的,那俩傻子只考了79,为了不挨打,自己偷偷把分数改成99了。

好了,开始说正经的……

在2014年英特尔推出14nm工艺之后不到一年的时间内,三星和台积电都陆续推出了自己的14nm工艺和16nm工艺,并被苹果用于制造iPhone 6s所搭载的A9处理器。2016年底,三星和台积电又相继推出了自己的10nm工艺,看起来这也比英特尔的10nm工艺早了将近十个月。

然而英特尔高级院士、技术与制造事业部制程架构与集成总监马博(Mark Bohr)却批评了竞争对手的一些做法,指出也许是因为制程进一步的微缩越来越难,一些公司背离了摩尔定律的法则。即使晶体管密度增加很少,或者根本没有增加,但他们仍继续为制程工艺节点命新名,结果导致这些新的制节点名称根本无法体现位于摩尔定律曲线的正确位置。

“行业亟需一种标准化的晶体管密度指标,以便给客户一个正确的选择。客户应能够随时比较芯片制造商不同的制程,以及各个芯片制造商的‘同代’产品。但半导体制程以及各种设计日益复杂使标准化更具挑战性。”Mark Bohr说。

他认为,“行业真正需要的是给定面积(每平方毫米)内的晶体管绝对数量。”也就是说,每个芯片制造商在提到制程节点时,都应披露用这个简单公式所测算出的MTr/mm2 (每平方毫米晶体管数量(单位:百万))单位中逻辑晶体管密度。只有这样,行业才可以厘清制程节点命名的混乱状况,从而专心致志推动摩尔定律向前发展。

英特尔公布的数据显示,英特尔10nm制程的最小栅极间距从70nm缩小至54nm,且最小金属间距从52nm缩小至36nm。这使得逻辑晶体管密度可达到每平方毫米1.008亿个晶体管,是之前英特尔14nm制程的2.7倍,大约是业界其他“10nm”制程的2倍。同时,芯片的die area缩小的幅度也超过了以往。可以看到,22nm之前每代工艺的提升可带来die area约0.62倍的缩减,14nm以及10nm则带来了0.46倍和0.43倍的缩减。

超微缩是英特尔用来描述从14nm到10nm制程,晶体管密度提高2.7倍的术语。超微缩为英特尔14nm和10nm制程提供了超乎常规的晶体管密度,并延长了制程工艺的生命周期。尽管制程节点间的开发时间超过两年,但超微缩使其完全符合摩尔定律。

纵向来看,相比之前的14nm制程,英特尔10nm制程提升了高达25%的性能和降低45%的功耗。全新增强版的10 nm制程—10++,则可将性能再提升15%或将功耗再降低。

“如果我们再横向的与业界其他竞争友商的16/14nm制程相比,就会发现英特尔14nm制程的晶体管密度是他们的1.3倍。业界其他竞争友商10nm制程的晶体管密度与英特尔14nm制程相当,却晚于英特尔14nm制程三年。”英特尔公司执行副总裁兼制造、运营与销售集团总裁Stacy Smith说。

摩尔定律到底有没有失效?

2011年下半年,英特尔发布了22nm工艺;2年半之后的2014年上半年,英特尔才发布最新的14nm工艺;3年后的2017年,英特尔才正式发布新一代10nm工艺。而且,在从14nm向10nm提升的过程中,英特尔此前一直秉承的Tick-Tock策略(一年提升工艺,一年提升架构)也很少再被提及。

“连英特尔这样最顶级的芯片制造商都花了3年左右的时间去完成两代工艺间的演进,这难道还不算失效吗?”人们不禁要问?

但如果我们细心的挖掘一下就会发现,英特尔14nm与之前的22nm的命名并不是0.7倍之间的关系。也就是说,如果按照0.7倍命名规律来看,22nm的0.7倍命名应该是16nm,而不是22nm的0.64倍的14nm工艺。

从上两张图可以看到,英特尔14nm工艺下的晶体管密度为37.5Mtr/mm²(百万晶体管/平方毫米),而这个密度是英特尔22nm工艺下晶体管密度的2.45倍。如果按照摩尔定律每两年翻一番的标准,两年半的周期,晶体管数量应该是需要增加2.5倍左右,所以英特尔的14nm工艺的晶体管密度也是基本符合摩尔定律要求的。

而且,从英特尔的32nm到22nm,每两年的时间,晶体管密度(单位面积下晶体管的平均数量)的提升都超过了两倍(32nm的晶体管密度是45nm的2.27倍)。虽然英特尔从22nm升级到14nm,以及从14nm升级到10nm的时间周期都超过了两年,但是对应的晶体管密度也分别提升了2.5倍和2.7倍。

而英特尔最新发布的10nm工艺下的晶体管密度则达到了100.8Mtr/mm²,大约是上一代的14nm工艺的2.7倍,也就是说3年左右的时间内,英特尔实现了晶体管密度2.7倍的增长,虽然略低于本该3倍的增长,但是结合此前几代超出摩尔定律的增长,英特尔10nm工艺仍然是符合摩尔定律的对于晶体管密度的线性增长要求。

超微缩的意义是什么?

在我看来,超微缩技术其实还是想尽可能维持摩尔定律,并保持芯片性能和成本而提出来的。因为制程节点越小,工艺越复杂,完全按照摩尔定律的规律是越来越困难了。die area越小,一个300mm晶圆上可放置的晶体管数量就越多,对英特尔和其他厂商来说,至少不用提前上450mm晶圆,此为其一。

其二,延长节点时间一是出于制造成本,工艺越先进,成本越高。英特尔说了,就算啥都不干,单把设备搬进fab里就需要花费70亿美元,恐怕英特尔自己也要掂量掂量;二是制造难度在大幅上升,很多技术需要进一步研究,以前那种革命式的前进就会变成渐变式的前进,这就是英特尔为什么要提出10nm+、10nm++的概念,简单说就是“小步快跑”。

其三,不是所有应用都需要如此先进的制造技术,目前也就是CPU、GPU、FPGA这类的芯片追逐新工艺以提升性能,更多应用可能28nm工艺甚至90nm工艺都足够应对了。而且,还要考虑是不是有公司能设计出5nm芯片?造出来能有多少产能?带来多大利润?在没有明确前景的时候,在相对比较成熟的工艺上“修修补补”可能更可靠。

其四,为了能够实现缩小面积,提高晶体管密度的目标,英特尔又提出很多新的技术,比如FinFET、3D堆叠、硅通孔、采用紫外光光刻等等。不过另一方面,单纯依靠堆叠晶体管数量又不行,因为还需要考虑其他因素,比如缓存、驱动电压、电流密度等,所以确实是一件很复杂的事情。

随着工艺的发展,制程节点之间的时间已经延长,成本也更加昂贵,越来越少的公司可以承担得起推进摩尔定律的成本,这是整个行业正在面临的问题。凭借规模优势、制程技术优势和集成密度优势,英特尔正在矢志不渝的推动摩尔定律在未来的继续前进。

颠覆未来计算

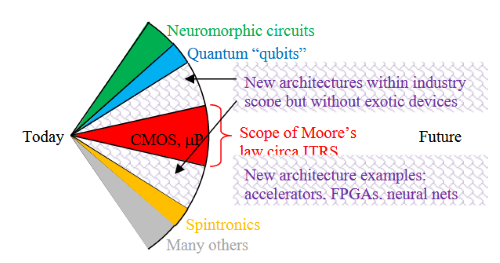

持续推动摩尔定律前行的动力不止来自于制造工艺的演进。

随着从高度动态、非结构化自然数据中进行收集、分析和决策的需求越来越高,对计算的需求也超越了经典的CPU和GPU架构。“不去研究数据的产生、数据的类别、所需要的处理能力是不行的。这和以前的通用数据处理不一样,单纯强调某一种处理器的算力是相当片面的。”英特尔公司全球副总裁兼中国区总裁杨旭认为,人工智能等于GPU是一个误解。人工智能最起码还要发展一二十年,现在没有任何一家厂商敢说应对未来人工智能的发展,所有的计算能力都准备好了,能胜任今后所有从简单到复杂的人工智能应用。

在向数据公司转型的过程中,英特尔将自身定义为端到端方案提供商,即产品线覆盖云端、网络传输端和终端。其中,核心来自云端的大规模数据处理,而布局端到端则可以让英特尔掌握“数据什么时候来、是什么样的数据、需要怎么来处理”。

为了弥补处理新数据的能力,跟上技术发展的步伐,并推动PC和服务器以外的计算,英特尔过去六年来一直在研究能够加快经典计算平台的专用架构,并且不惜重金收购。2017年3月,英特尔斥资153亿美元收购以色列自动驾驶技术供应商Mobileye,并由Mobileye主导如今的英特尔自动驾驶事业部;2016年,英特尔收购了AI初创企业Nervana Systems、视觉处理芯片企业Movidius等;2015年6月,英特尔斥资167亿美元收购可编程芯片FPGA的生产商Altera,并成立了可编程解决方案事业部。

此外,英特尔还同时加大了对人工智能(AI)和神经拟态计算的投资和研发,这被视作英特尔对未来计算的提前布局,旨在颠覆全球未来计算格局。

●量子计算

相对于传统计算,量子计算最大的优势是可以并行地运行数据,它表示数据的能力达到传统计算机的50倍,使得我们可以处理在固定内存时间内传统计算机解决不了的问题。

如何浅显易懂的理解量子计算和传统计算的区别,有一个行业公认的例子:抛一枚硬币,通常来说,它落地时或者正面朝上、或者反面朝上,只有两种答案,这就是二进制的传统计算。那么,现在你把硬币立起来旋转,它既是1,也是0,这就是量子计算。

对于英特尔这样一家数据公司,押注量子计算的目的十分明显。目前全球范围内包括无人驾驶、人工智能各个领域的数据呈现爆发式增长,但计算能力加起来却十分有限,量子计算如果一旦落地使用,将会呈现颠覆式跨越。

2015年,英特尔就与学术界合作伙伴QuTech一起加快量子计算的研发,2017年10月,双方携手成功测试了17量子比特超导计算芯片。而在CES 2018期间,英特尔正式向QuTech交付了首个49量子比特量子计算测试芯片。

三个月,实现从17量子比特到49量子比特的跨越,迭代速度是显而易见的。对于英特尔来说,这意味着,量子计算虽然经历了将近40年历史,直到今天才迈出万里长征的第一步,但毫无疑问的是,属于英特尔的“量子霸权”时机已经来临。

●神经拟态研究原型芯片Loihi

神经拟态计算的灵感来自我们目前对大脑结构及其计算能力的了解。英特尔神经拟态研究原型芯片Loihi包括模仿大脑基本机制的数字电路,从而让机器学习变得更快、更高效,同时对计算力的需求更小。与训练人工智能系统的通用计算芯片相比,Loihi芯片的能效提升了1000倍。

英特尔科学家把罗莎林·富兰克林造型的摇头娃娃作为训练工具,将其360度旋转,让Loihi能够从每一个角度记住罗莎林。训练了一次后,Loihi便能在4秒钟内从少量图片中区分一个橡胶鸭子、一个玩具大象和摇头娃娃。尽管研究院只给出了罗莎林的一个背影,Loihi还是能够快速辨别出来。虽然这个实验只使用了Loihi不到1%的芯片资源,但它表明了架构的有效性。

专家预测,机器人将是神经拟态计算的杀手级应用。在智能家庭的应用中,想要入室抢劫的小偷,在进入房间时就可能被智能监控摄像头中的Loihi所识别,并发出警报;在汽车应用中,Loihi还可能扮演“交警”的角色,缓解交通压力,或是识别汽车、自行车的运动;在工业领域,Loihi也许会化身为一丝不苟的“监工”,监测小到滚珠轴承、大到修建路桥的一切工业应用。“神经拟态芯片将帮助人们减少一些繁重而耗时的工作”,

●人工智能

英特尔中国研究院院长宋继强认为,如果终极AI的智能程度是100%的话,那么当下AI的智能程度也就10%。也就是说,AI还处于婴儿期,依然有着巨大的成长空间。

在计算机和算法创新的推动下,人工智能的变革性力量预计将对社会产生重大影响。现在,英特尔正在运用自身的优势,推动摩尔定律和制造领先地位,为市场带来各种产品——英特尔至强处理器、英特尔 Nervana技术、英特尔Movidius技术和英特尔FPGAs ——以便从网络边缘到数据中心和云计算平台,来满足人工智能计算任务的独特需求。

正如之前所述,英特尔的独特之处在于能够提供多元化的解决方案,能够提供适应不同工作负载和能耗的产品,而不是其中的一两项。这样,用户既可以将自己的应用与通用软件融合在一起,选择在至强处理器上运作;同时,如果有更加细分的工作要求,也可以选择从通用处理器转向更加具体的处理器:如果想要低延迟,就可以使用FPGA;如果是想更注重低能耗,就可以使用

Movidius;如果想追求诸如数据中心这样的高性能,就可以使用至强。

在宋继强看来,“任何一种说用一种芯片或者说一种架构方式全处理所有的问题,都是太过夸张的。”因为很多AI应用都还未完成,而且可以预见的趋势是算法带来的红利将越来越少,边际效应呈逐级递减态势。俗话说,“是骡子是马,拉出来溜溜”,等到AI应用出来需要真正落地的时候,就需要所有人开始真正按照产品而不是学术的方式思考,不同的计算能力适合不同的应用,不同的硬件需要逐一接受市场检验。

-

英特尔

+关注

关注

61文章

9903浏览量

171552 -

cpu

+关注

关注

68文章

10831浏览量

211211 -

人工智能

+关注

关注

1791文章

46909浏览量

237684

原文标题:节点工艺命名藏猫腻,英特尔主动出击正视听

文章出处:【微信号:edn-china,微信公众号:EDN电子技术设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体制程微缩将在2024年以前告终

英特尔10纳米可实现多达25%的性能提升

【AD新闻】英特尔解读全球晶体管密度最高的制程工艺

英特尔半导体制程的节点命名

半导体工艺几种工艺制程介绍

三星加速制程微缩 DRAM进入40纳米世代

半导体制程再微缩下去,还有经济效益吗?

制程工艺是什么?

什么叫“制程工艺”?超微缩的意义是什么?

什么叫“制程工艺”?超微缩的意义是什么?

评论