硬件乘法器是现代计算机中必不可少的一部分,其基础是加法器结构。

硬件乘法器,其基础就是加法器结构,它已经是现代计算机中必不可少的一部分。[1]乘法器的模型就是基于“移位和相加”的算法。在该算法中,乘法器中每一个比特位都会产生一个局部乘积。第一个局部乘积由乘法器的LSB产生,第二个乘积由乘法器的第二位产生,以此类推。如果相应的乘数比特位是1,那么局部乘积就是被乘数的值,如果相应的乘数比特位是0,那么局部乘积全为0。每次局部乘积都向左移动一位。

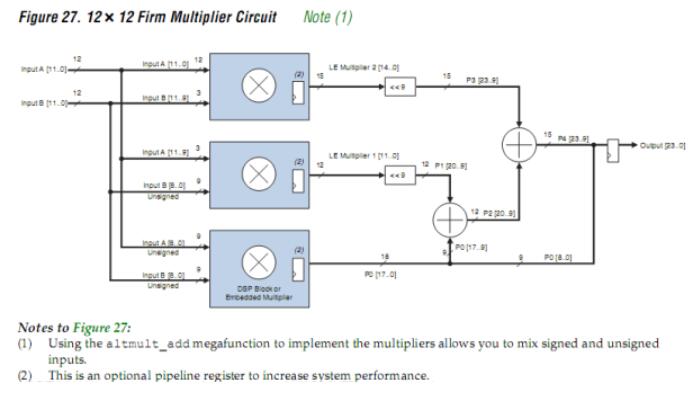

乘法器可以用更普遍的方式来表示。每个输入,局部乘积数,以及结果都被赋予了一个逻辑名称(如A1、A2、B1、B2),而这些名称在电路原理图中就作为了信号名称。在原理图的乘法例子中比较信号名称,就可以找到乘法电路的行为特性。

在乘法器电路中,乘数中的每一位都要和被乘数的每一位相与,并产生其相应的乘积位。这些局部乘积要馈入到全加器的阵列中(合适的时候也可以用半加器),同时加法器向左移位并表示出乘法结果。最后得到的乘积项在CLA电路中相加。注意,某些全加器电路会将信号带入到进位输入端(用于替代邻近位的进位)。这就是一种全加器电路的应用;全加器将其输入端的任何三个比特相加。

随着乘数和被乘数位数的增加,乘法器电路中的加法器位树也要相应的增加。通过研究CLA电路的特性,也可以在乘法器中开发出更快的加法阵列。

电路结构

从理论上讲,两个二进制N位操作数相乘,乘积的总宽度为2N,因此需要一个宽度为2N的移位寄存器和加法器。但在实际执行过程中,一是每个部分积的宽度和移位相加的有效宽度都为N位,从资源的利用率角度考虑,仅需N位宽度的加法器即可;二是按照先移位再相加的原理,两个N位操作数则需要2N个时钟周期才能完成整个运算,在此考虑将移位和相加两个运算步骤合并,从速度上就可在N个时钟周期内完成。

根据上述分析,8位移位相加型硬件乘法器应包括16位锁存器、8位移位寄存器、8位乘法器、8位加法器等4个组成部分。具体电路结构如图1所示。

锁存器发挥着锁存的作用,用于锁存部分和。

移位寄存器则具备移位作用,当加载信号有效时乘数将加载于8位右位寄存器,随着时钟上升沿的到来,乘数即由低位开始逐位移出。

乘法器功能类似一个特殊的与门。有两个输入端口,一个端口用于输入8位并行操作数(被乘数),另一个端口在时钟信号控制下输入由移位寄存逐步移出的串行操作数,并将这两个操作数进行与运算。

加法器用于将本次时钟脉冲控制下得到的8位部分积与锁存于锁存器高8位的前一个时钟脉冲下得到的部分和相加。

-

硬件乘法器

+关注

关注

0文章

5浏览量

2621

原文标题:硬件乘法器

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

查表式硬件乘法器

AVR的硬件乘法器8X8的吗?

硬件乘法器的相关资料分享

MSP430F5系列16位超低功耗单片机模块原理10

MSP430教程Chapt12-硬件乘法器

硬件乘法器原理_硬件乘法器电路结构

加法器结构和硬件乘法器的基础使用工程文件免费下载

MSP430X1XX系列硬件乘法器,比较器,flash讲解

硬件乘法器是什么?

硬件乘法器是什么?

评论