Synopsys设计平台用于高性能、高密度芯片设计

重点:

Synopsys设计平台获得TSMC工艺认证,支持高性能7-nm FinFET Plus工艺技术,已成功用于客户的多个设计项目。

针对7-nm FinFET Plus工艺的极紫外光刻技术,IC Compiler II 进行了专门的优化,进一步节省芯片面积。

采用TSMC的Wafer-on-Wafer®(WoW)技术,平台内全面支持多裸晶芯片堆叠集成,从而提高生产效率,加快实现大批量生产。

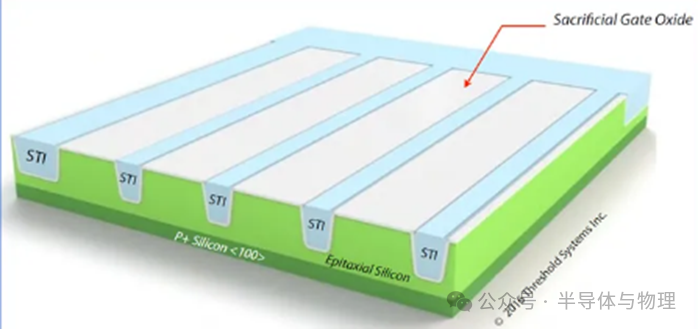

全球第一大芯片自动化设计解决方案提供商及全球第一大芯片接口IP供应商、信息安全和软件质量的全球领导者Synopsys(NASDAQ: SNPS)近日宣布,Synopsys 设计平台获得TSMC最新工艺认证,符合TSMC最新版设计规则手册(DRM)规定的7-nm FinFET Plus先进工艺技术的相关规范。目前,基于Synopsys 设计平台完成的数款测试芯片已成功流片,多位客户也正在基于该平台进行产品设计研发。Synopsys设计平台在获得TSMC的此项认证后,将可以更加广泛地用于基于此工艺技术的芯片设计,包括高性能、高密度计算和低功耗移动应用。

该认证意味着TSMC极紫外光刻(EUV)工艺取得显著进步。与非EUV工艺节点相比,前者的芯片面积显著减少,但仍保持卓越的性能。

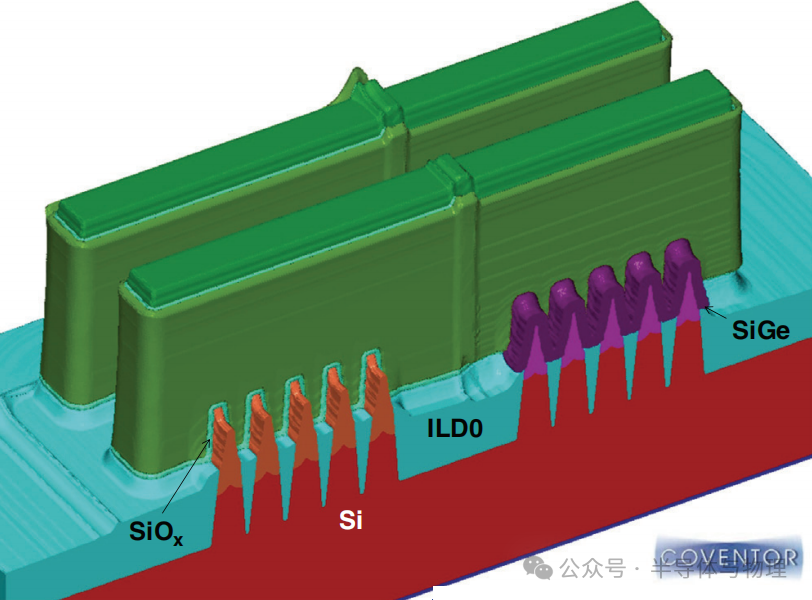

以Design Compiler® Graphical综合工具和IC Compiler™II布局布线工具为核心Synopsys设计平台性能显著增强,可充分利用TSMC的7-nm FinFET Plus工艺实现高性能设计。Design Compiler Graphical可以通过自动插入过孔支柱(via-pillar)结构,提高性能以及防止信号电迁移(EM)违规,并且可将信息传递给IC Compiler II进行进一步优化。它还会在逻辑综合时自动应用非默认规则(NDR),并感知绕线层以优化设计、提高性能。这些优化(包括IC Compiler II总线布线),将会在整个布局布线流程中继续进行,以满足高速网络严格的延迟匹配要求。

PrimeTime®时序分析工具全面支持先进的波形传播(AWP)技术和参数化片上偏差(POCV)技术,并已经进行充分优化,可解决更高性能和更低电压场景中波形失真和非高斯分布偏差造成的影响。此外,PrimeTime感知物理信息的Sign-off扩展了对过孔支柱的支持。

Synopsys强化了设计平台功能,可以执行物理实现、寄生参数提取、物理验证和时序分析,以支持TSMC的WoW技术。其中基于IC Compiler II的物理实现流程,全面支持晶圆堆叠设计,包括最初的裸晶布局规划准备到凸块(bumps)布局分配,以及执行芯片布线。物理验证由Synopsys 的IC Validator工具执行DRC/LVS检查,由StarRC™工具执行寄生参数提取。

TSMC设计基础架构营销事业部资深处长Suk Lee表示:“与Synopsys的持续合作以及TSMC 7-nm FinFET Plus工艺技术的早期客户合作,使我们可以提供差异化的平台解决方案,帮助我们的共同客户更快地将开创性新产品推向市场。Synopsys设计平台成功通过认证,让我们共同客户的设计方案首次实现了基于EUV工艺技术的批量生产。”

Synopsys设计事业群营销和业务开发副总裁 Michael Jackson说:“我们与TSMC就7-nm FinFET Plus量产工艺进行合作,使客户公司可以放心地开始运用高度差异化的Synopsys 设计平台,设计日益庞大的SoC和多裸晶堆叠芯片。TSMC 7-nm FinFET Plus工艺认证,让我们的客户可以享受到先进的EUV工艺所带来的功率和性能上的显著提升,以及面积更大程度的节省,同时加快了其差异化产品的上市时间。”

-

芯片

+关注

关注

459文章

51583浏览量

429828 -

IC

+关注

关注

36文章

6018浏览量

176979

发布评论请先 登录

相关推荐

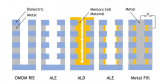

ALD和ALE核心工艺技术对比

消息称台积电3nm、5nm和CoWoS工艺涨价,即日起效!

深度解析安森美Treo平台

安森美推出基于BCD工艺技术的Treo平台

锐成芯微推出基于8nm工艺的PVT Sensor IP

所谓的7nm芯片上没有一个图形是7nm的

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证

台积电高雄与宝山晶圆厂扩建,1.4nm(A14)工艺制造增添两阶段

TSMC和Synopsys将在生产中使用NVIDIA计算光刻平台

什么是BCD工艺?BCD工艺与CMOS工艺对比

Synopsys设计平台获得TSMC工艺认证_7-nm FinFET Plus工艺技术

Synopsys设计平台获得TSMC工艺认证_7-nm FinFET Plus工艺技术

评论