将Quartus II中FPGA管脚的分配及保存方法做一个汇总。本文首先介绍了FPGA 的管脚分配方法,其次介绍了Quartus II自动添加管脚分配的方法,最后阐述了FPGA管脚分配文件保存方法,具体的跟随小编一起来了解一下吧。

一、管脚分配方法

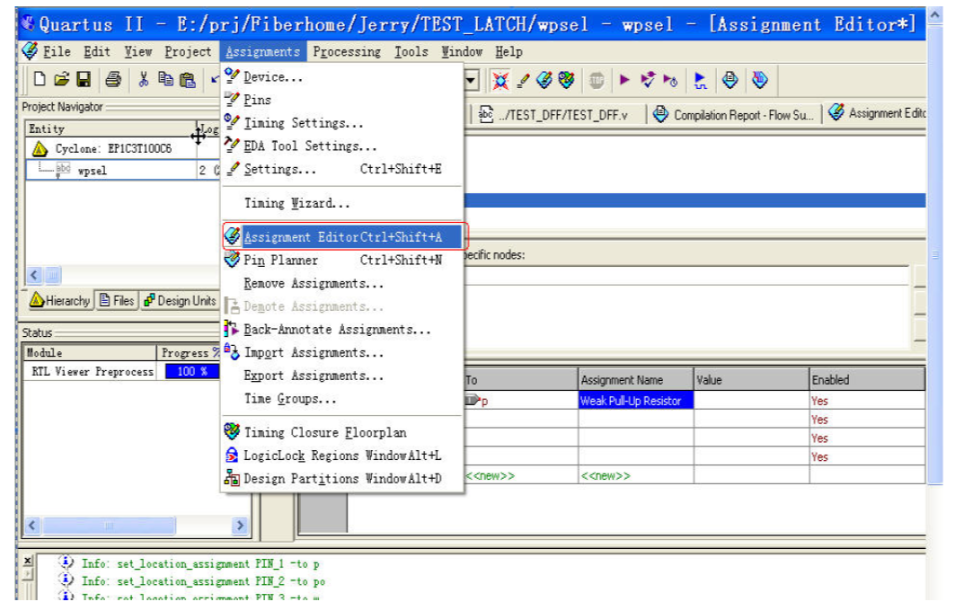

FPGA 的管脚分配,除了在QII软件中,选择“Assignments -》Pin”标签(或者点击按钮) ,打开Pin Planner,分配管脚外,还有以下2种方法。

方法一:Import Assignments

步骤1:

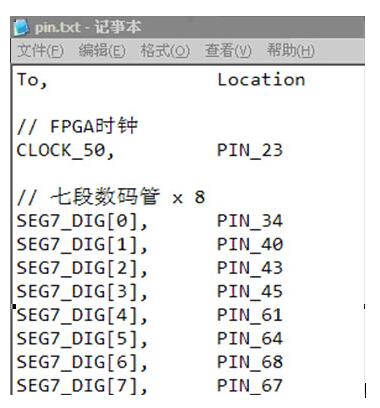

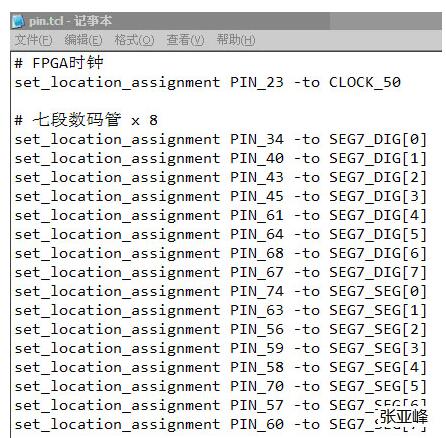

使用记事本或类似软件新建一个txt文件(或csv文件),按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。【这种方式格式最为简单】

注意:To和Location两个关键字中间有一个半角逗号。

图1 pin.txt

步骤2:

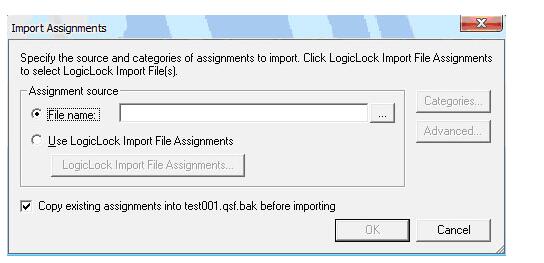

在QII软件中,选择“Assignments -》 Import Assignments”。如图所示,导入xxx.txt或者xxx.csv文件即可

图2 导入pin.txt

步骤3:

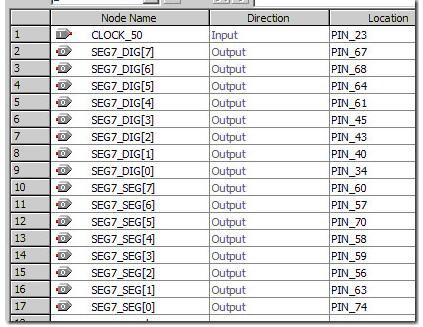

在QII软件中,选择“Assignments -》 Pin”标签(或者点击 按钮) ,打开Pin Planner,验证管脚是否分配正确。

图3 验证管脚是否分配正确

方法二:导入source xxx.tcl文件

步骤1:

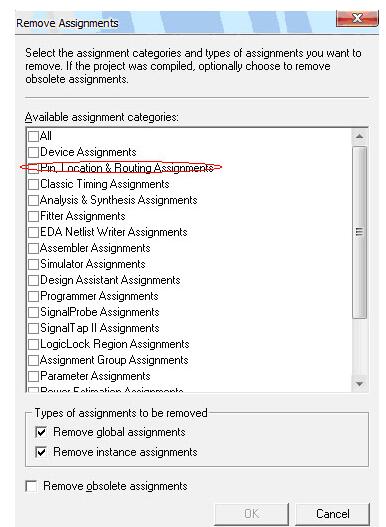

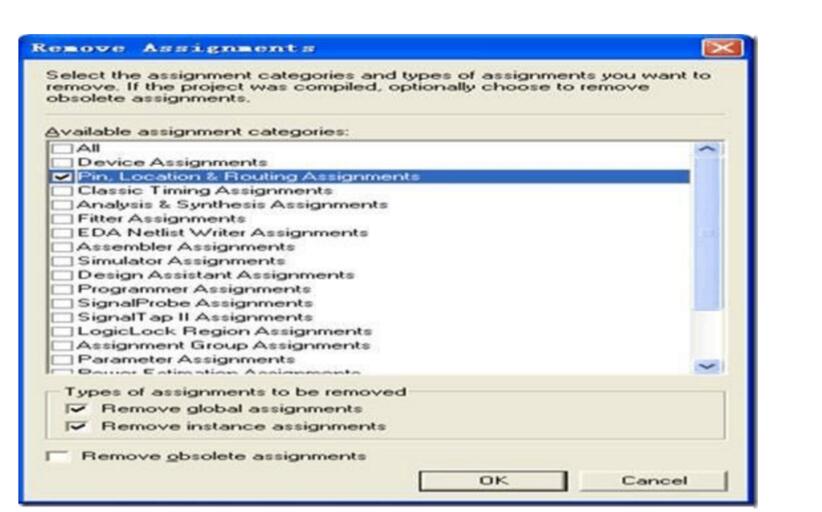

在QII软件中,使用“Assignments -》 Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

图4 Remove Assignments

注:在未执行任何管脚分配操作新工程中,可跳过步骤1。

步骤2:

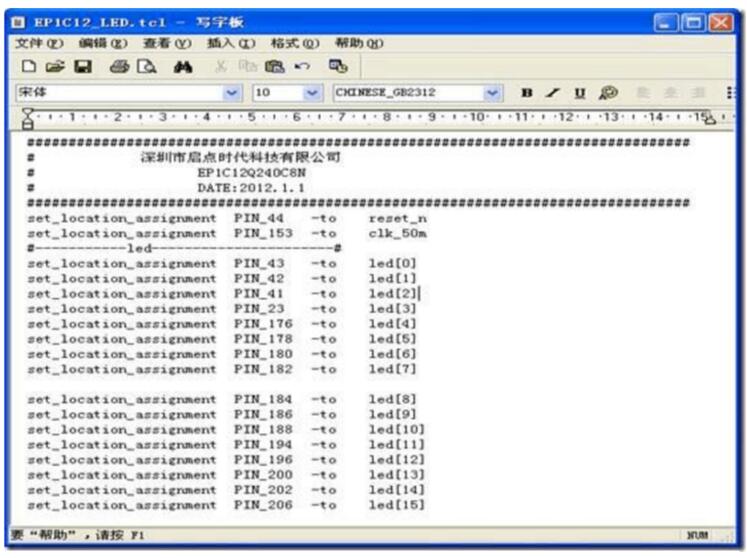

使用记事本或类似软件新建一个tcl文件,按如下格式编写管脚分配内容(不同的开发版,其内容也不同,本文以我使用的DIY_DE2开发板为范例)。

注意关键字set_location_assignment和-to的用法。

图5 pin.tcl

步骤3:

执行pin.tcl

方法1:在QII软件中,使用“View -》 Utility Windows -》 Tcl Console”标签,打开Quartus II Tcl Console。执行语句:

图6 source pin.tcl

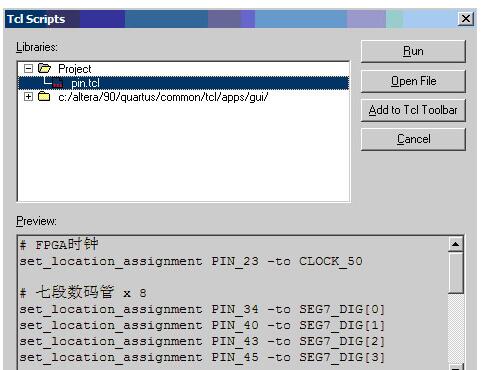

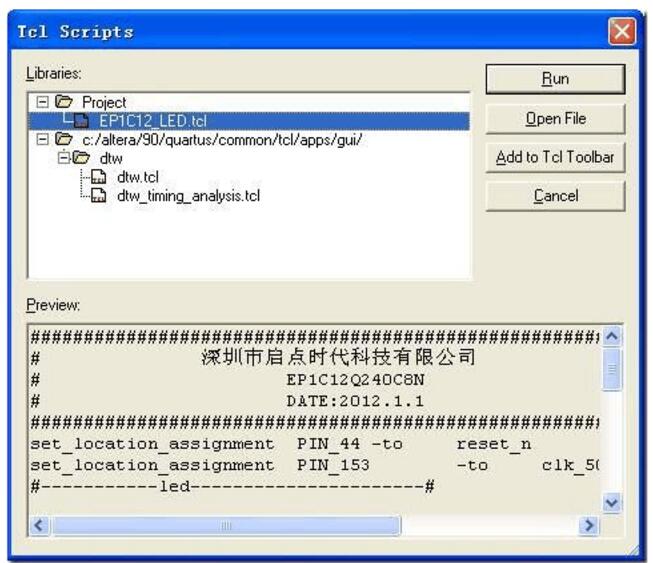

方法2:在QII软件中,使用“Tools -》 Tcl Scripts …”标签,打开Tcl Scripts。

图7 Tcl Scripts

选择pin.tcl,选择“Run”标签,执行Tcl文件。

步骤4:

同方法1的步骤3。

步骤1:在QII软件中,使用“Assignments —— Remove Assignments”标签,移除管脚分配内容,以确保此次操作,分配的管脚没有因为覆盖而出现错误的情况。

注:在未执行任何管脚分配操作新工程中,可跳过步骤1。

步骤2:使用记事本或类似软件新建一个TCL文件,按如下格式编写管脚分配内容(以EP1C12的 例程为例)

我们命名的名字就是后面那部分,PIN_*是FPGA硬件上癿引脚,-to后面的就是对应的名字 如

set_location_assignment PIN_153 -to clk_50m

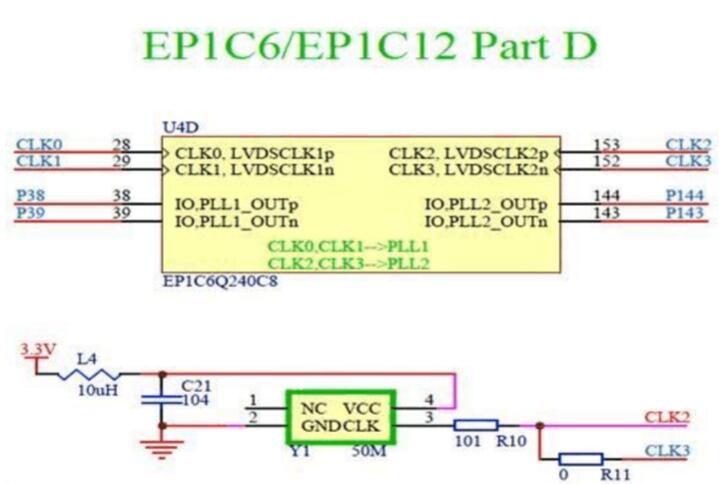

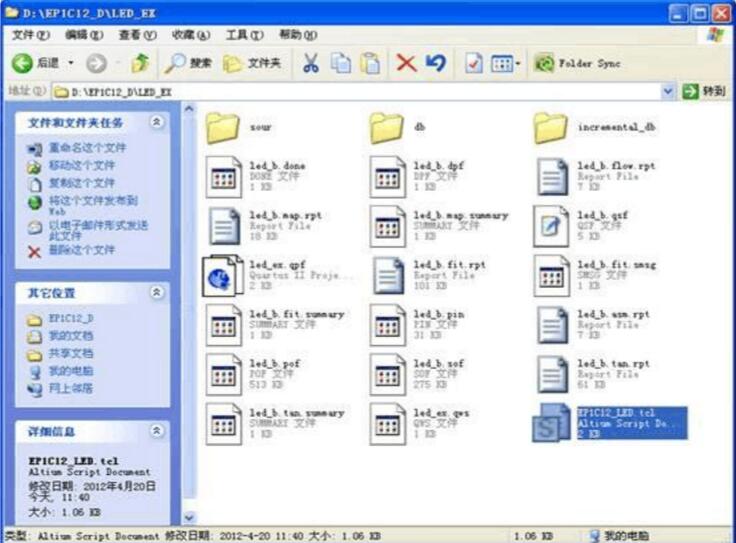

我们可以看到,原理图中50MHz晶振Y1(CLK2)接的就是FPGA的153脚。 步骤3:将新建的TCL文件放到工程目录文件夹下。

步骤4:执行pin.tcl。

在QII软件中,使用“Tools —— Tcl Scripts „”标签,打开Tcl Scripts

选择pin.tcl,选择“Run”标签,执行Tcl文件。

如下所示,又看见Successfully了吧,返说明我们脚本文件运行成功了

二、Quartus II自动添加管脚分配的方法

对CPLD大量管脚进行分配是件头疼的事情。在Pin Planner里逐一添加比较麻烦。或者布线改动较多时需要逐一修改。

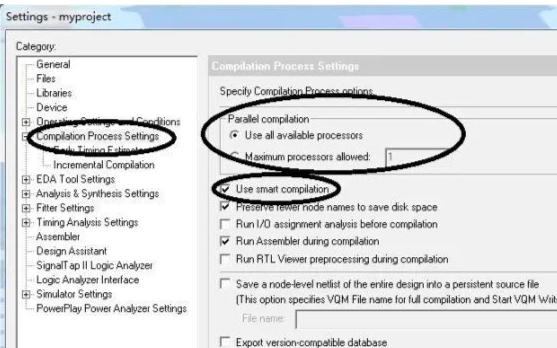

可以通过内置tcl命令进行自动添加,步骤如下:

1. 新建一个文本文件,例如pin.txt

2. 添加多条管脚分配命令

set_location_assignment PIN_123 -to MODULE_PORT

其中,PIN_123是管脚123的编号,其它的类似。MODULE_PORT是TOP模块的端口。

如果端口是多位的,则需使用如下命令

set_location_assignment PIN_123 -to MODULE_PORT[n]

其中,n表示端口的第n位

3. 在Quartus中打开Tcl console,可以通过快捷键Alt+2打开

4. 在Tcl console中粘贴pin.txt中所有命令,回车执行

5. 自动分配完成!可以在Pin Planner中查看分配结果。保留pin.txt用于未来管脚的更改。

三、FPGA管脚分配文件保存方法

使用别人的工程时,有时找不到他的管脚文件,但可以把他已经绑定好的管脚保存下来,输出到文件里。

方法一:

查看引脚绑定情况,quartus -》 assignment -》 Pins,打开FPGA引脚界面,在这个界面的菜单中可以保存引脚文件为csv格式(表格形式)和tcl格式。

步骤:File -》 Export… -》 选择保存名字和保存格式。

方法二:

直接输出管脚配置,assignmengt -》 Export assignmengt,可以保存配置为qsf格式,该格式可以用记事本查看,在该文件中同样包含了引脚信息。注意:保存时会在原工程文件夹下新建一个文件夹。

至于元件的其它配置方式,可以在qsf文件和tcl文件中用语句来设置,也可以在Assignment -》 device,界面中设置。

加载:

使用已经有的引脚文件时,在选项assignment -》 Import assignment,中可以选择要加载的引脚文件。此时,可以加载qsf 和 csv(或txt)文件。

保存的csv(txt)文件、qsf文件 和 tcl文件的区别:

csv(txt)文件:包含芯片所有管脚信息,包括分配的和未分配的;

qsf文件:包含管脚分配信息和芯片信息;

tcl文件:只包含已分配管脚信息。

-

FPGA

+关注

关注

1629文章

21729浏览量

602964 -

管脚分配

+关注

关注

1文章

5浏览量

7466

发布评论请先 登录

相关推荐

我想问下,在quartus II 11版中运行了tcl的管脚分配文件,消...

quartus ii 遇到的问题!!!!

Quartus II打开Pin Planner后在管脚分配时有一项Reserved不知道里面列表的含义

Quartus II 下FPGA管脚锁定

quartus ii使用教程,中文教程

Quartus II中管脚上拉电阻应该如何设置

一文详解Quartus II自动添加管脚分配的方法

一文详解Quartus II自动添加管脚分配的方法

评论