笔者多年来反复用一道面试题来考察IC求职人员的水平和能力。这道面试题看似平淡无奇,大部分求职者却只知其一不知其二,知其然而不知其所以然。这是一道怎样的奇葩题目呢:

请设计一个异步复位的计数器:“从0到20的无限循环计数,每次计数到20便清0从头开始计数。”

看到这里有没有心想“Are you kidding me? So simple?”?其实不然,对于初学者而言,这其实是一个连环无敌面试题。欲知详情,请见本文一一拆解。

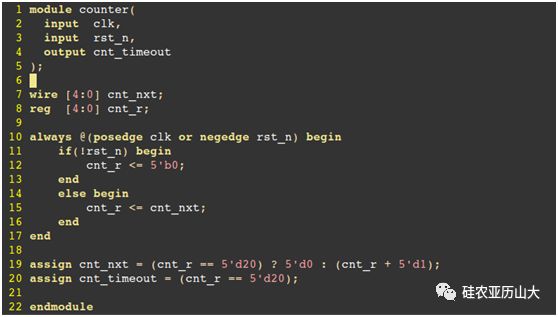

问题1:如何用Verilog实现这个计数器?

针对上述功能的计数器,应该如何用Verilog实现?

一般而言,大多数学过Verilog语言的人,这一个问题都能回答清楚,初步的解题思路如下:

模块有2个输入:时钟clk,复位rst_n(此处用下降沿有效的复位为例)

模块有1个输出:每次计数到20时,输出信号cnt_timeout拉起一拍

完整的Verilog代码如下:

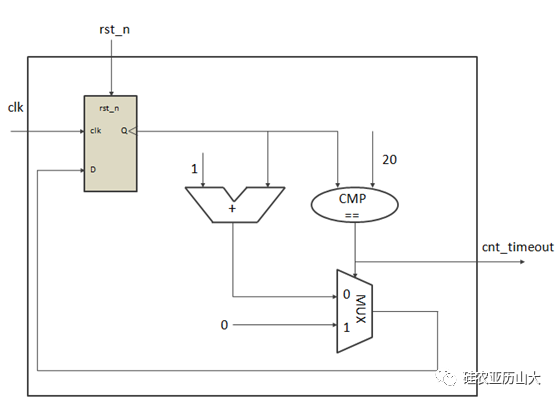

问题2:此计数器代表的实际电路是什么?

在面试的学生回答出如何用Verilog实现计数器后,第二个问题笔者就会问:

用Verilog实现的这个计数器背后的实际电路是什么?如果给你提供多个D触发器,多个比较器,多个加法器,多个多路选择器,你怎么组合出这个电路?

经过笔者的实验统计,这个问题大概有30%的人能不假思索的回答出来,剩下的大概20%在经过引导后也能说出自己的思路和答案,而经过引导也没有思路的50%则存在着“只知语法不知电路”的问题,需要进一步学习提高。

完整电路如下:

问题3:此计数器的关键路径是哪一条?

初学者如果能够回答出上一个问题,那么说明对于电路的理解已经相当的不错,那么接下来的问题便是 :“以上电路的关键路径在哪里”?

绝大多数的面试学生对于这个问题是难以回答的,主要原因是,不理解关键路径的含义,或者找不出关键路径。

正确答案如下:关键路径应该是从“寄存器的Q端”->加法器(ADD)->多路选择器(MUX)->“寄存器的D端”。

有关关键路径(Critical Path)的概念需要初学者自行查阅学习。

如果能够回答出上述问题,那么可以继续反问面试学生:为什么关键路径不是从“寄存器的Q端”->比较器(CMP)->多路选择器(MUX)->“寄存器的D端”。即:比较器(CMP)和加法器(ADD)哪个更关键,有关此问题,请参见后续问题。

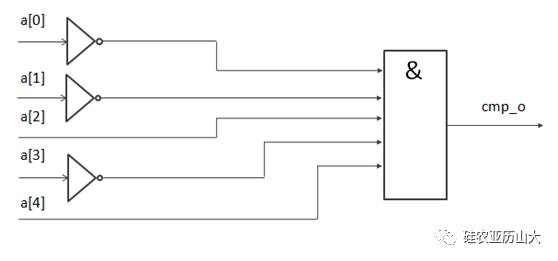

问题4:“cnt == 20”对应的电路是什么?

上述电路中的比较器其实是“cnt == 20”,那么这段比较器代码对应的电路是什么呢?此问题非常简单,但是绝大多数初学者是回答不出来的。

正确答案:20的2进制表示为5’b10100,那么“等于”20的电路逻辑如下图所示,即对应0的位取反,对应1的位不取反,将其与在一起。此乃大二数电的基本知识。

注意:只有“等于”常数才能得到如此简洁的电路,如果是两个变量的“等于”比较则必须使用“同或”电路来实现,“同或”电路是什么逻辑?查一查大二数电的基本知识。

问题5:使用“cnt > 19”和“cnt == 20”一样吗?

针对上述电路中的比较器,接下来的问题是 :“用cnt > 19来代替cnt == 20行吗? 为什么”?

一个对电路有深刻理解的人应该不仅仅能回答出行不行,还能说出为什么。

正确答案如下:功能上是可行,但从电路优化的角度看,是不行的。

因为“cnt == 20”如上文所述,实现相对简单,用少量的非门及与门即可实现。但“cnt > 19” 的电路逻辑更为复杂。

具体的“cnt > 19”的电路是怎样的呢?对于这个5bit的“cnt > 19”, cnt可能的范围取值为[20:31],综合工具会将电路优化成几个等于相与:“cnt == 20 && cnt == 21 && …… && cnt == 31”。显然“cnt > 19”的电路实现比“cnt == 20”复杂许多。所以此处用“cnt > 19”是不合适的,会带来额外的硬件开销。

上述5 bit的大于的比较电路,因为cnt的可能的取值范围是[20:31],综合工具能将电路优化成几个等于相与,但假设cnt是32 bit的,那“cnt > 19”所代表的cnt的可能的取值范围太大,此时对于32bit的“cnt > 19”,则相当于“cnt – 19 > 0”,此比较器映射的电路将引入一个加法器。

问题6:加法器的电路是什么?

加法器的电路比较复杂,以后的系列会专门讲加法器:“登堂设计案例之:加法器真的就是写个+号这么简单吗?”。

但有一点是可以肯定的:如采用“cnt==20”的比较器,上述计数器中的加法器的延时肯定是大于比较器的。

所以,关键路径是上面所述的“寄存器的Q端”->加法器(ADD)->多路选择器(MUX)->“寄存器的D端”。

附加问题:如何验证这个计数器?

如果学生是面试IC验证工程师岗位的,此时不妨加上一些验证相关的问题:

如何验证这个计数器?

你的TB的组成是怎样的?

列举一下针对这个计数器功能描述提取的测试点?由于此系列以Verilog设计为主要讲解主题,所以验证的问题在此不深入展开讨论。

基于这个简单的计数器,您还能想出什么衍生问题可以加入这一系列的面试题呢?

结语

最后,我们总结下核心要义:Verilog只是一种硬件描述语言,IC设计的本质是对于电路的设计,虽然现在Verilog Coding采用RTL级别的抽象描述,但是必须清楚所描述的代码能够映射出的电路结构,对其面积和时序的影响都了然于胸,只有如此才能够成为一名优秀的IC设计工程师。

-

Verilog

+关注

关注

28文章

1352浏览量

110469 -

计数器

+关注

关注

32文章

2276浏览量

95073

原文标题:入门设计基础之:无敌的面试题--计数器

文章出处:【微信号:real_farmer,微信公众号:硅农亚历山大】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

java基础练习、面试题

这样的面试题 ,你敢回答吗?

java经典面试题深度解析

c语言面试题,c++面试题下载

Java的经典面试题和答案详细说明

一个连环无敌面试题--计数器

一个连环无敌面试题--计数器

评论