FPGA即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。本文主要介绍的是FPGA开发流程及VHDL基本语法,具体的跟随小编来了解一下。

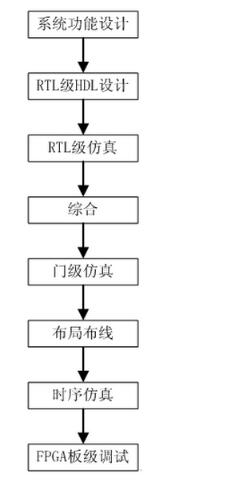

FPGA开发流程详解

1) 系统功能设计

在系统设计之前,首先要进行的是方案论证、系统设计和FPGA芯片选择等准备工作。

一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元。

2) RTL级HDL设计

RTL级(Register Transfer Level,寄存器传输级)指不关注寄存器和组合逻辑的细节(如使用了多少个逻辑门、逻辑门的连接拓扑结构等),通过描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型的HDL设计方法。

RTL级比门级更抽象,同时也更简单和高效。RTL级的最大特点是可以直接用综合工具将其综合成为门级网表,其中RTL级设计直接决定着系统的功能和效率。

3) RTL级仿真

也称为功能(行为)仿真,或是综合前仿真,是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。

仿真前,要先利用波形编辑器和HDL等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中观察各个节点信号的变化。虽然仿真是非必需步骤,但却是系统设计中最关键的一步。为了提高功能仿真的效率,需要建立测试平台testbench,其测试激励一般使用行为级HDL语言描述。

4) 综合

所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。

就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。

5) 门级仿真

也称为综合后仿真,综合后仿真检查综合结果是否和原设计一致。

在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。但这一步骤不能估计线延时,因此和布线后的实际情况还有一定的差距,并不十分准确。目前的综合工具较为成熟,对于一般的设计可以省略这一步,但如果在布局布线后发现电路结构和设计意图不符,则需要回溯到综合后仿真来确认问题之所在。

6) 布局布线

实现是将综合生成的逻辑网表配置到具体的FPGA芯片上,将工程的逻辑和时序与器件的可用资源匹配。布局布线是其中最重要的过程,布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。也可以简单地将布局布线理解为对FPGA内部查找表和寄存器资源的合理配置,布局可以被理解挑选可实现设计网表的最优的资源组合,而布线就是将这些查找表和寄存器资源以最优方式连接起来。

目前,FPGA的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分资源的使用情况。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

7) 时序仿真

是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等)现象。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。由于不同芯片的内部延时不一样,不同的布局布线方案也给延时带来不同的影响。因此在布局布线后,通过对系统和各个模块进行时序仿真,分析其时序关系,估计系统性能,以及检查和消除竞争冒险是非常有必要的。

8) FPGA板级调试

通过编程器将布局布线后的配置文件下载至FPGA中,对其硬件进行编程。配置文件一般为.pof或.sof文件格式,下载的方式包括AS(主动)、PS(被动)、JTAG(边界扫描)等方式。

VHDL基本语法详解

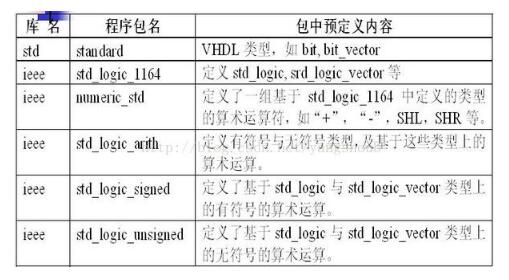

1、引用库

library IEEE; //表示打开IEEE库,因为IEEE库不属于VHDL的标准库,所以使用库的内容要先声明

use ieee.numeric_std.all; //USE和ALL是关键词,表示允许使用IEEE库中numeric_std程序包中的所有内容,这个程序包主要是用来做数据类型转换

use ieee.std_logic_unsigned.all;

use ieee.std_logic_misc.all;

use ieee.std_logic_1164.all;

library UNISIM; //UNISIM是xilinx的库函数,为了仿真使用。Using this declaration, the simulator references the functional models for all device primitives. In addition to this declaration, you must compile the library and map the library to the simulator.

use UNISIM.VCOMPONENTS.ALL;

程序包的使用都可以在EDIT-》language templates-》VHDL-》Common Constructs-》Convertion Functions中找到例子。

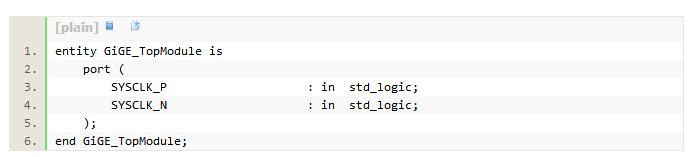

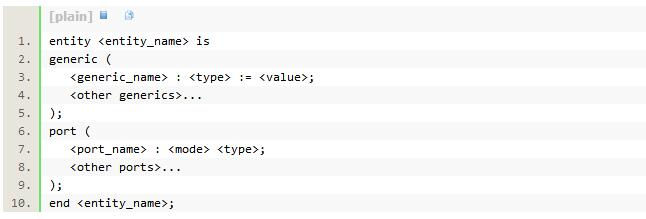

2、实体entity

实体类似于原理图中的一个部件符号,它并不描述设计的具体功能,只是定义所需的全部输入/输出信号。

举例:

套用EDIT-》language templates-》VHDL-》Common Constructs-》Architecture Components & entity的举例

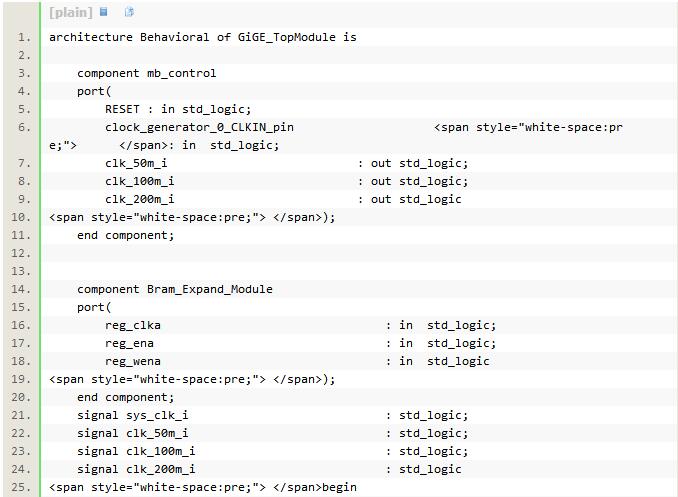

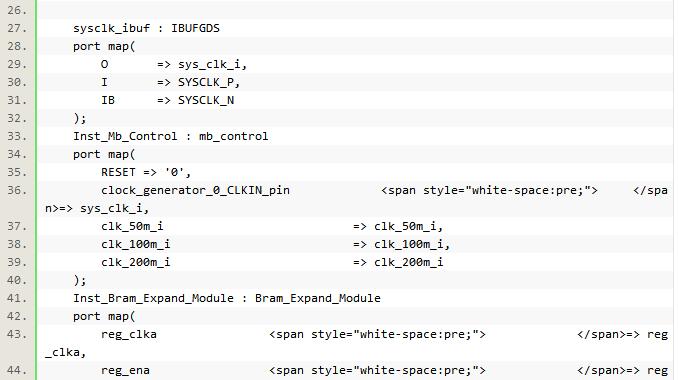

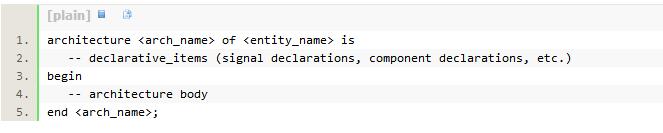

3、结构体architecture

所有能被仿真的实体都由结构体(ARCHITECTURE)描述,即结构体描述实体的结构或行为,一个实体可以有多个结构体,每个结构体分别代表该实体功能的不同实现方案。

结构体名是对本结构体的命名,它是该结构体的惟一名称,虽然可以由设计人员自由命名,但一般都将命名和对实体的描述结合起来,结构体对实体描述有三种方式(括号中为命名):

1) 行为描述(BEHAVE):反映一个设计的功能和算法,一般使用进程PROCESS,用顺序语句表达;(下例中的情况)

2) 结构描述(STRUCT):反映一个设计硬件方面的特征,表达了内部元件间连接关系,使用元件例化来描述;

3) 数据流描述(DATAFLOW):反映一个设计中数据从输入到输出的流向,使用并行语句描述

举例:

套用EDIT-》language templates-》VHDL-》Common Constructs-》Architecture Components & entity的举例

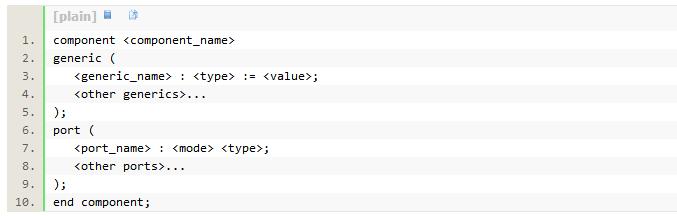

4、元件component

上面例子中有了component的例化,具体的:

-

vhdl

+关注

关注

30文章

817浏览量

128110 -

FPGA开发

+关注

关注

1文章

43浏览量

14909

发布评论请先 登录

相关推荐

FPGA入门:Verilog/VHDL语法学习的经验之谈

FPGA入门:基本开发流程概述

勇敢的芯伴你玩转Altera FPGA连载4:Verilog与VHDL

FPGA与VHDL快速工程实践从入门到提高

VHDL语言在FPGA/CPLD开发中的应用?

FPGA入门笔记_FPGA开发流程及VHDL基本语法

FPGA入门笔记_FPGA开发流程及VHDL基本语法

评论