很多计算机专业的学生都只是在理论层次学习计算机体系结构方面的知识,比如数据路径、控制结构和存储系统等,但是如何将这些组合起来则完全靠学生的想象力。MIPSfpga的出现让这一切迎刃而解,它不同于其他课程的地方在于首次采用了一款纯粹的商用软核CPU用于研究目的,用户可以在此课程的系统集成环境下详细、深入的探索计算机架构。

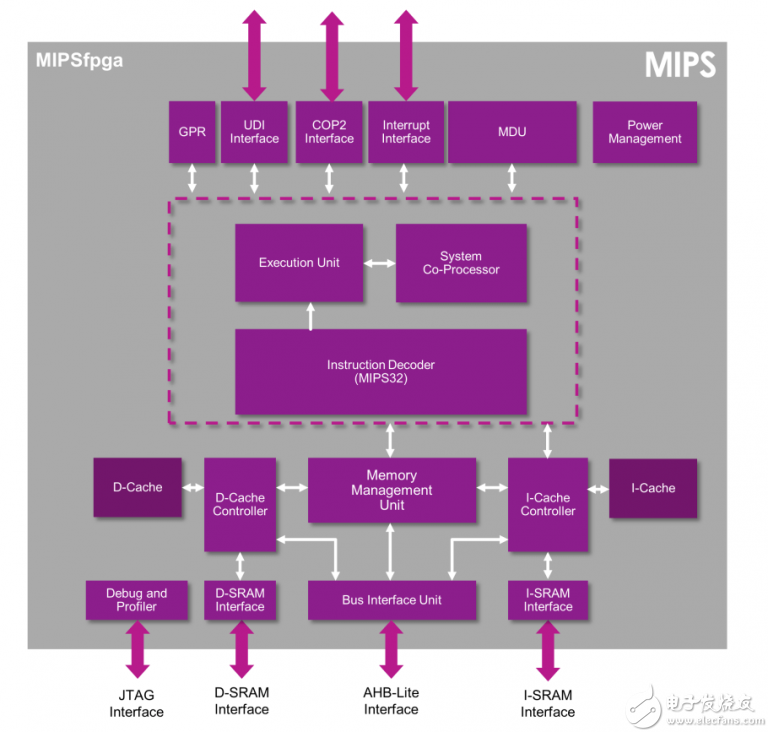

MIPSfpga使用一款MIPS系列软核IP——具体来讲是microAptiv核,PIC32MK处理器采用的既是此款软核。该核面向的是可编程逻辑门阵列(FPGA)。Imagination公司除了授权可以使用这款实用的MIPS软核处理器外,还准备了一系列的教学材料,从而可以使用户快速入门、开发,进而能够修改该处理器和系统。

该课程提供了三部分材料引导用户入门、使用和修改MIPSfpag:入门指南、实验实例和SoC资料包。

第一部分材料包括MIPSfpga用到的Verilog设计文件和一些介绍MIPSfpga系统和使用方法的文档。

第二部分材料(MIPSfpga实验实例)包含25个需要动手操作的实验,指导用户如何学习计算机架构和进行系统级的设计。比如,修改MIPSfpga系统与外设(如LCDs、传感器等)的接口、使用性能计数器和中断、改变缓存刷新策略、添加新的指令并且测量这些改变所带来的性能差异等。由于使用的商用编译器能够清晰的看到因架构或系统的修改带来的性能改变,也帮助用户在此方面的能力上得到较快的提升。

第三部分材料是MIPSfpga SoC,它向用户展示了如何基于MIPSfpga搭建片上系统(SoC)并且移植开源的Linux操作系统。

最新的MIPSfpga v2.0在2017年7月1日正式推出,在之前版本的基础上又增加了更多的特性和资源,比如增加了16个动手实验(即动手实验的个数从9个增加到25个),可以采用UART(串口)将程序下载到MIPSfpga,精简了启动代码,增加了Windows和Linux系统的安装指令,同时提供了Verilog和VHDL语言的系统级模块,支持快速调试通道(FDC)和用户自定义接口(UDI),支持使用printf这样的I/O指令并且允许用户定义自己的系统指令。

自从2015年5月以来,全世界已经有超过600所大学获得了授权并且下载使用MIPSfpga相关的资料--软核IP以及入门资料和实验练习。

通过提供全面开放的商业CPU IP软核和系统, 指导用户使用和修改处理器和系统,MIPSfpga正在转变计算机体系结构的教育方式。当然不仅这些,MIPSfpga还提供了一个在研究和高级项目中探索计算机架构特性和增强功能的平台。

这里提供了一些高级项目的链接,它们都是基于MIPSfpga实现的。

MIPS由于其足够简单和精致,在计算机架构教学中已经非常流行。MIPSfpga提供了一个强大的平台,将计算机架构和系统设计的理论教学与实践操作联系起来,从而让用户更加全面的了解计算机架构设计。

-

FPGA

+关注

关注

1630文章

21766浏览量

604577 -

mips

+关注

关注

1文章

239浏览量

47791 -

imagination

+关注

关注

1文章

574浏览量

61374

发布评论请先 登录

相关推荐

芯驿电子 ALINX 推出全新 IP 核产品线,覆盖 TCP/UDP/NVMe AXI IP 核

MicroBlaze V软核处理器的功能特性

基于国产异构双核(RISC-V+FPGA)处理器,AG32开发板开发资料

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景

FPGA的IP软核使用技巧

关于FPGA IP核

Achronix FPGA增加对Bluespec提供的基于Linux的RISC-V软处理器的支持,以实现可扩展数据处理

Achronix与Bluespec联合宣布推出一款支持Linux的RISC-V软处理器

MIPSfpga软核处理器IP设计方案

MIPSfpga软核处理器IP设计方案

评论