- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:30fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADI

+关注

关注

146文章

45941浏览量

253837 -

SAR ADC

+关注

关注

2文章

18浏览量

7623

发布评论请先 登录

相关推荐

Marvell展示2纳米芯片3D堆叠技术,应对设计复杂性挑战!

随着现代科技的迅猛发展,芯片设计面临着前所未有的挑战。特别是在集成电路(IC)领域,随着设计复杂性的增加,传统的光罩尺寸已经成为制约芯片性能和功能扩展的瓶颈。为了解决这一问题,3D堆叠技术应运而生

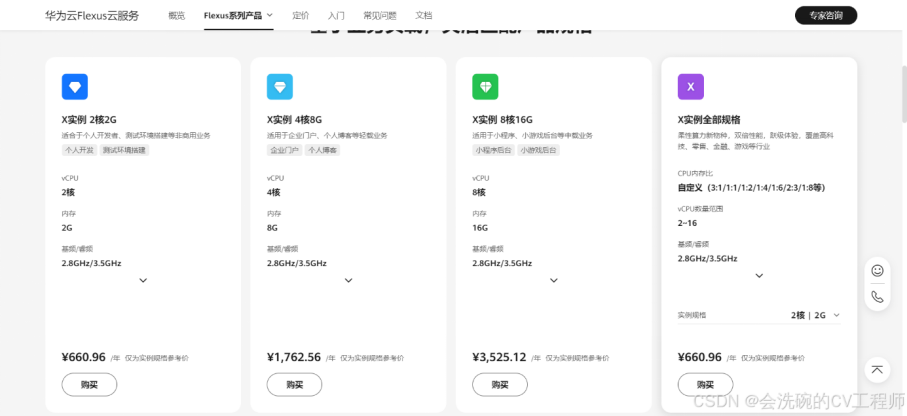

将 Vue 项目部署到 Flexus 云服务器 X 实例并实现公网访问

的云服务体验。 华为深刻洞察了中小企业和开发者在云服务应用中遇到的挑战,如资源规格刚性与用户多样化需求之间的矛盾、业务调优复杂性等,将柔性算力技术引入到服务器中,产生了 Flexus X

为什么隔离ADC的采样频率可以如此显著的提高?但是带宽反而降低了?

。(AMC1304x-Q1)

为什么隔离ADC的采样频率可以如此显著的提高?但是带宽反而降低了?

为什么隔离ADC都是基于 Δ-Σ 调制器的,其他结构的(比如SAR)没有?

发表于 12-06 06:42

一文聊聊自动驾驶测试技术的挑战与创新

随着自动驾驶技术的飞速发展,自动驾驶测试的重要性也日益凸显。自动驾驶测试不仅需要验证车辆的感知、决策、控制模块的独立性能,还需确保系统在复杂场景中运行的整体可靠性。然而,自动驾驶测试面

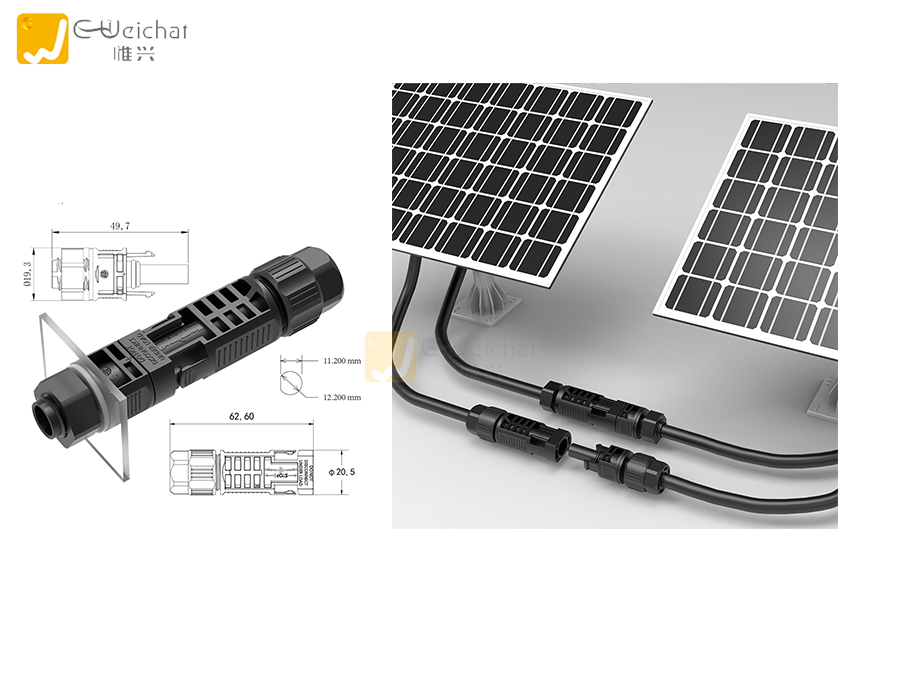

光伏连接器外壳:超越简单塑料的复杂性与重要性

将深入探讨光伏连接器外壳的设计要求及其超越简单塑料的复杂性与重要性。 一、光伏连接器外壳的设计要求 材料选择 光伏连接器的外壳并非简单的塑料,而是需要经过精心选择的材料,以满足以下要求: 耐候性:光伏

学习RV32GC对比X86-32指令集的优势思考

。

X86-32 :

指令长度不固定,包括多种不同的指令格式,这增加了指令解码的复杂性。

指令解码部件在低端实现中偏昂贵,在中高端处理器设计中容易带来性能挑战。

寄存器数量与操作

RV32GC

发表于 10-31 21:47

SOC芯片设计的挑战与解决方案

设计复杂性 挑战: 随着技术的发展,SOC集成的组件越来越多,设计复杂性也随之增加,这导致了设计周期的延长和成本的增加。 解决方案: 模块化设计: 将SOC分解为可重用的模块,可以简

不需要点表的工业智能网关的卓越功能:精准 PLC 协议解析与可靠数据采集及远程维护

需要点表的先进工业智能网关以其精准的 PLC 协议解析、可靠的数据采集和强大的远程维护功能,为工业自动化领域带来了全新的发展机遇。它不仅提高了工业生产的效率和质量,降低了系统的复杂性和维护成本,还为工业智能化的进一步发展奠定

【⌈嵌入式机电一体化系统设计与实现⌋阅读体验】+磁力输送机系统设计的创新与挑战

传感器和三相电源控制,实现了输送机小车的精准推进,展示了先进的直线驱动技术在物料搬运中的应用潜力。

简化电路设计 :通过优化的电路设计和逻辑门控制,实现了对空心直线电机的高效换向控制,降低了

发表于 09-14 22:44

ARM MCU嵌入式开发 | 基于国产GD32F10x芯片+嵌入的开始

嵌人式系统的分类方法是依照系统主控制芯片的复杂性进行分类。可以分为型嵌入式系统、中等规模嵌入式系统、复杂

发表于 09-09 14:48

FPGA设计面临的挑战和解决方案

设计可靠的可编程逻辑门阵列(FPGA)对于不容故障的系统来说是一项具有挑战性的任务。本文介绍FPGA设计的复杂性,重点关注如何在提高可靠性的同时管理随之带来的功耗增加、设计

CISC(复杂指令集)与RISC(精简指令集)的区别

, B; STR A

DDRA, A。这种架构可以降低CPU的复杂性以及允许在同样的工艺水平下生产出功能更强大的CPU,但对于编译器的设计

有更高的要求。

CISC(Complex

发表于 07-30 17:21

硬件工程师在可靠性设计中所面临的挑战及解决之道

Course硬件电路可靠性设计HardwareEngineer硬件电路工程师在进行可靠性设计时,常常会陷入一系列烦恼之中。这些挑战包括成本、时间压力、可靠性预测的不确定性、

AD400x解决了设计挑战并降低了系统复杂性

AD400x解决了设计挑战并降低了系统复杂性

评论