- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:59fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx

+关注

关注

71文章

2172浏览量

122472 -

Vivado

+关注

关注

19文章

816浏览量

67034

发布评论请先 登录

相关推荐

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

•0次下载

使用HLS流程设计和验证图像信号处理设备

STMicroelectronics成像部门负责向消费者、工业、安全和汽车市场提供创新的成像技术和产品。该团队精心制定了一套通过模板实现的High-Level Synthesis(HLS)高层次综合流程,使得上述产品能够迅速上市。对于汽车市场,该流程符合ISO 26262

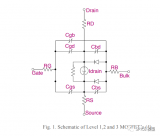

从Level1 Model到Level3 Modle来感受器件模型是如何开发的

本文从Level1 model到Level3 model的Ids电流公式的发展来感受Compact器件模型是如何开发的。 MOS技术扩展到纳米尺寸,带来了电路模拟器中器件模型的发展

求助,ISO7721用于485隔离遇到的疑问求解

我想选用ISO7721用于485隔离,遇到带你问题,请帮忙看看。

①看到PDF上描述IIH(High-level input current)最大到10uA,但是MCU SCI TX引脚输出一般

发表于 12-18 06:30

Xilinx_Vivado_SDK的安装教程

I Agree,然后点击 Next: 选择 Vivado HL System Edition(一般选择这个设计套件比较完整,它比 Vivado HL Design Edition 多了一个 System Generator for DSP with Mat

每次Vivado编译的结果都一样吗

很多FPGA工程师都有这种困惑,Vivado每次编译的结果都一样吗? 在AMD官网上,有这样一个帖子: Are Vivado results repeatable for identical

Vivado使用小技巧

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

Vivado编辑器乱码问题

,但是在Vivado里面打开用sublime写的代码之后,经常出现中文乱码,让人很不舒服。究其原因就是一般来说第三方的编辑器是采用utf8的编码方式,而vivado的text editor不是这种方式。

如何让使用JCOM写入的Overcurrent Trip Level是有效的?

我们使用IMC300的JCOM修改MCE的CompRef暂存器数值, 该暂存器为Overcurrent Trip Level,但是实验后并未得到预期的效果.

经量测马达运转电流约为2A。为了测试

发表于 08-01 08:12

esp32c3运行examples/wifi/getting_started/softAP例子,设置密码后WIFI标志上显示一个叉,为什么?

运行examples/wifi/getting_started/softAP例子,发现如果不设置密码可以正常连上,但设置密码后WIFI标志上显示一个叉,输入密码后无法连接

发表于 06-06 06:42

STM8S103 LOW_LEVEL_H; LOW_LEVEL_L时间是怎么计算的?

(void)

{

if(CC1IF_LOW)//检测到下降沿

{

LOW_LEVEL_H=TIM2_CCR2H;

LOW_LEVEL_L=TIM2_CCR2L;

CC1IF_LOW=0

发表于 04-25 06:24

在Vivado Synthesis中怎么使用SystemVerilog接口连接逻辑呢?

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

评论