- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:11fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3519浏览量

106342 -

ADI

+关注

关注

146文章

45866浏览量

252692 -

RF

+关注

关注

65文章

3060浏览量

167529 -

AD9361

+关注

关注

8文章

35浏览量

37286

发布评论请先 登录

相关推荐

光纤收发器与IO-Link收发器的区别

在工业自动化和通信领域,光纤收发器和IO-Link收发器都是关键的通信组件,它们在数据传输、网络扩展和设备连接方面发挥着重要作用。然而,两者在设计、功能、应用场景以及技术特性上存在显著差异。本文将

无线收发器工作原理,无线收发器怎么使用

无线收发器作为现代通信技术的重要组成部分,广泛应用于各个领域,包括无线通信、物联网、远程控制和无线传感器网络等。本文将深入探讨无线收发器的工作原理,同时提供详细的使用方法。

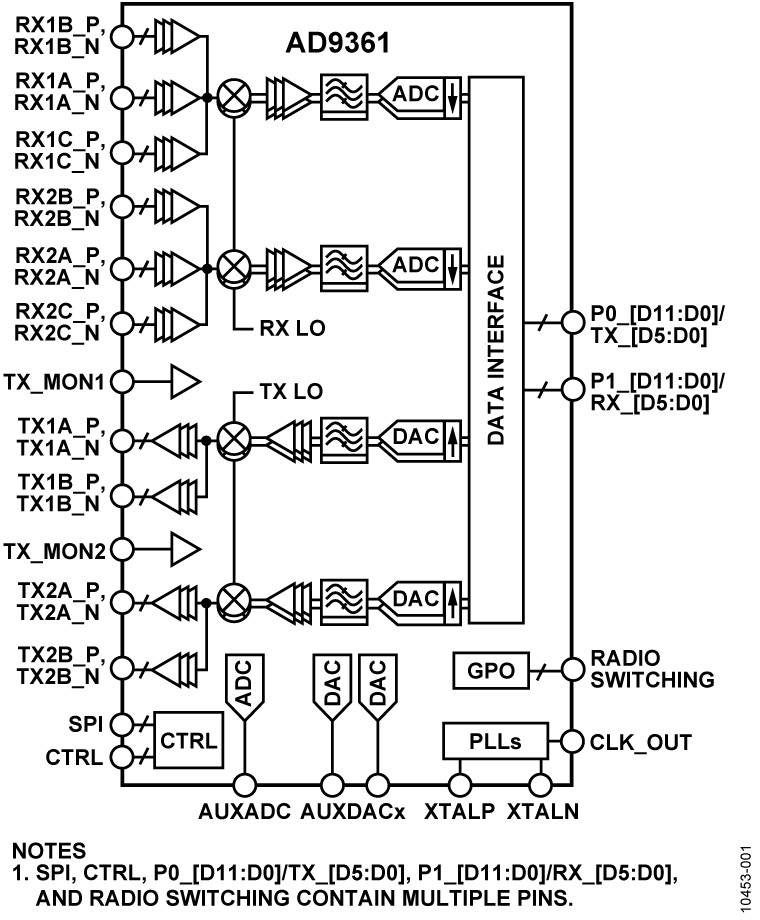

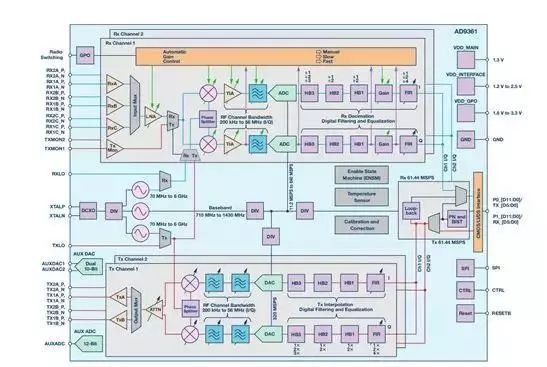

AD9361 RF捷变收发器,评估套件和开发资源

AD9361 *附件:AD9361_cn 中文数据手册.pdf 是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver™捷

AD936x RF收发器应用相关问答

AD9361是一款针对各种低功耗无线应用而设计的RF收发器,集RF前端与灵活的混合信号基带部分为一体,集成频率合成器,为处理器提供可配置数字

射频收发器就是基带吗

射频收发器(RF Transceiver)和基带(Baseband)是无线通信系统中两个不同的概念,它们在功能和设计上有所区别。射频收发器主要负责无线信号的发送和接收,而基带则处理信号的数字处理部分

射频收发器属于什么类别

射频收发器(RF Transceiver)是无线通信系统中的关键组件,它负责将数字信号转换为无线电波(发射)以及将无线电波转换为数字信号(接收)。射频收发器的设计和应用非常广泛,包括但不限于移动通信

光纤收发器怎么判断好坏

光纤收发器作为光纤通信系统中的关键设备,其性能直接影响到整个网络的传输质量和稳定性。因此,准确判断光纤收发器的好坏是确保网络正常运行的重要步骤。以下是从多个方面综合评估光纤收发器好坏的详细方法,旨在为读者提供全面而深入的指导。

光纤收发器pwr是什么意思

光纤收发器是一种将电信号转换为光信号或将光信号转换为电信号的设备,广泛应用于通信、网络、监控等领域。在光纤收发器的参数中,PWR是一个非常重要的指标,它代表了光纤收发器的功耗。 PWR的含义 PWR

光纤收发器的作用、使用方法及应用

光纤收发器是一种将电信号转换为光信号或将光信号转换为电信号的设备,广泛应用于通信网络中。以下是光纤收发器的介绍: 光纤收发器的作用 光纤收发器的主要作用是实现电信号与光信号之间的转换。

收发器的主要作用与种类详解

收发器,作为通信系统中的关键组成部分,其主要作用是实现信号的发送和接收。随着通信技术的不断发展,收发器的种类也日益丰富,满足了不同场景下的通信需求。本文将对收发器的主要作用和种类进行详细介绍,旨在帮助读者更好地理解和应用

AD9361和AD9371里接收机的性能有哪些不同呢?

话说,如果使用CMOS工艺的话,零中频的闪烁噪声会比较大,如果使用SiGe和BiCMOS工艺的话,闪烁噪声就会小很多[1]。所以,我就打算看看AD9361和AD9371这两个芯片的工艺。

AD9361 BBPLL锁相环失锁(Z706)

各位好! 我在尝试用FPGA直接配置AD9361,但是BBPLL一直失锁,具体问题如下:

这是9361配置表,在9361初始化时,index一直卡在24,说明BBPLL失锁,观察spi读写

可以看到sdi值一直为0,sdo波形也

发表于 03-25 16:14

怎么区分单模多模光纤收发器

在光纤通信系统中,单模光纤收发器和多模光纤收发器是两种不同的设备,它们的工作原理和特点有所不同。为了区分单模多模光纤收发器,可以从以下几个方面进行区分: 光纤类型:单模光纤收发器和多模

AD9361 RF 捷变收发器

AD9361 RF 捷变收发器

评论