大量设备都使用数/模转换器(DAC)来实现各种各样的功能。高精度、电压输出DAC的常见应用有仪器仪表、自动测试以及测试/测量设备。在这些应用中,DAC产生直流电压或任意波形。

对于这些电路,使用电压输出DAC进行设计的最具挑战的部分就是真实了解这种怪兽在其规定精度范围之内到底能够跑多快。如果某款设备的时钟频率为50MHz,那么就电压输出更新速度来说,这意味着什么?或者,除了知道时钟频率之外,还需要更多信息吗?

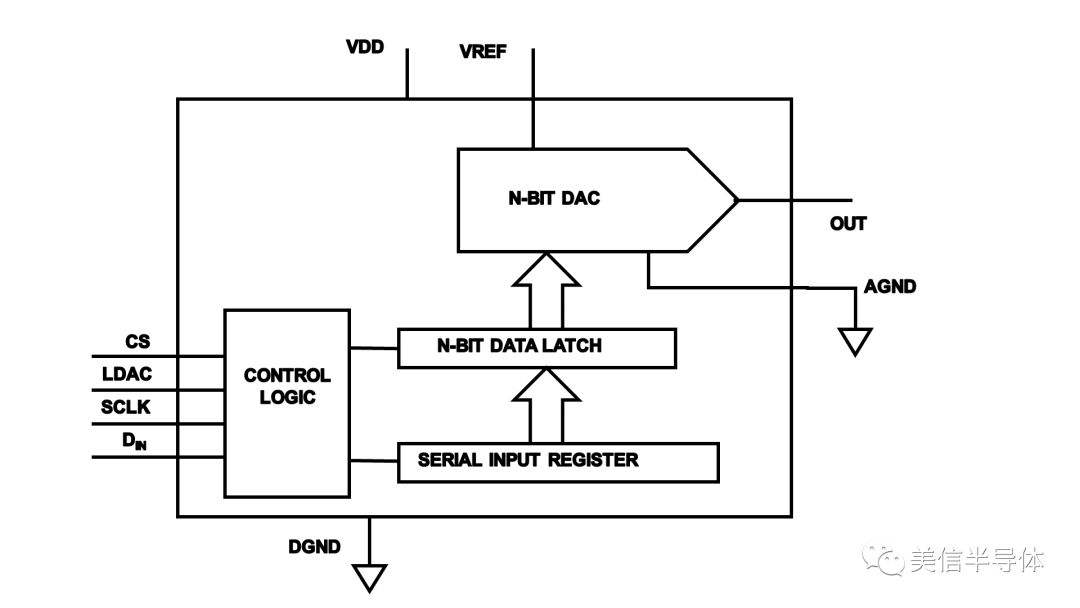

电压输出DAC采用FIFO方式,也就是先进先出(图1)。通常情况下,用户将DAC的输入数字数据(DIN)装载到DAC内部串行输入寄存器,而将之前的数据编码锁存到N位DAC。

图1. 高精度、电压输出DAC的通用方框图

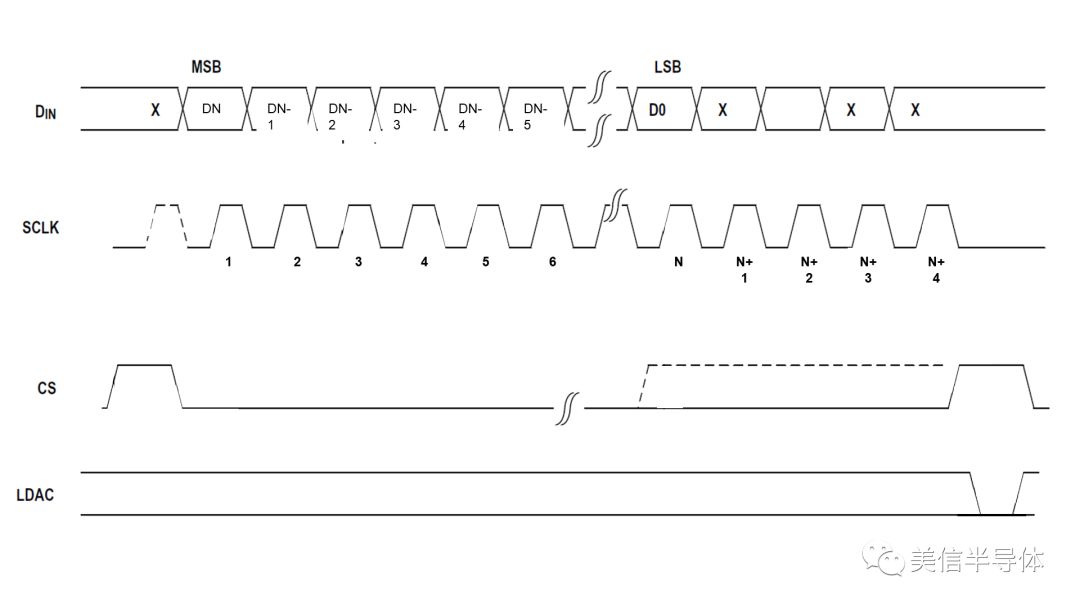

LDAC(装载DAC)引脚为高电平时,串行数据流与SCLK(串行时钟)配合,装载DAC的串行输入寄存器(图2)。输入寄存器填满之后,LDAC低电平则将串行输入寄存器装载到N位数据锁存器。LDAC再次变为高电平,模拟输出电压通过OUT引脚输出并稳定到最终值。在建立时间期间,串行输入寄存器接收下一个编码。

图2. 高精度、电压输出DAC的通用时序图

理想情况下,DAC的理论吞吐速度等于SCLK/N,其中SCLK为外部时钟速率,N为DAC的位数。例如,对于16位DAC,最大时钟速率为50MHz,吞吐率为50MHz/16,即3.125MHz。

这是很了不起的DAC吞吐率!然而,这是非常不现实的,特别是如果您将模拟输出电压设置为满幅或满摆幅输出。在这种情况下,您需要时间使输出稳定到其满幅值。

建立时间决定一切

所以,我们还是回到现实吧。高精度应用中的建立时间决定DAC的有效更新率,而不取决于时钟的数据率。DAC的模拟输出频率结构通常是一阶的。对于较大的信号,很容易利用R/C电路建立这种响应的模型。对于这种电路,可用以下公式描述模拟输入/输出行为。

VOUT = VIN(1 – e-t/RC) 式1

式中:

VOUT➔模拟输出电压

VIN➔模拟输入电压

R ➔DAC输出电阻

C ➔ DAC输出电容

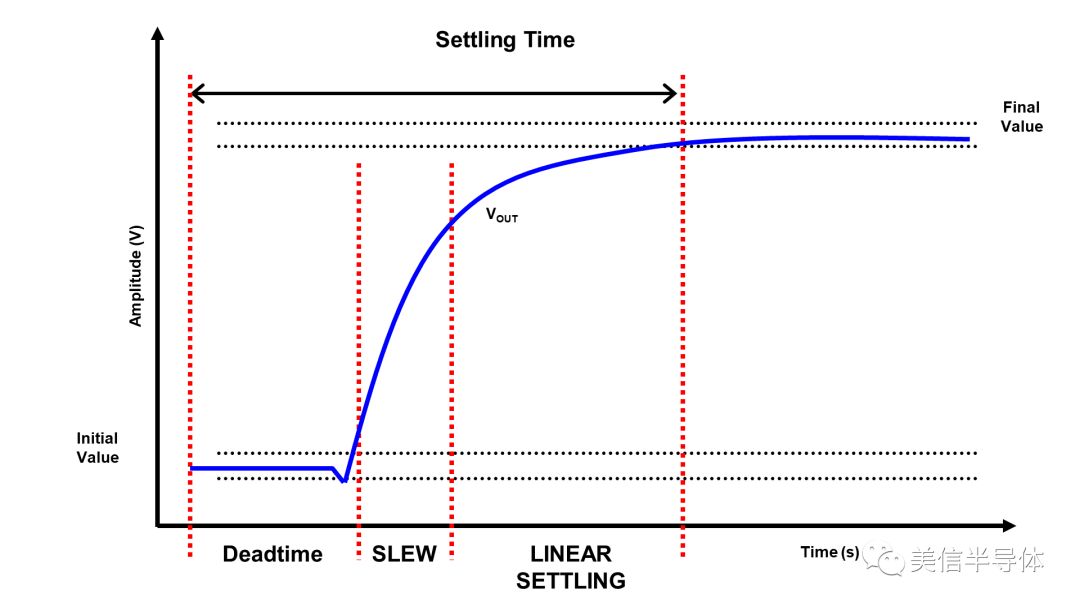

图3所示为DAC系统的模拟信号建立时间响应,包括死区时间、摆动及线性建立部分。

图3. DAC的理论输出建立时间

死区时间是DAC使用数据锁存寄存器更新模拟输出的时间。如果发生较大的模拟输入阶跃,DAC将进入摆动区。在该信号响应结束时,最终值为理论最终值的±1/2 LSB。

DAC的数据手册会列出建立时间指标。以MAX5717 16位、50MHz、电压输出DAC为例,建立时间为0.75us。初看之下,会以为DAC的吞吐率为50MHz除以16,即2.33MHz。如果您将DAC的建立时间考虑在内,该DAC的实际吞吐率为建立时间的倒数,即1.33MHz。

重要的工作优先

大量使用DAC的设备都要求DAC行为实现最优化,这取决于系统要求。对于仪器仪表、自动测试和测试/测量应用,吞吐率是主要技术指标。DAC精度性能的细节非常重要,但切记建立时间是使您能够立即洞察DAC速度是否足够满足电路的最佳指标。

-

寄存器

+关注

关注

31文章

5619浏览量

130409 -

dac

+关注

关注

44文章

2856浏览量

197603

原文标题:Maxim设计指南 | 找到最优的建立时间

文章出处:【微信号:Maxim_Integrated,微信公众号:美信半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于双12位DAC的高精度直流电压/电流源设计

基于MSP430F149_DAC7811的数控直流电压源程序

示波器如何测量直流电压?

DAC产生直流电压或任意波形

DAC产生直流电压或任意波形

评论